#### Washington University in St. Louis

#### Washington University Open Scholarship

All Computer Science and Engineering Research

Computer Science and Engineering

Report Number: WUCSE-2002-17

2002-05-03

### Design and Performance of Scalable High-Performance Programmable Routers - Doctoral Dissertation, August 2002

Tilman Wolf

The flexibility to adapt to new services and protocols without changes in the underlying hardware is and will increasingly be a key requirement for advanced networks. Introducing a processing component into the data path of routers and implementing packet processing in software provides this ability. In such a programmable router, a powerful processing infrastructure is necessary to achieve to level of performance that is comparable to custom silicon-based routers and to demonstrate the feasibility of this approach. This work aims at the general design of such programmable routers and, specifically, at the design and performance analysis of the processing... Read complete abstract on page 2.

Follow this and additional works at: https://openscholarship.wustl.edu/cse\_research

#### **Recommended Citation**

Wolf, Tilman, "Design and Performance of Scalable High-Performance Programmable Routers - Doctoral Dissertation, August 2002" Report Number: WUCSE-2002-17 (2002). *All Computer Science and Engineering Research.*

https://openscholarship.wustl.edu/cse\_research/1135

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160.

This technical report is available at Washington University Open Scholarship: https://openscholarship.wustl.edu/cse\_research/1135

# Design and Performance of Scalable High-Performance Programmable Routers - Doctoral Dissertation, August 2002

Tilman Wolf

#### **Complete Abstract:**

The flexibility to adapt to new services and protocols without changes in the underlying hardware is and will increasingly be a key requirement for advanced networks. Introducing a processing component into the data path of routers and implementing packet processing in software provides this ability. In such a programmable router, a powerful processing infrastructure is necessary to achieve to level of performance that is comparable to custom silicon-based routers and to demonstrate the feasibility of this approach. This work aims at the general design of such programmable routers and, specifically, at the design and performance analysis of the processing subsystem. The necessity of programmable routers is motivated, and a router design is proposed. Based on the design, a general performance model is developed and quantitatively evaluated using a new network processor benchmark. Operational challenges, like scheduling of packets to processing engines, are addressed, and novel algorithms are presented. The results of this work give qualitative and quantitative insights into this new domain that combines issues from networking, computer architecture, and system design.

# SEVER INSTITUTE OF TECHNOLOGY DOCTOR OF SCIENCE DEGREE

#### DISSERTATION ACCEPTANCE

(To be the first page of each copy of the dissertation)

DATE: May 3, 2002

STUDENT'S NAME: Tilman Wolf

This student's dissertation, entitled *Design and Performance of Scalable High-Performance Programmable Routers* has been examined by the undersigned committee of five faculty members and has received full approval for acceptance in partial fulfillment of the requirements for the degree Doctor of Science.

| APPROVAL: |  | Chairman |

|-----------|--|----------|

|           |  |          |

|           |  |          |

|           |  |          |

|           |  |          |

|           |  | •        |

|           |  |          |

# WASHINGTON UNIVERSITY SEVER INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE

# DESIGN AND PERFORMANCE OF SCALABLE HIGH-PERFORMANCE PROGRAMMABLE ROUTERS

by

Tilman Wolf, M.S.

Prepared under the direction of Professor Jonathan S. Turner

A dissertation presented to the Sever Institute of Washington University in partial fulfillment of the requirements for the degree of

Doctor of Science

August, 2002

Saint Louis, Missouri

Short Title: Design of Programmable Routers Wolf, D.Sc. 2002

# WASHINGTON UNIVERSITY SEVER INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE

ABSTRACT

# DESIGN AND PERFORMANCE OF SCALABLE HIGH-PERFORMANCE PROGRAMMABLE ROUTERS

by Tilman Wolf

ADVISOR: Professor Jonathan S. Turner

August, 2002 Saint Louis, Missouri

The flexibility to adapt to new services and protocols without changes in the underlying hardware is and will increasingly be a key requirement for advanced networks. Introducing a processing component into the data path of routers and implementing packet processing in software provides this ability. In such a programmable router, a powerful processing infrastructure is necessary to achieve a level of performance that is comparable to custom silicon-based routers and to demonstrate the feasibility of this approach. This work aims at the general design of such programmable routers and, specifically, at the design and performance analysis of the processing subsystem. The necessity of programmable routers is motivated, and a router design is proposed. Based on the design, a general performance model is developed and quantitatively evaluated using a new network processor benchmark. Operational challenges, like scheduling of packets to processing engines, are addressed, and novel algorithms are presented. The results of this work give qualitative and quantitative insights into this new domain that combines issues from networking, computer architecture, and system design.

copyright by Tilman Wolf 2002

# Contents

| Li       | List of Tables             |        |                                     |     |  |  |

|----------|----------------------------|--------|-------------------------------------|-----|--|--|

| Li       | st of                      | Figur  | es                                  | ix  |  |  |

| A        | cknov                      | wledgr | ${f ments}$                         | xi  |  |  |

| Pr       | efac                       | е      |                                     | xii |  |  |

| 1        | Intr                       | oduct  | ion                                 | 1   |  |  |

|          | 1.1                        | Trend  | s in Networking                     | 2   |  |  |

|          | 1.2                        | Progra | ammable Networks                    | 3   |  |  |

|          | 1.3                        | Techn  | ology Challenges and Opportunities  | 5   |  |  |

|          | 1.4                        | Progra | ammable Router Design               | 6   |  |  |

|          | 1.5                        | Organ  | nization of Dissertation            | 7   |  |  |

| <b>2</b> | Programmable Router Design |        |                                     |     |  |  |

|          | 2.1                        | Softwa | are-Based Programmable Routers      | 9   |  |  |

|          |                            | 2.1.1  | Active Network Node                 | 10  |  |  |

|          |                            | 2.1.2  | Active Applications                 | 11  |  |  |

|          |                            | 2.1.3  | Performance Issues                  | 13  |  |  |

|          | 2.2                        | High-  | Performance Programmable Routers    | 14  |  |  |

|          |                            | 2.2.1  | Parallelism in Networking Workloads | 14  |  |  |

|          |                            | 2.2.2  | Programmable Router Design          | 15  |  |  |

|          | 2.3                        | Proces | ssing System                        | 21  |  |  |

|          |                            | 2.3.1  | Processor Architectures             | 21  |  |  |

|          |                            | 2.3.2  | Memory System                       | 26  |  |  |

|          |                            | 2.3.3  | I/O System                          | 26  |  |  |

|          |                            | 2.3.4  | Configurations                      | 27  |  |  |

|   | 2.4 | Scalab       | ility                               | 28 |  |  |  |

|---|-----|--------------|-------------------------------------|----|--|--|--|

|   |     | 2.4.1        | APC Design Scalability              | 28 |  |  |  |

|   |     | 2.4.2        | Technology Scaling                  | 29 |  |  |  |

|   | 2.5 | Relate       | ed Work                             | 35 |  |  |  |

|   |     | 2.5.1        | Programmable Routers                | 35 |  |  |  |

|   |     | 2.5.2        | Network Processors                  | 37 |  |  |  |

|   | 2.6 | Summ         | ary 3                               | 38 |  |  |  |

| 3 | Wo  | rkload       | Characterization                    | 10 |  |  |  |

|   | 3.1 |              |                                     | 10 |  |  |  |

|   |     | 3.1.1        |                                     | 11 |  |  |  |

|   |     | 3.1.2        |                                     | 12 |  |  |  |

|   | 3.2 | Measu        |                                     | 13 |  |  |  |

|   |     | 3.2.1        |                                     | 13 |  |  |  |

|   |     | 3.2.2        | Code and Computational Kernel Sizes | 14 |  |  |  |

|   |     | 3.2.3        | Computational Complexity            | 16 |  |  |  |

|   |     | 3.2.4        | Instruction Set Characteristics     | 16 |  |  |  |

|   |     | 3.2.5        | Memory Hierarchy Characteristics    | 19 |  |  |  |

|   |     | 3.2.6        | Summary of Characteristics          | 52 |  |  |  |

|   | 3.3 | Comp         | arison to SPEC                      | 52 |  |  |  |

|   | 3.4 | Archit       | sectural Implications               | 53 |  |  |  |

|   | 3.5 | Related Work |                                     |    |  |  |  |

|   | 3.6 | Summ         | ary                                 | 56 |  |  |  |

| 4 | Per | formaı       | nce Model                           | 57 |  |  |  |

|   | 4.1 | Analy        | tic Model                           | 57 |  |  |  |

|   |     | 4.1.1        |                                     | 30 |  |  |  |

|   |     | 4.1.2        | Chip Area                           | 30 |  |  |  |

|   |     | 4.1.3        | Memory System                       | 31 |  |  |  |

|   |     | 4.1.4        | Memory and I/O Channels             | 35 |  |  |  |

|   |     | 4.1.5        | Optimization                        | 66 |  |  |  |

|   | 4.2 | Workl        | oad and System Characteristics      | 37 |  |  |  |

|   |     | 4.2.1        | Network Processor Workload          | 67 |  |  |  |

|   |     | 4.2.2        | System Parameters                   | 37 |  |  |  |

|   | 4.3 | Design       | n Results                           | 38 |  |  |  |

|   |     | 431          | Optimal Configuration               | 38 |  |  |  |

|   |     | 4.3.2  | Performance Trends                   | 70  |

|---|-----|--------|--------------------------------------|-----|

|   |     | 4.3.3  | Sensitivity of Results               | 76  |

|   |     | 4.3.4  | Summary of Results                   | 78  |

|   |     | 4.3.5  | Impact on Programmable Router Design | 78  |

|   | 4.4 | Relate | ed Work                              | 79  |

|   | 4.5 | Summ   | nary                                 | 79  |

| 5 | Pro | cessor | Scheduling Algorithms                | 80  |

|   | 5.1 | Sched  | uling Problem                        | 30  |

|   | 5.2 | Proces | ssing Characteristics                | 31  |

|   |     | 5.2.1  | Predictability of Processing Times   | 32  |

|   |     | 5.2.2  | Cold Cache Penalty                   | 34  |

|   |     | 5.2.3  | Reservations                         | 36  |

|   | 5.3 | Locali | ty-Aware Predictive Scheduling       | 37  |

|   |     | 5.3.1  | Scheduling Algorithm                 | 37  |

|   |     | 5.3.2  | Evaluation                           | 90  |

|   | 5.4 | Estim  | ation-Based Fair Queuing             | 97  |

|   |     | 5.4.1  | Scheduling Algorithm                 | 98  |

|   |     | 5.4.2  | Evaluation                           | )5  |

|   | 5.5 | Comb   | ination of LAP and EFQ               | )9  |

|   | 5.6 | Relate | ed Work                              | )9  |

|   | 5.7 | Summ   | nary                                 | . 1 |

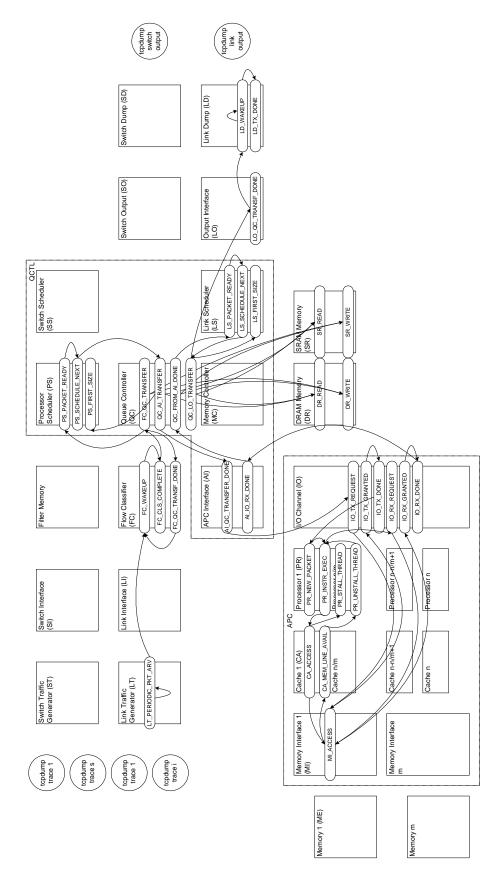

| 6 | Sys | tem Si | mulation                             | .2  |

|   | 6.1 | Introd | luction                              | 2   |

|   | 6.2 | Syster | m Simulation                         | 4   |

|   |     | 6.2.1  | Data Path                            | 4   |

|   |     | 6.2.2  | Control Path                         | .5  |

|   |     | 6.2.3  | Processing Engine Simulation         | .5  |

|   |     | 6.2.4  | Queuing System                       | 9   |

|   |     | 6.2.5  | Schedulers                           | 21  |

|   |     | 6.2.6  | Programming Environment              | 21  |

|   |     | 6.2.7  | Simulation Summary                   | 23  |

|   | 6.3 | Simula | ation Results                        | 23  |

|   |     | 6.3.1  | Workload and Configuration           | 23  |

|   |     | 6.3.2  | Comparison                           | 25  |

|              |       | 6.3.3 Error Trends    |

|--------------|-------|-----------------------|

|              | 6.4   | Summary               |

| 7            | Sun   | nmary and Future Work |

|              | 7.1   | Summary               |

|              | 7.2   | Future Work           |

| $\mathbf{R}$ | efere | nces                  |

| $\mathbf{V}$ | ita . |                       |

# List of Tables

| 2.1 | Technology Growth Parameters                        | 33 |

|-----|-----------------------------------------------------|----|

| 2.2 | Processing Engine Scalability                       | 36 |

| 3.1 | CommBench Applications                              | 41 |

| 3.2 | Code Size for CommBench                             | 44 |

| 3.3 | Dynamic Kernel Size for CommBench                   | 45 |

| 3.4 | Computational Complexity of CommBench Applications  | 47 |

| 3.5 | Ordered Instruction Frequencies for CommBench       | 49 |

| 3.6 | Effects of Cache Line Size on Miss Rates            | 51 |

| 3.7 | SPEC Code Size                                      | 52 |

| 3.8 | SPEC Kernel Size                                    | 53 |

| 4.1 | Performance Model Parameters                        | 59 |

| 4.2 | Aggregate Workload Parameters                       | 67 |

| 4.3 | System Parameters                                   | 69 |

| 4.4 | Optimal System Configurations                       | 71 |

| 4.5 | Sensitivity of Results                              | 77 |

| 5.1 | Packet Processing Parameters                        | 84 |

| 5.2 | System Parameters                                   | 88 |

| 6.1 | Comparison of Analytic Model and Simulation Results | 27 |

# List of Figures

| 1.1  | Network Services Requiring Programmability           | 4  |

|------|------------------------------------------------------|----|

| 1.2  | Technology Growth Trends                             | 6  |

| 2.1  | Active Network Node                                  | 11 |

| 2.2  | Parallelism in Networking Workloads                  | 15 |

| 2.3  | System Organization of Programmable Router           | 17 |

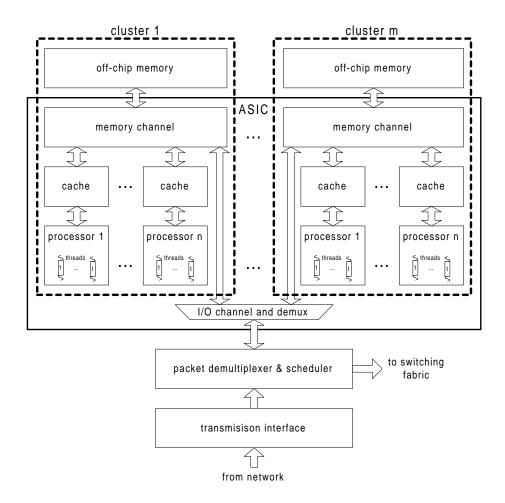

| 2.4  | Router Port Design                                   | 18 |

| 2.5  | Processor Performance in Relation to Complexity      | 23 |

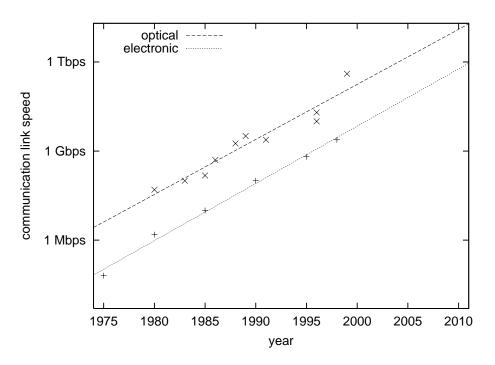

| 2.6  | Growth of Communication Link Speed                   | 30 |

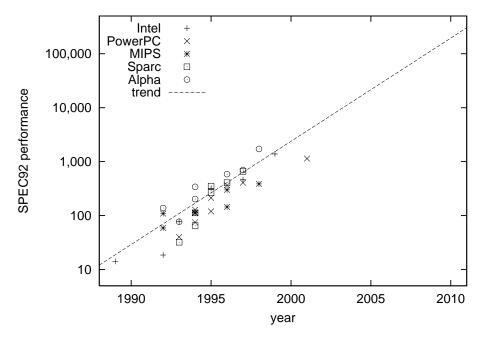

| 2.7  | Growth of Processor SPEC Performance                 | 31 |

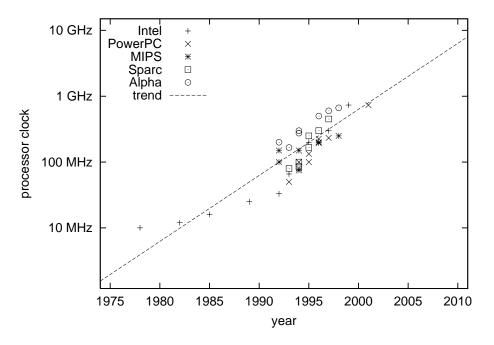

| 2.8  | Growth of Processor Clock Rate                       | 31 |

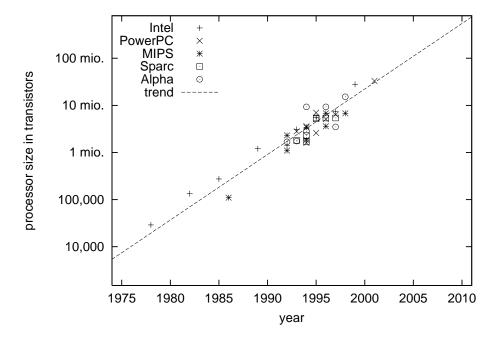

| 2.9  | Growth of Processor Size                             | 32 |

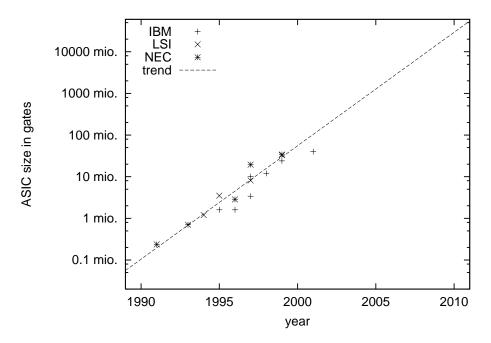

| 2.10 | Growth of Application-Specific Integrated Circuits   | 33 |

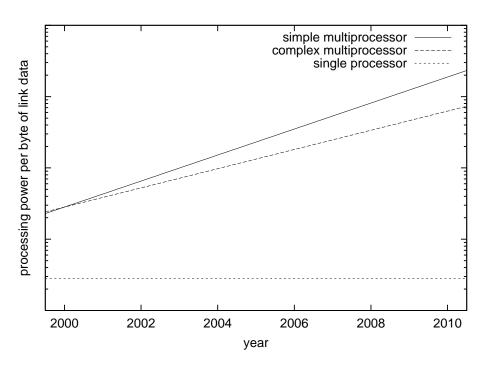

| 2.11 | Processing Power per Byte of Link Data               | 35 |

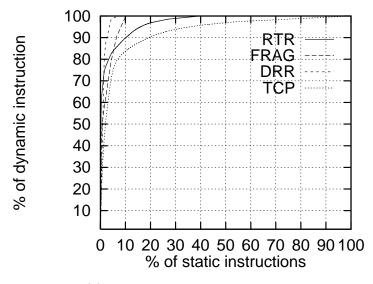

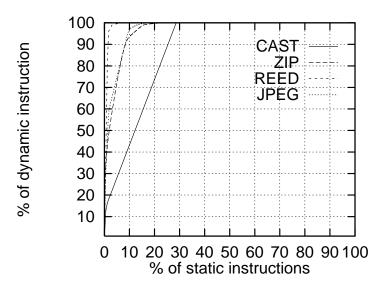

| 3.1  | Locality in CommBench Applications                   | 47 |

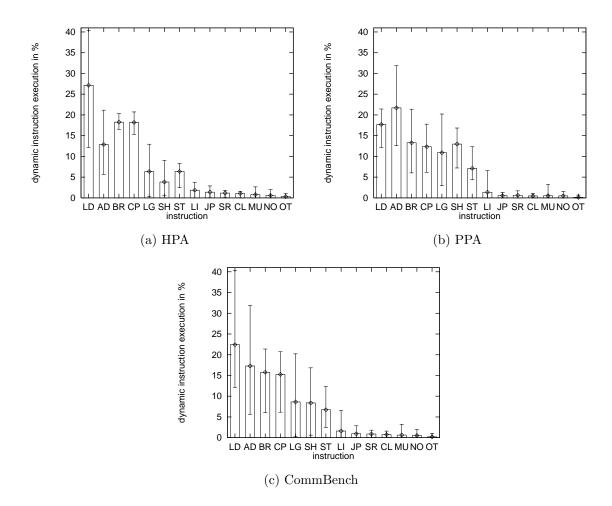

| 3.2  | Instruction Mix for CommBench                        | 48 |

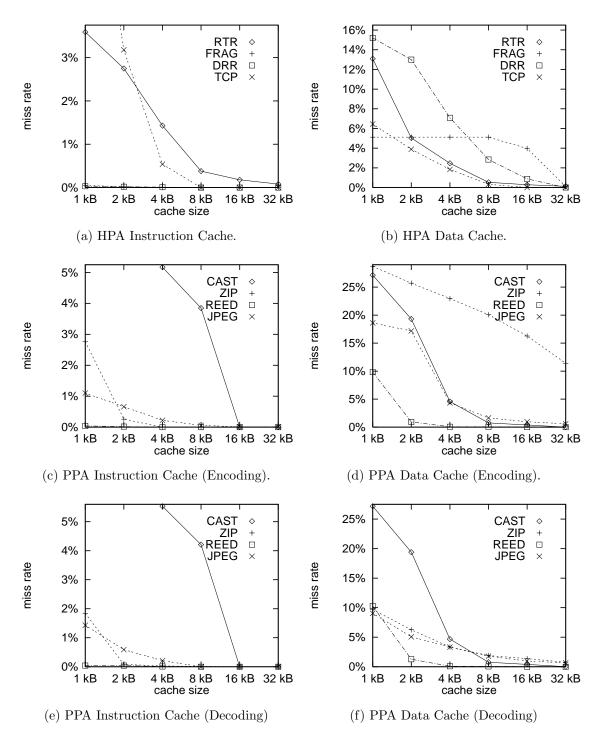

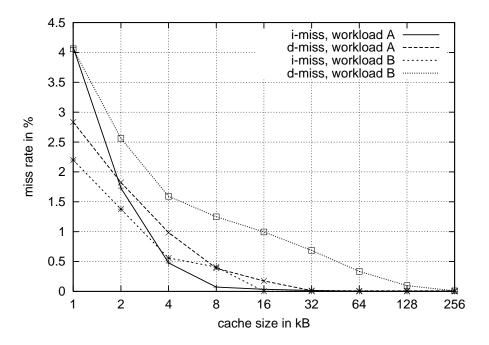

| 3.3  | Cache Miss Rates for CommBench Applications          | 50 |

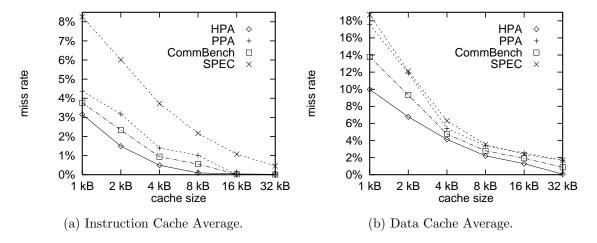

| 3.4  | Average Cache Miss Rates                             | 51 |

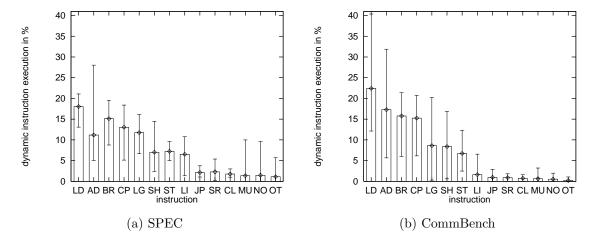

| 3.5  | SPEC and CommBench Instruction Frequencies           | 54 |

| 4.1  | Network Processor Architecture for Performance Model | 58 |

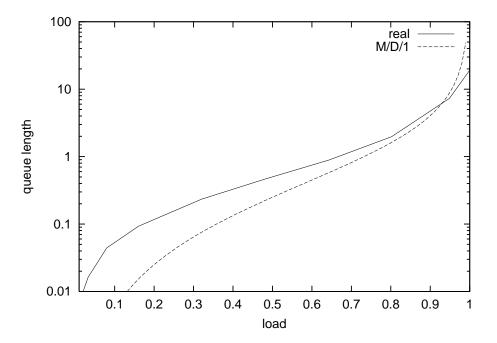

| 4.2  | Queue Length for Memory Channel                      | 64 |

| 4.3  | Aggregate Cache Miss Rates                           | 68 |

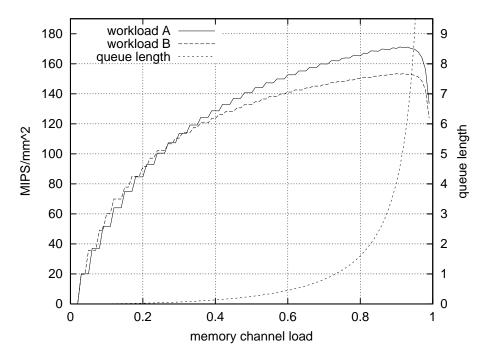

| 4.4  | Performance vs. Memory Channel Load                  | 71 |

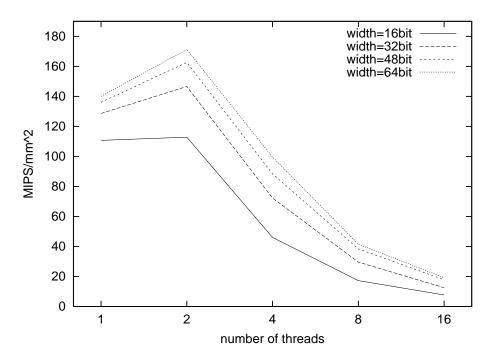

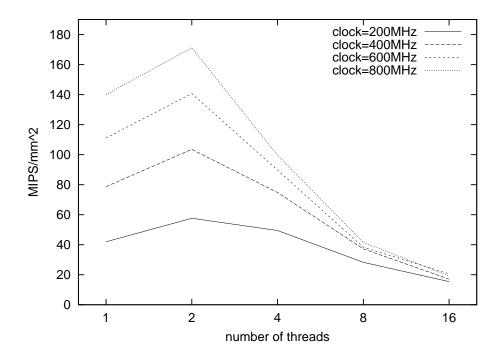

| 4.5  | Performance vs. Memory Channel Width                 | 72 |

| 4.6  | Performance vs. Processor Clock Rate                 | 73 |

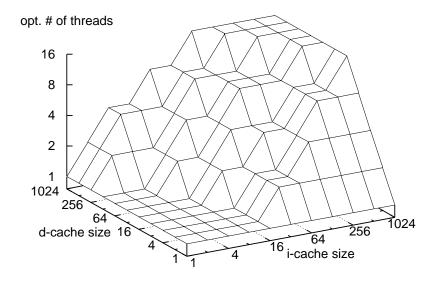

| 4.7  | Optimal Number of Threads                            | 73 |

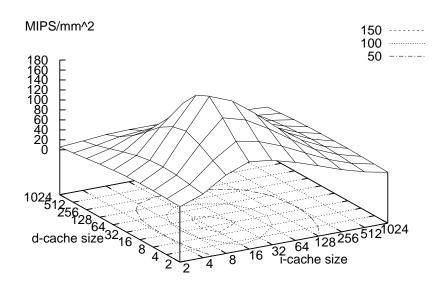

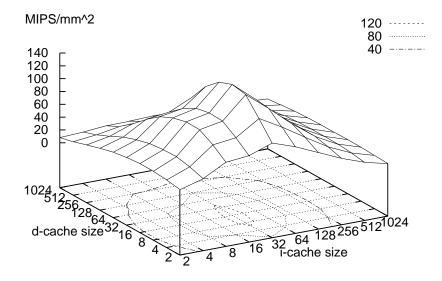

| 4.8  | Performance vs. Cache Sizes (Workload A)               | 74  |

|------|--------------------------------------------------------|-----|

| 4.9  | Performance vs. Cache Sizes (Workload B)               | 74  |

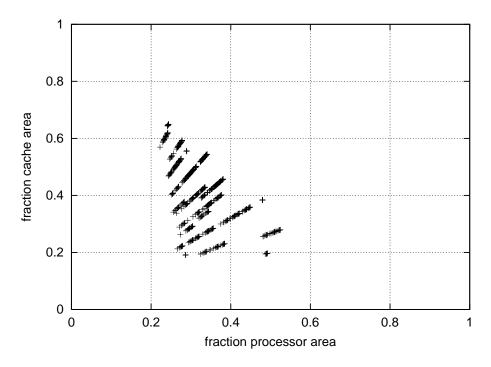

| 4.10 | Chip Area Usage                                        | 76  |

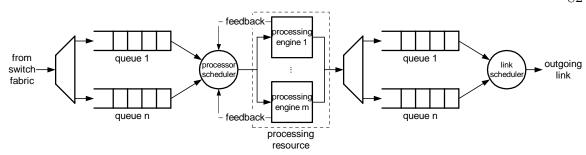

| 5.1  | Scheduler System Outline                               | 82  |

| 5.2  | Packet Processing Time Approximation                   | 83  |

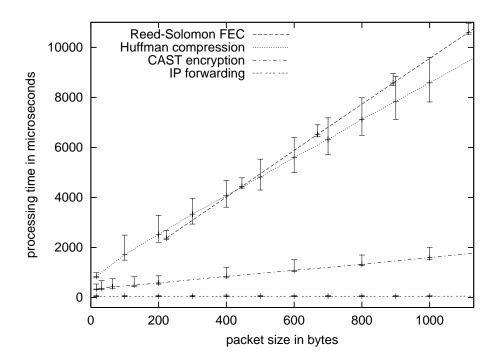

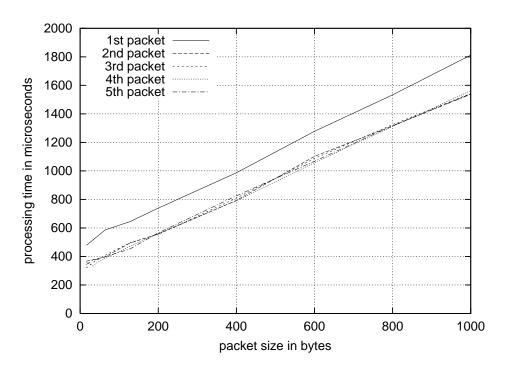

| 5.3  | Cold Cache Penalty                                     | 85  |

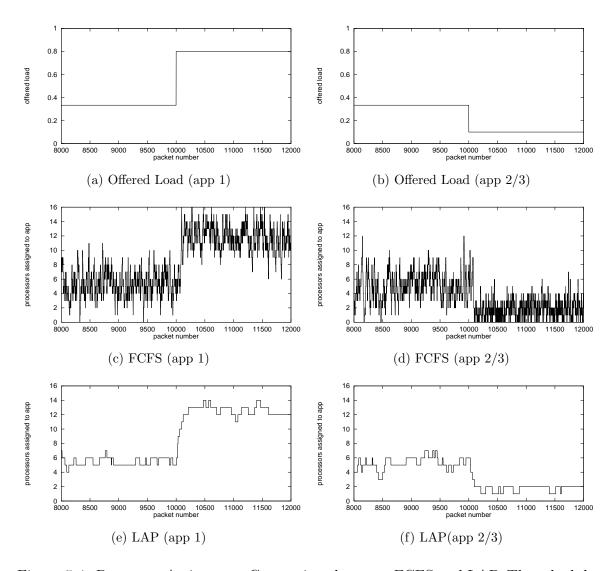

| 5.4  | Processor Assignment Comparison between FCFS and LAP   | 93  |

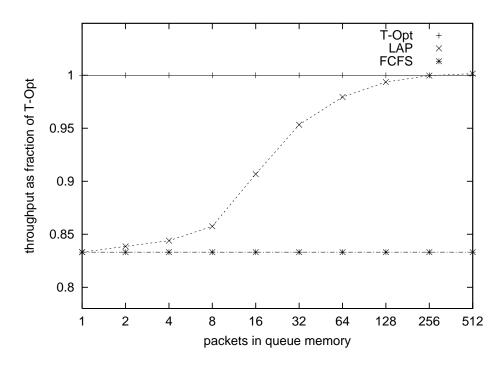

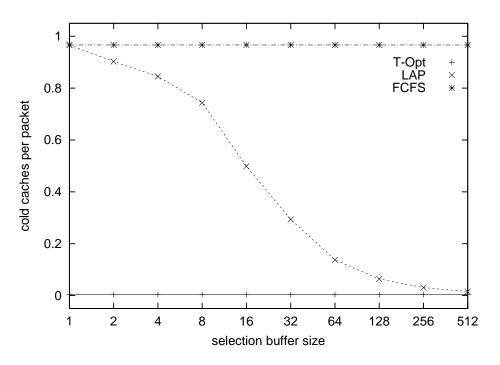

| 5.5  | Throughput of Different Scheduling Algorithms          | 94  |

| 5.6  | Cold Cache Fraction                                    | 95  |

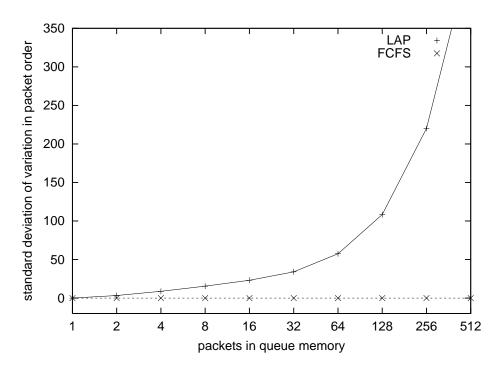

| 5.7  | Delay Variation                                        | 96  |

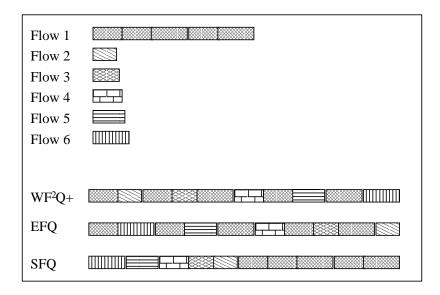

| 5.8  | EFQ Scheduling Example                                 | 102 |

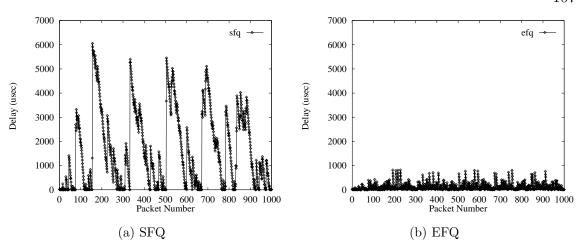

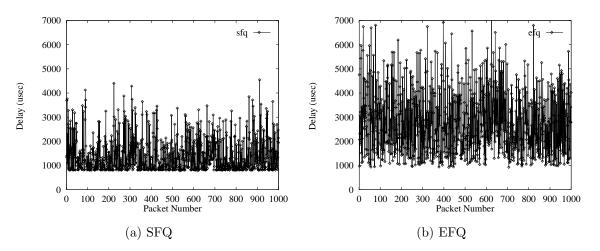

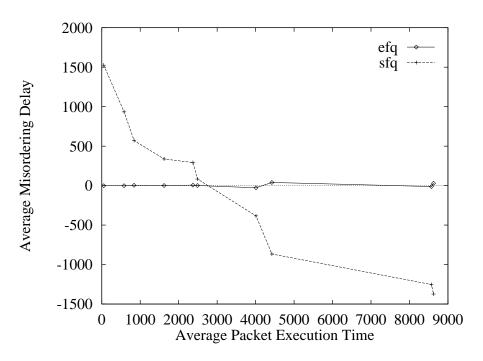

| 5.9  | Packet Delays for a Flow Processed by IP Forwarding    | 107 |

| 5.10 | Packet Delays for a Flow Processed by CAST Encryption  | 107 |

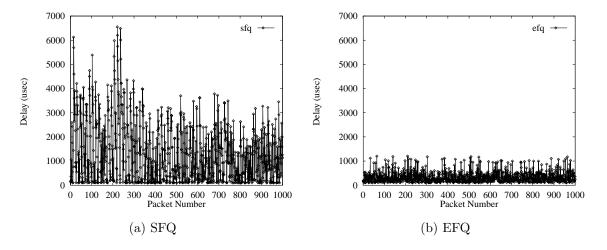

| 5.11 | Packet Delays for a Flow Processed by Reed-Solomon FEC | 107 |

| 5.12 | Variation of Minimum Packet Delay                      | 108 |

| 6.1  | Simulation Data Path                                   | 116 |

| 6.2  | Simulation Control Path                                | 117 |

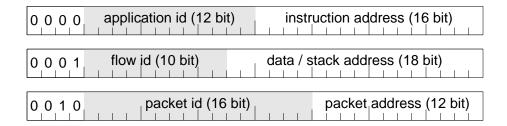

| 6.3  | Simulation Address Space                               | 119 |

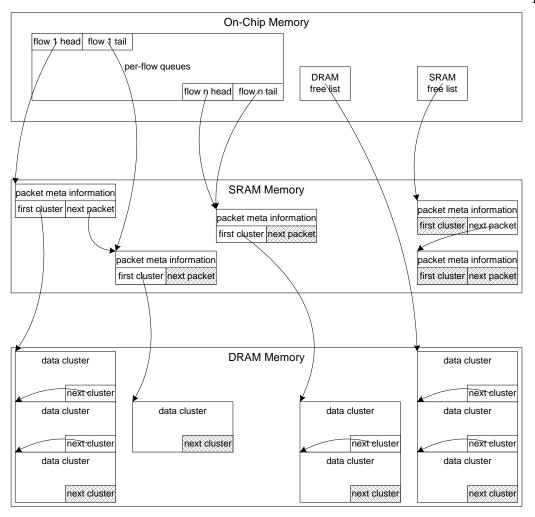

| 6.4  | Queue Memory Layout                                    | 120 |

| 6.5  | Application Template                                   | 122 |

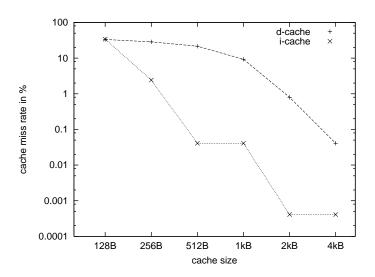

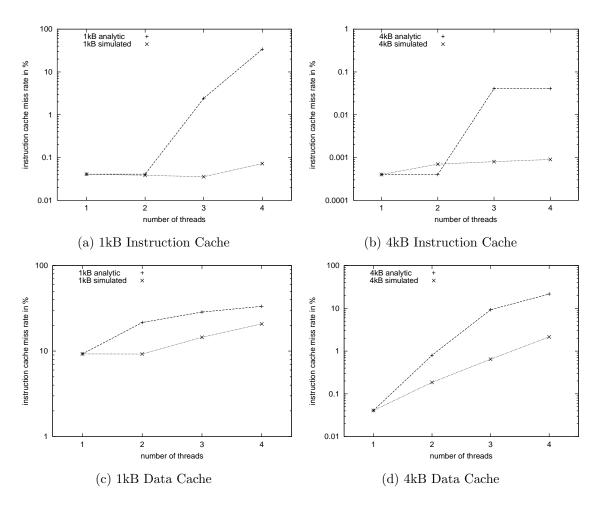

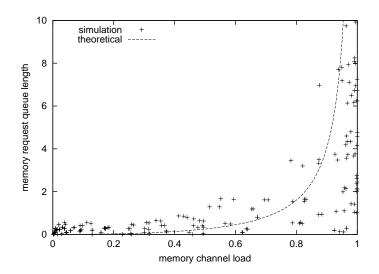

| 6.6  | Simulation Workload Cache Misses                       | 124 |

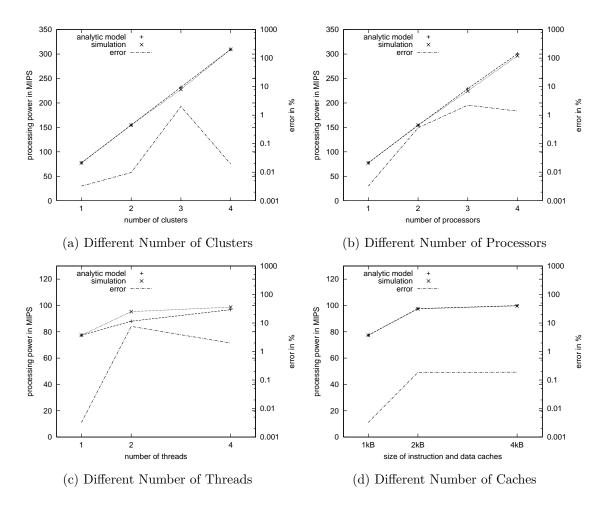

| 6.7  | Comparison of Analytic Model and Simulation Results    | 129 |

| 6.8  | Comparison of Analytic and Simulated Cache Miss Rates  | 130 |

| 6 9  | Memory Channel Queue Length                            | 131 |

# Acknowledgments

I would like to express my thanks to the numerous people who have helped me in completing this work. First and foremost, I want to thank my advisor Jon Turner for his guidance and the many fruitful discussions. His constant quest for meaningful research and results has taught me invaluable lessons for my career. I also want to thank the members of my thesis committee, Mark Franklin, Jason Fritts, David Richard, and Marcel Waldvogel, who have given me constructive input. In particular, I want to thank Mark Franklin with whom I have collaborated on much of the research related to computer architecture. For support with every-day lab work I want to thank John DeHart, who helped me with many of the measurements. Thanks to Sumi Choi, Dan Decasper, and John DeHart for all the work on the ANN project. For interesting discussions on all kinds of topics, I would like to thank Anshul Kantawala, David Taylor, Samphel Norden, Jai Ramamirtham, Prashant Pappu, and Sherlia Shi. Finally, I want to thank Ed Spitznagel, who was a great officemate for the past four years.

For financial support, I would like to thank DARPA and IBM Research, who paid for my stipend and many conference trips. Especially, I would like to thank Mahmoud Naghshineh from IBM, who sponsored my IBM Research Fellowship.

I thank my fianceé Ana Lucia Caicedo for her love and patience throughout my time as a graduate student. For further non-technical support, I want to thank all the "fools" from the  $4^{th}$  floor in Bryan Hall who were fun to interact with. I thank Dr. Roman for his advice on how to run the Friday Happy Hour and on how to find a faculty position. Thanks to the people from the Evolutionary Biology program at WashU who gave my mind a respite from computer science when needed.

Finally, I thank my parents for having me brought up to appreciate the value of friends, travel, respect, and education.

Tilman Wolf

Washington University in Saint Louis August 2002

### **Preface**

Hundreds of scientific papers are being published every year proposing changes to existing protocols (e.g., TCP) or introducing new communication mechanisms (e.g., mutlicast, QoS). In practice, however, only very few modifications to the current Internet are deployed. One reason is that most improvements require changes to current Internet routers, which means that expensive equipment that is already in place has to be replaced. For economic reasons, it is infeasible to do this more often than every few years.

To address this problem, it was proposed that packet processing be performed in software on each node in the network. Such a network is called an "active network" or "programmable network." Much funding by DARPA has been put into this research area, including the Active Network Node project at Washington University. One key issue in our project was the limited amount of processing that can be performed at link rates. From this need for more processing power, my work on high-performance programmable routers has been motivated.

The processing engine of a programmable router, the "network processor," is the most performance-critical component. While network processors have recently been developed commercially, not much effort has been put into systematically evaluating the processing requirements and design alternatives of these multiprocessors. It is imperative to obtain a quantitative understanding of system issues in order to develop programmable routers that scale well and can keep up with the ever-growing link speeds and application demands. My work proposes such a programmable router design based on workload measurements and analytic performance modelling. The scope of this work also includes network processor scheduling and system simulation, which brings together issues from networking, computer architecture, and system design.

# Chapter 1

### Introduction

Industrialized countries have become more dependent on a widely accessible and high-performance networking infrastructure. The Internet is used for personal and business communications as well as online commerce in the form of e-shopping and e-business. It is crucial that networking technology maintains and further improves the performance and the range of functionality of the Internet.

With the wide deployment of optical fiber over the past years, raw bandwidth has become a widely available commodity. A key challenge now is to make use of this bandwidth and extend networks to provide advanced services. The need for new services lies in the fact that the protocols that were originally developed for the Internet are not addressing issues that have recently become critical (e.g., security). It is important that the Internet be able to adapt to support such changes. However, current routers in the network are specialized for fast processing of existing protocols. New protocols can only be supported by replacing existing routers with new routers.

Programmable routers offer a solution to providing this necessary flexibility in the network. By processing packets in software rather than specialized hardware, a programmable router can be re-programmed to support new protocols and services. One key challenge is to design such a programmable router in a way that it can achieve data forwarding performance that is comparable to traditional networks. This dissertation addresses this issue and proposes a scalable, high-performance design for programmable routers.

#### 1.1 Trends in Networking

One reason for the lack of flexibility in today's Internet is that it evolved from a network that was originally designed in the 1970's. The design goals then were to have a simple, packet-switched communication infrastructure, which connects a large number of networks with gateways (or "routers") [Cla88]. The network itself was kept relatively simple and provided basic communication between the end-systems. This led to networking protocols, where most of the complexity is implemented on the end-systems (e.g., retransmission of lost packets, congestion control based on round-trip time measurements).

Over time, several additions have been proposed and implemented in the Internet, because the initial design did not consider them. Since the Internet does not support the dynamic deployment of new protocols, these additions were specifically added to later generations of routers. The following list highlights a few, which are characterized by the need of support by the network (i.e., they cannot be implemented on end-systems only):

- Random Early Detection [FJ93] is a queue management scheme for routers to fairly drop packets from rogue TCP flows. This is can be implemented in a very simple fashion, but it constitutes a type of processing on a router. Almost all current routers implement some form of RED, but only few use it in practice.

- Firewalls [Mog89] are a standard security component of most networks. Packets are filtered depending on rules defined by the network administrator. This enables the blocking of network traffic that could compromise the security of hosts on the network (e.g., port scanning). The firewall rules can be numerous and complex, which requires significant computational power on the firewall to keep up with typical access link speeds.

- Network address translators (NAT [EF94]) are another common component in IP networks. A NAT allows multiple hosts in a stub domain to use a single globally unique IP address. IP packets passing between the stub domain and the Internet are modified by the NAT. This reduces the number of IP addresses used by a stub domain and thereby extends the time before all IP addresses are assigned.

- Web switching [AAP+00] is a method of distributing a web server over several physical machines while presenting a single font-end to the outside. Web

switches parse HTTP requests in packets and determine the appropriate server to which to forward the request. Since the HTTP request is sent only after the TCP connection is established, the web switch also has to splice the TCP connection between client and back-end server.

• IP traceback [SPS+01] allows the network to keep state on the traffic that was forwarded and provides the ability to identify the sources of possibly malicious data flows. For this purpose, routers need to compute a hash from the data packet and store it for a possible later audit.

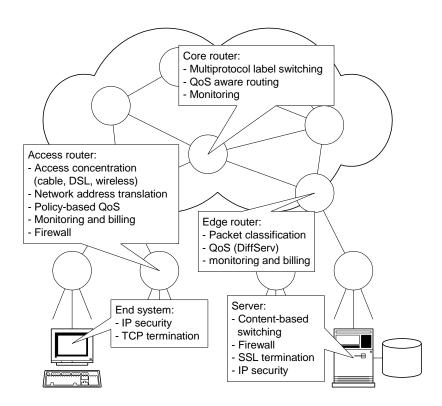

In practice, these changes either have been slowly added to all routers (as for RED) or they were implemented on servers that are connected to the routers (as for NAT and Web Switching). These specialized solutions are working reasonably well for individual problems, but they are limited in that each extension requires its own solutions. This approach is limited as more and more changes are proposed. A few examples of desirable functions that the network should support are shown in Figure 1.1. Also, as the number of devices connected to the Internet increases with time, the diversity of protocols and the range of services will further increase. A more general approach to providing flexibility to adapt to new protocols and services is by means of programmable routers.

### 1.2 Programmable Networks

A programmable network consists of programmable routers that have general-purpose processing units in their data path. These processing units can be programmed to perform various protocol operations as well as complex payload processing. Unlike traditional routers, deployment of new protocols can be achieved by reprogramming the system rather than exchanging expensive hardware. This programmability of the data plane extends the traditional store-and-forward paradigm of routers to store-process-and-forward. The processing step is where interesting new services and protocols can be integrated into the network.

The philosophy of opening the network to be programmable raises many administrative issues. In particular, safety and security are points of increasing concern. We assume that programmable networks would only allow system administrators and

Figure 1.1: Network Services Requiring Programmability.

router vendors to deploy well-tested router software that provides the required service functionality. Such a model might later migrate to a fully open programming platform as proposed by the active networking community.

The flexibility of a programmable router comes of course at a price. Software processing is inherently slower than customized logic that is optimized for protocol processing. However, the increased life-time of a programmable router and the shorter development phase for new protocol support can pay for possibly lower performance. Also, highly parallel processing engines can be developed for this environment to achieve processing rates comparable to traditional routers.

On the commercial side, there has been much development on such network processors. Numerous companies have announced and built such multiprocessor systems-on-a-chip for this environment (e.g., IBM's Power NP, Intel's IXP1200, and Motorola's C-5). However, a general architecture for network processors has not been developed, and a quantitative method for comparing designs is not available. There is much need for a more systematic design approach for these architectures.

The field of programmable routers is still in its early years. It can be expected that there will be much growth in this area. One reason is that the flexibility

provided by programmable routers enables companies to deploy new services faster than in traditional networks. This is particularly important, since the telecommunications market has saturated on raw bandwidth. Services are now what differentiates telecommunications providers, and the ability to quickly react to user demands and competitions will be key to survival in the new telecommunications age.

#### 1.3 Technology Challenges and Opportunities

The need for high performance in the processing engines of programmable routers requires consideration of the newest available integrated circuit technologies. Therefore it is important to observe the technology growth trends in these areas. Of particular interest are:

- Communication Link Speed. Programmable router performance must scale with the growing data link rates.

- Semiconductor Technology. Economic reasons require processing engines to be implemented on single chips. Higher levels of integration allow more processors and memory on such an embedded system.

- Processor Architecture. Advances in processor design give opportunities for higher performing processing engines.

- Application Complexity. With the proliferation of processing engines in networks, application programmers will invent new applications, services, and protocols that will require more and more processing power.

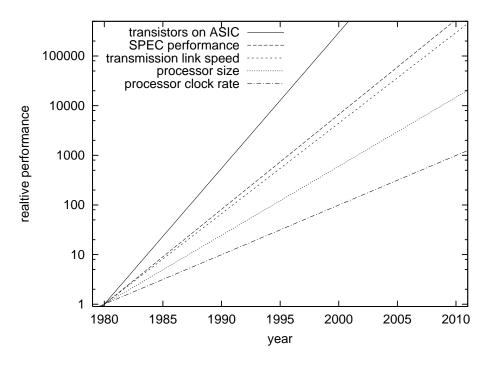

These four areas are relevant to programmable router design as they directly impact the performance requirements (link speeds and application complexity) and the possible solutions (ASIC technology and processor design). In particular, link speed, ASIC technology, and processor performance follow exponential growth characteristics. Moore's "Law" [Moo65] states that the number of transistors on a chip doubles about every 18 months. This exponential growth has impacted other measures in semiconductor technology (i.e., exponential increase of clock speeds). Considering the exponential growth in performance, Figure 1.2 shows the growth rates for the important technologies (each technology is discussed in more detail in Chapter 2, where also the sources for this data are given). It shows that communication

Figure 1.2: Growth of Semiconductor and Communication Technologies.

link speeds grow rapidly, but the density of applications-specific integrated circuits (ASICs) grows even faster. This allows network processor designs with multiple parallel processors to keep up with link speed growth. Since the clock rates and performance of processors themselves grow over time, we can show that processing power of the network processor design proposed in this work even grows faster than link speeds. As a result, more complex network protocols and services can be supported.

#### 1.4 Programmable Router Design

There are two interesting design questions for programmable routers. One is how to provide the functionality of dynamically installing new protocols and services, and the other is how to obtain the necessary performance to compete with traditional routers. The issue of functionality has been addressed by some research in the area. Extending software-based routers to dynamically support new protocols and applications has been a goal of the "active networks" community. An equally important goal for programmable routers is to achieve performance that is comparable to traditional custom-logic routers.

To achieve such performance, two components of a programmable router need to be considered closely. One is the queuing system that moves packets from the interface to the processors and to the switching fabric is an important component. With the additional processing step, this component becomes more complex than in traditional routers as it has to ensure that the packet is processed by the right instruction code on a processor at the right time. This leads to the question how a processing engine should be integrated in each system and what the data and control path should look like. The other component is the processing engine itself. There are many interesting questions regarding the design and configuration of the network processor. It is necessary to consider realistic workload characteristics in order to obtain results that are meaningful for a particular environment. By using analytic performance models, a broad range of configurations can be considered and general performance trends can be derived.

A related issue is the scheduling of processing on a router port. Since neither traditional processor scheduling schemes nor link bandwidth schedulers apply for this environment, a new scheduling algorithm needs to be developed. The goal of a scheduling algorithm is give performance guarantees for flows and improve the processing throughput of a system by exploiting instruction locality.

In this work, the above issues are discussed and solutions are proposed and evaluated.

#### 1.5 Organization of Dissertation

The dissertation is organized as follows:

Chapter 2 introduces the design that we consider for the programmable router and the network processor chip. Based on the trends in supporting technologies, a scalable design is derived and described in detail.

Chapter 3 discusses the workload characteristics for network processors. Quantitative results are derived from a benchmark that was developed specifically for this purpose. This chapter also discusses how workloads for NPs are different than for workstations and what impact this has on the overall processor design.

The network processor that is described in Chapter 2 has a variety of configuration options. Chapter 4 derives an analytical performance model that can be used to find an optimal configuration and provides a method for exploring the large design space.

The scheduling of the network processor is addressed in Chapter 5. In particular, two scheduling strategies are investigated; one that considers locality in the data

stream to reduce context switching overhead and one that addresses fair sharing of processing resources under the premise of unknown processing times.

Chapter 6 ties the results of Chapters 2-5 together in a system simulation. The analytical results for ASIC optimization and scheduling are simulated and verified. Additional results are derived to evaluate overall system performance and demonstrate its feasibility.

Finally, Chapter 7 summarizes the contributions of this work, addresses future work, and concludes this thesis.

Related work to each topic is discussed individually in each chapter.

# Chapter 2

# Programmable Router Design

The ability to not only forward packets through a network, but also process them on a router, is the key to implementing new services and protocols without changing the underlying hardware infrastructure. Such processing can range from simple routing and queuing decisions to complex payload modifications. Performing such processing in software rather than custom logic opens the possibility to adapt and deploy new services by simple changes in the software. The crucial challenge in such a system is not only to be able to provide the functionality to dynamically change the forwarding loop for selected data streams. It is equally important that the performance of the system be comparable to custom logic solutions despite the fact that software processing is inherently slower than hardware solutions.

This chapter briefly motivates programmable networks by discussing our implementation of a software-based programmable router. Two applications are introduced to show the spectrum of processing demands necessary. This leads to our programmable router design discussed in Section 2.2. In particular the processing engine is discussed in detail. The scalability of this design is shown under current technology growth trends. Related work at the end of the chapter discusses commercial solutions and contrasts them to the port design proposed here. Parts of this chapter are published in [WT00] and [WT01].

### 2.1 Software-Based Programmable Routers

General-purpose workstation processors that perform packet routing and forwarding in software were common router configurations in the 1980's. Typical link speeds of a few kilobits per second did not exceed the processing power of such a system. As performance demands for communication changed in the 1990's towards link speeds of several megabits per second, software-based routers were not able to keep up with this trend. As a result, ASIC-based routers were developed to provide basic protocol processing functionality at high speeds. The majority of current Internet routers are still ASIC-based. Their limitations in supporting new protocols led to efforts re-introduce the flexibility and extensibility of software-based systems.

General-purpose processing as part of the data path and deployment of processing code via the packet itself was initially proposed by Tennenhouse and Wetherall in 1996 [TW96]. From this idea, numerous research projects have spawned to develop infrastructure that can process packets in the data path and dynamically deploy the processing code. The majority of these projects were and are aimed at investigating and implementing software-based "active routers". Key questions are how to dynamically install protocol processing code in the data path, how to deploy code modules, and how to safely and securely execute arbitrary code on a router. We have developed such a software-based programmable router in the Active Network Node project at Washington University [DPC+99].

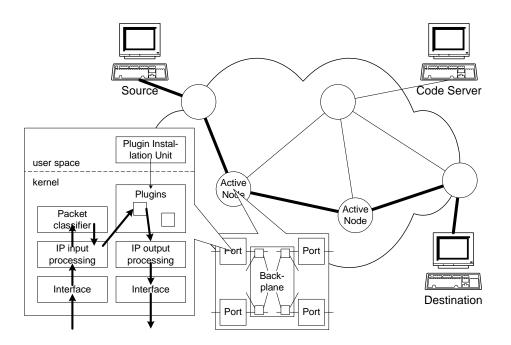

#### 2.1.1 Active Network Node

The Active Network Node uses a programmable port processor [DRST01] on the Washington University Gigabit Switch to implement the active processing functionality (see Figure 2.1). The operating system on the port processors is an extension of NetBSD [Net], which allows dynamic installation of code modules (so-called "plugins") into the O/S kernel. IP packets are received by the O/S and processed by the traditional IP processing steps. They are classified, and if active processing is required, they are forwarded to the plugin code modules. There, the special functionality and protocols can be processed. Afterwards, packets are sent through the IP output processing to the switch backplane.

Plugins can be installed dynamically (i.e., when the first packet arrives that requires a new plugin) or statically (i.e., by the administrator for commonly used plugins). The code distribution for this system is done by code servers and clients on

<sup>&</sup>lt;sup>1</sup>The difference between an "active router" and a programmable router lies in the way packet processing code is developed and deployed. The "active networks" community supports the philosophy of having end-systems (i.e., applications or users) deploy code modules along the path of a data stream. For programmable routers, it is assumed the only well-defined code modules (i.e., new protocol support developed by the router vendor) are installed by administrative entities in the network.

Figure 2.1: Active Network Node. The data path is indicated by arrows.

the respective nodes. If a plugin is requested, the Plugin Installation Unit checks the local plugin repository for the module. If the plugin module cannot be found, it is downloaded from a remote code server.

The major contribution of this project, which makes it different from many other active node implementations, is that the processing of packets occurs entirely in the operating system kernel. This avoids the need to cross the boundary between kernel and user-space, which is associated with overheads from switching between contexts. Therefore much higher packet forwarding rates can be achieved.

#### 2.1.2 Active Applications

The following two examples of applications that use processing on routers illustrate how such a functionality can be used. More applications and their quantitative characteristics are discussed in Chapter 3, where a programmable router benchmark is presented.

#### **Application-Specific Queuing**

Once a node is able to consider application-specific requirements of data flows, queuing policies can be adapted to improve the drop policies for flows. In this particular application, which was implemented by Keller *et al.* [KCD<sup>+</sup>00], a WaveVideo data

flow was used. WaveVideo is a wavelet-based encoding of video data that separates each frame into 33 frequency components [FDW<sup>+</sup>99]. Low frequency components define the general image in the frame; high frequency components contain the details of the image.

When a WaveVideo transmission encounters congestion in the network, it is desirable that higher-frequency components are dropped first. With traditional queuing, it is not possible for the router to make any distinction among packets. On an active node, a plugin can determine if a packet should be forwarded or dropped. This decision is based on the frequency-level of the current packet and the output queue length. The result of this application-specific queuing is that under congestion the subjective quality of the WaveVideo at the client is significantly higher than under a random dropping policy. Also the quality degrades gracefully under increasing congestion.

While the processing for this kind of application-specific queuing is very simple, it has a considerable effect on the application. It should be noted that this particular method of queuing could not easily be implemented on end-systems in traditional networks without processing capabilities on the router.

#### **Data Aggregation**

An example of an active application, which is much more demanding in terms of processing power, is Audio Data Aggregation [WC01]. The basic idea is to use the capability to store and process packets to combine several data flows into a single stream. In the process, data from multiple sources is aggregated, such that the outgoing stream has lower bandwidth that the sum of all incoming streams. This mechanism has also been described as "reverse multicast" [CGM<sup>+</sup>01].

Practical applications of this aggregation are scenarios, where a large number of sensors transmit periodic status information, for example, a set of temperature sensors in a building. Instead of forwarding all messages from all sensors to one central location, the active nodes in the network can aggregate the information and forward only a "summary." For temperature, a suitable aggregation function is to compute the minimum, maximum, and average temperature of all nodes that are connected to that node. Another example is groups of people, who periodically transmit their geographic position (e.g., soldiers in a battlefield). For this case, the centroid or the bounding box of the group can be used as an aggregation function.

If the networking infrastructure matches the location of the sensors (e.g., all sensors in one room send to one particular active node), then the aggregation steps can be arranged in a hierarchical fashion. By connecting to the output from different levels of the aggregation hierarchy, an observer can navigate the entire sensor space at various levels of detail. Such a hierarchical aggregated multicast is described in more detail in [WC01].

We have implemented this reverse multicast on the Active Network Node for an audio conferencing application. With possibly multiple participants transmitting audio data, the network can bridge the audio information together into a single data stream (with the same bandwidth as an individual stream). There is a twofold benefit in doing that. For one, the overall amount of data that is sent through the network is reduced. Instead of each sender sending to all receivers, the audio is aggregated on the first active node and each receiver receives only one single data stream. The other benefit lies in the reduced processing requirements on the end-system. Since the bridging has already been performed by the network, the audio stream can be played back directly. In a traditional scheme, the end-system would need to bridge all data streams individually. This is particularly useful for "thin clients" (e.g., mobile PDAs), which have limited processing power. Another nice feature of audio aggregation in the network is that the multiparty aspect of the conference becomes completely transparent to the end-system software. In our implementation, we used an IP telephony application, which can only support point-to-point communication. Since the active network performed the bridging function, the aggregated stream was indistinguishable from a point-to-point stream, and thus the application could be used for conferencing without any modifications (except the control plane, which is not considered here).

#### 2.1.3 Performance Issues

The implementations of the above applications have shown that providing the functionality of processing packets in software on a router can be achieved. An interesting issue is the level of performance that can be achieved with such a system. For the application-specific queuing application, very little processing power is necessary, and high throughput can be achieved that is comparable to the throughput of a typical software-based router. However, the processing of the entire payload for the aggregation limits the throughput in the audio application. On the Active Network Node,

which uses a 167MHz Pentium processor, the processing of one 400 byte packet takes in the order of  $750\mu$ s, which translates to less than 5Mbps throughput. Such performance is definitely several orders of magnitude below the needs in high-bandwidth environments. This low throughput can be attributed to several causes:

- Heavy O/S Overhead. The programmable router uses a full-blown NetBSD operating system, which is not optimized for packet processing.

- Non-Optimized Implementations. The proof-of-concept implementations lack the fine-tuning that can be found in commercial software.

- Non-Optimized Architectures. The processing architecture is not optimized for networking applications, but for traditional workstation-type processing.

These three points clearly limit the performance of a software-based router. However, it cannot be expected that improving on these shortcomings would increase the data throughput by more than an order of magnitude. The real limit of the Active Network Node (and most other active router implementations) lies in the use of a single-processor system. To overcome this limitation, the remainder of this Chapter introduces a programmable router design that emphasizes on a high-performance processing infrastructure.

#### 2.2 High-Performance Programmable Routers

Higher levels of processing power can be achieved by exploiting parallelism in networking workloads. The packet processing can then be performed by highly parallel multiprocessor systems, which are called "network processors." The following discusses the parallelism in networks and shows our router design.

#### 2.2.1 Parallelism in Networking Workloads

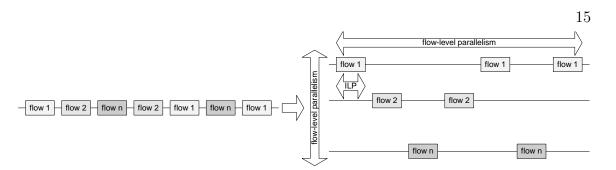

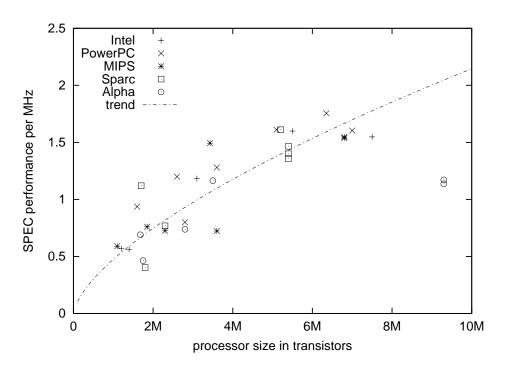

In a networking environment, more levels of parallelism are available to the system designer than in traditional workstation multi-processors. This enables the design of processing engines with a large number of independent processors without the need for much communications or synchronization among them. There are three layers at which parallelism can be exploited in a network multiprocessor (see Figure 2.2):

Figure 2.2: Parallelism in Networking Workloads.

- Flow Level. Packets from different flows do typically not interact with each other. Therefore they can be processed completely independently.

- Packet Level. In many protocols, there is no dependency among packets within a flow. For example, simple IP protocol forwarding does not keep or modify state between packets. Therefore packets can be processed in parallel, even if they belong to the same flow. In some cases it is necessary to ensure that the original packet order is restored after processing.

- Instruction Level. When processing a packet, there are several ways that parallelism can be exploited. These approaches are the same as found in traditional processor architecture. In particular, pipelining and instruction-level parallelism can be used.

Parallelism in the processing workload can be directly translated to parallelism in a processing system. For this to work, we need to make a few assumptions. First, it is assumed that the processing requirements for a single flow do not exceed the processing power of a processor. Otherwise processing would have to be split over several processors creating similar synchronization problems as encountered in parallel workstation processors. Second, if there are dependencies (e.g., between packets of a flow), the scheduler assigns packets from the same flow to the same processors. This is discussed in more detail in Chapter 5. These limitations are not expected to pose significant constraints on realistic systems.

#### 2.2.2 Programmable Router Design

The proposed programmable router design extends a traditional router design by adding a network processors on router ports. This differs slightly from some commercial approaches, where the entire router port functionality is implemented on network

processors. In our system, the network processor could be removed and the remaining components would still provide basic router functions.

#### **Processing Resources**

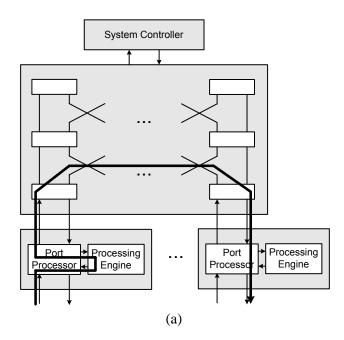

A traditional router can be augmented to support flexible processing in different ways. One approach is to add a processing engine at each router port. Another is to provide a shared pool of processing engines that can be used to process traffic from any port. These two baseline system designs are shown in Figure 2.3. The routers are based on a scalable cell switching fabric which connects to external links through *Port Processors*. In the first design, all ports are augmented by a *Processing Engine* that can perform active processing. In the second design, a set of router ports is dedicated to active processing. These ports are equipped with processing engines but do not have external interfaces.

The first approach is most appropriate when all ports have comparable requirements for active processing. The second makes sense when ports have widely varying needs. One can also combine these approaches by having both per-port processing engines and a shared pool to augment the processing power of ports with particularly high processing needs. For the rest of the discussion, the first configuration is assumed.

Packets can be processed on the input port, the output port, or both. We assume processing is performed on the input side. The advantage of this approach is that the processing requirements are limited to the link speed of the connected link. If multicast is used, processing has to be done only once. On the other hand, the drawback is that in case of congestion on the output port, processing might be performed on packets that are later dropped.

Packets belonging to passive flows (that is, flows that do not require active processing), are passed directly from the input port at which they first arrive to the output port where they are to be forwarded. Such packets encounter no added overhead or delay, compared to a conventional router. Packets belonging to active flows are received by the input port and sent to a processing engine (either on the same port or on a dedicated processing port) where they are enqueued and eventually processed. After processing, the packets are forwarded to the proper output port. If there are processing engines on all ports, processing may also be done at the output port. To provide the maximum flexibility, an input port can distribute packets to various processing engines to achieve system-wide load balancing.

(a) Processing Engines on all Ports

(b) Dedicated Processing Ports

Figure 2.3: System Organization of Programmable Router.

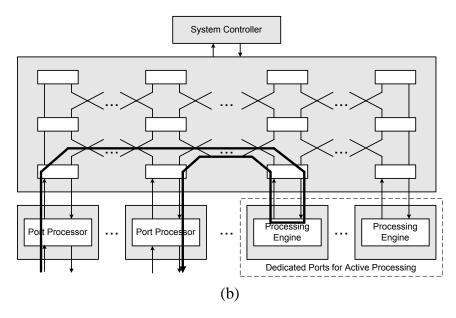

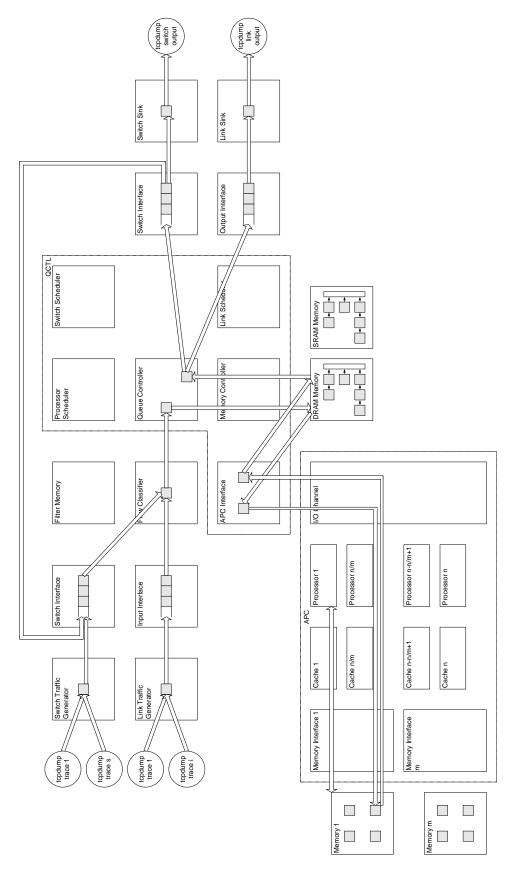

Figure 2.4: Router Port Processor Design. Shaded areas indicate distinct chips.

The switching fabric can be implemented in a variety of ways. For concreteness, we assume a multistage network such as described in [CFFT97]. That system supports external link rates up to 2.4 Gb/s and can be configured to support hundreds or even thousands of such ports. The active router's port processors perform packet classification, active processing and fair queuing. The *System Controller* provides a control and management interface to the outside world and implements routing algorithms and other high level operations.

#### Router Port

The port design for our programmable router is shown in Figure 2.4. The shaded areas indicate physically distinct logic and memory chips. The center of the port is the *Packet Classification and Queuing chip* (PCQ), which controls the data flow through the port. The processing engine with the *Application Processing Chip* (APC) and off-chip memories comprises the network processor of the system.

#### Data Path

The PCQ performs classification of packets arriving from the *Transmission Interface*, to determine how they are to be processed and where they are to be sent. It also manages queues on both the input and output sides of the system. The PCQ has two memory interfaces, one to a *Filter Memory* used for packet classification and one to a *Queue Memory* used to store packets awaiting processing or transmission.

As packets are received from the Transmission Interface, the headers are passed to the *Packet Classifier* which performs flow classification and assigns a tag to the packet. At the same time, the entire packet is passed to the *Queue Controller* (QCTL) which segments the packet into cells and adds it to the appropriate queue. This requires a fast general flow classification algorithm, such as the one described in [SSV99].

The processing engine is the key component of the programmable router. In our system, the APC performs active processing for packets that require more processing than just plain forwarding. Note that removing the APC from the system still leaves a router port that is capable of plain forwarding of packets. After processing, packets are queued by the QCTL and then scheduled for forwarding through the switching fabric to the output port. Packets that are received from the switch fabric are also queued, possibly processed, and scheduled for transmission on the outgoing link.

#### Queuing System

The queuing system of the router stores packets which need to wait for processing or transmission to the switch fabric or the outgoing link. Packets can be assigned to queues in a fully flexible fashion (e.g., per flow or aggregate). The queues can be rate-controlled to provide guaranteed quality of service. The filter database determines whether flows are aggregated or handled separately.

To make the implementation of the queuing system efficient, the queues can be implemented with a combination of two types of memory. Fast (and expensive) SRAM and cheaper (but slower) DRAM. There is also a limited amount of on-chip memory available in the PCQ. The queue data structures can be split onto memories in the following way with respect to the need for fast access versus more storage:

• Per-flow Queue Head and Tail Pointers. These pointers should be stored on the PCQ, since they are accessed frequently. It can be assumed that there is only a limited number of such pointers necessary (particularly since multiple flows can be aggregated into traffic classes).

- Packet Meta Information and DRAM Pointers. This data structure is necessary

for each packet and should be stored in SRAM. It contains higher-level information for each packet (i.e., packet size, classification results, output port, etc.)

and a pointer to the first memory location in DRAM that contains the actual

packet data.

- Actual Packet. The packet is stored in DRAM in a set of "chunks." Each chunk contains a fixed amount of packet data and a pointer to the next data chunk.

Chapter 6 contains more details on the actual implementation of the queuing system on our system simulator.

One key design variable for any router is the amount of memory to provide for queues and how to use that memory to best effect. The usual rule of thumb is that the buffer size should be at least equal to the bandwidth of the link times the expected round trip time for packets going through the network. For 2.4 Gb/s links in wide area networks, this leads to buffer dimensions of roughly 100 MB. Such large buffers are needed in IP networks because of the synchronous oscillations in network traffic produced by TCP flow control and the long time constants associated with these oscillations. In the context of large buffers, per flow queuing and sophisticated queuing algorithms are needed to ensure fairness and/or provide quality of service. Flow control is also needed within a router which has hundreds of high speed ports. Without flow control, output links can experience overloads that are severe enough to cause congestion within the switch fabric, interfering with traffic destined for uncongested outputs. Fortunately, the large buffers required by routers make it possible for cross-switch flow control to be implemented with a relatively coarse time granularity (1-10 ms). Using explicit rate control, output PPs can regulate the rate at which different input PPs send them traffic so as to avoid exceeding the bandwidth of the interface between the switch fabric and the output PP. By adjusting the rates in response to periodic rate adjustment requests from the input PPs, the output PPs can provide fair access to the output links on a system-wide basis or can allocate the bandwidth so as to satisfy quality of service guarantees. Such a rate control mechanism is described in [KDK<sup>+</sup>02].

# 2.3 Processing System

The Application Processing Chip provides the general purpose computational resources needed to implement active networking applications. Since these networking tasks are relatively simple and there are many that can be processed in parallel, it is suitable to use very simple processing cores (a more detailed discussion on the choice of processor cores can be found below). Each APC also has several external memory interfaces, providing access to additional memory, which is shared by the processors on the chip. The processors are arranged in clusters, where processors in a cluster share one off-chip memory interface. The APC processors retrieve active packets from queue memory through the I/O Channel, process them, and write them back out to the proper outgoing queue. Processing instructions and flow state information are stored in the on-chip and off-chip memory. The scheduling of these processing engines and issues related to maintaining consistency in flow state is discussed in Chapter 5.

The APC design shown in Figure 2.4 contains four *Application Processing Units*. Each application processing unit consists of a processor, an SRAM cache memory for instructions and data, and a memory controller for off-chip DRAM access and communication with the I/O channel (not shown). The processing units are linked to the PCQ through an I/O channel, which also provides the interface to the extension port. The *Memory Channel* provides access to the external DRAM.

#### 2.3.1 Processor Architectures

There is a wide range of processor architectures that can be considered for processing on a programmable router. The key criteria that have to be considered for selecting a suitable processor are:

- General-Purpose Processing Capability. The key to flexibility to support new protocols and services lies in having general-purpose processing engines. This does not exclude a design that has a few special hardware accelerators for speeding up common tasks (e.g., checksum computation, table lookups).

- Small Physical Size. One major constraint for processing engines is that they need to fit onto a single chip. Due to the high level of parallelism that can be exploited, multiple small processors can provide more performance than a single, more sophisticated processor.

• Performance on Networking Tasks. The characteristics of tasks that process packets on routers is significantly different from traditional workstation tasks (a quantitative comparison of our network processor benchmark with a workstation benchmark shows this in Chapter 3).

For the processing engine of our router, we consider RISC cores, VLIW processors, DSPs, and specialized co-processors.

#### Reduced Instruction Set Computers

Reduced Instruction Set Computers (RISC) [Pat85] were proposed in the 1980's as an alternative to increasingly complex "Complex Instruction Set Computers" (CISC). RISC architectures are typically relatively simple (several dozen to few hundred instruction, orthogonal addressing modes, etc.), pipelined, and supported by a sophisticated compiler. Since some of the complexity of execution is off-loaded to the compiler, the RISC processor itself is simpler than a CISC processor and thus can be implemented in a smaller area. RISC architectures are particularly suitable for embedded systems, where area constraints are much more pressing than in workstation environments.

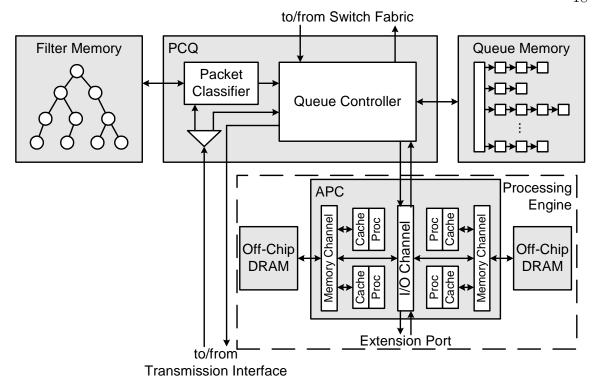

It is important to consider the processing performance that can be obtained from a processor architecture versus the size that it occupies on the chip. Figure 2.5 shows this tradeoff for several generations of the most common processor architectures. The performance metric (y-axis) is the processor's performance on the SPEC benchmark [Sta95]<sup>2</sup> normalized by the clock rate of the processor. This allows a comparison of various processor generations without considering improvements in clock rates due to smaller feature sizes (as done in [AHKB00]). The performance and size values are obtained from [CPU].

As can be seen, the performance of a processor does not increase linearly with the area it occupies. Instead, larger processors of newer generations show proportionally lower performance than smaller, simpler processors. This is partly due to fact that these architectures are optimized for processing of single tasks. Traditional workstation workloads cannot easily be parallelized as is possible in networking environments. High levels of parallelism can be exploited much better by multiple simpler processors, which results in linear performance improvements when replicating processors. Another reason for the observed trend is that modern processors are

$<sup>^2</sup>$ The SPEC performance values were adjusted to SPEC CPU92, because certain architectures predate the release of the SPEC CPU95 benchmark.

Figure 2.5: Processor Performance in Relation to Complexity. The performance metric is SPEC rating per MHz and the complexity is the processor size in transistors.

optimized for speed at the cost of chip area. It is not necessarily clear that older, simpler architectures can be implemented on modern ASICs and clocked at gigahertz rates. However, the clock rates considered in network processor are not at the cutting edge of technology as they are for workstation processors. Therefore, it can be assumed that most processor implementations can be adapted to these increasing clock rates.

This leads to the conclusion that simple RISC cores, like MIPS [MIP98], ARM [ARM99], and PowerPC [IBM98], are suitable processor architectures for network processors.

#### Superscalar and Multithreaded Processors

Numerous improvements to the basic RISC architecture have been proposed. In particular, several methods for exploiting parallelism on the instruction level and thread level have been proposed:

• Superscalar and Very-Long Instruction Word Processors. These processors can issue and execute multiple instructions per cycle exploiting instruction-level parallelism (ILP). Superscalar processors can be scheduled statically by the

compiler or dynamically using scoreboarding techniques. VLIW can only be scheduled statically by the compiler.

- Fine-Grained Multithreaded Processors. Such multithreaded processors maintain hardware contexts for several threads. In case of a stall of a thread, the processor can continue processing another thread [ALKK90]. Most recent multithreaded architecture support zero-overhead context switching, which means that no cycles get lost during a context switch [MMC00].

- Simultaneous Multithreaded Processors. SMT processors also maintain multiple thread contexts. The processor can dynamically schedule multiple instructions from all available threads [HKN<sup>+</sup>92], [TEL95]. This approach is a combination of superscalar and multithreaded processors.

The main goal of all these architectures is to improve the execution time of a single thread and increase the overall processor utilization. In the context of network processors, the individual thread execution time is less significant than the overall processing throughput of the system. Thus, all the architectures need to be examined in the light of usage in a network processor. Such a study has been done by Crowley et al. [CFBB00]. The results have shown that simple RISC multiprocessors perform best under networking workloads. When considering a heavier O/S overhead, the SMT architectures perform best.

For our router design, we chose to use simple RISC processors instead of considering more complex architectures. One key reason is the higher space requirements and smaller overall performance gain as shown in Figure 2.5. Another reason is that with the trends in integrated circuit technology, processor architecture, and link rates, the performance of a RISC multiprocessor outperforms a multiprocessor that uses increasingly complex processor architectures (which will be discussed in more detail in Section 2.4).

The one improvement over RISC that will be considered in this work is the idea of multithreading. Since the shared off-chip memory can create long processor stalls under high loads, it is desirable to keep the processors utilized by adding a few thread contexts. Such an approach is discussed in more detail in Chapter 4, where the performance model of our system is introduced.

#### **Digital Signal Processors**

Digital Signal Processors (DSP) are processors that are specialized for performing highly regular and real-time critical processing. A typical DSP consists of several arithmetic units and multipliers. In each cycle, an instruction can be executed on each unit and data can be moved between them. The operation of a DSP is usually highly pipelined, which allows the DSP to operate at high clock frequencies. Multiple memories or peripherals provide the data and instructions for the DSP. With clock rates as high as one GHz, DSPs can provide significantly more performance than general-purpose processors if the applications match well the regular operating patterns of the DSP architecture.

Traditionally, DSPs have been used in applications involving digital control, audio, telephony, imaging, and video. Recently, DSPs have also been developed for use in networking. For example, the C6000 family from Texas Instruments implements a complete TCP/IP stack on the DSP. This allows certain networking equipment to operate without a host processor, which was traditionally required for running the network protocol processing.

For the programmable router design in this work, we do not consider DSPs, because the arbitrary processing requirements of a programmable router cannot always be mapped efficiently to the regular, pipelined operation modes of DSPs. It is conceivable, though, that the APC can be implemented as a hybrid system that is equipped with a set of DSPs for the few applications which execute more efficiently on such processors.

#### Specialized Coprocessors

There is a set of common operations in the networking domain that are used in a wide range of protocols. For some such operations, specialized coprocessors can perform significantly better than general-purpose RISC processors. Such functions are:

- Checksum and CRC Computations. Several protocols in a typical protocol stack require a checksum or CRC computation across parts of or the entire packet.

- Table Lookup and Packet Classification. Routing and QoS algorithms require such functionality to determine the flow to which a packet belongs.

• Encryption Processing. This is only one example for a processing step that requires intense processing and that can be efficiently implemented in specialized hardware.

As with DSPs, coprocessors can be used in addition to the general-purpose RISC processors. In our system, such coprocessors could be co-located with each RISC processor if they are relatively small (e.g., checksum coprocessors) or be shared among a set of processors (e.g., table lookup unit).

#### 2.3.2 Memory System

For efficient processing of flows, the processors should have enough memory to store both a small operating system kernel and the code for the applications being used. In addition, they need to be able to store the current packet that is being processed as well as per flow state information for the current flow. Since the packets can be brought in from the queue memory as needed, then promptly written back out, not too much on-chip memory is needed for the packets themselves, but the program code and per-flow state could easily consume hundreds of kilobytes of memory. This suggests that the bulk of data should be stored in the off-chip DRAM. To allow the processors to operate at peak efficiency, on-chip SRAM can be used to cache data and instruction code.

Integrated circuits with embedded DRAM have recently been developed. Since the CMOS fabrication process for DRAM optimizes for density rather than speed as in processing logic, it is challenging to combine both on a single chip. We are not considering a second level cache in DRAM at this point, but it might be possible in the future to use DRAM technology and increase the available on-chip memory.

The bandwidth required between an APC and its external memory is determined by the number of APUs on the chip, the instruction-processing rate of those APUs and the fraction of instructions that generate requests to the external memory. Chapter 3 and 4 discuss in detail the application requirements and the performance tradeoffs for different memory interface configurations.

### 2.3.3 I/O System

The I/O channel on the APC transports data packets from the queue memory to the processors. The required I/O bandwidth is a key consideration. In this design, the bandwidth required for the interface to/from the PCQ can be bounded by the link bandwidth. For 2.4 Gb/s links, this implies a bandwidth of 300 MB/s in each direction. To allow for loss of efficiency due to packet fragmentation effects (caused by packets being divided into cells) and to reduce contention at this interface, it is advisable to increase the bandwidth at this interface to 1 GB/s. This can be achieved with a 32 bit interface in each direction, operating at a clock rate of 250 MHz, which is feasible in .25  $\mu$ m technology. It is also possible to implement the I/O Channel as a ring. This can give a simpler implementation but may yield larger delays.

#### 2.3.4 Configurations

The actual configuration of an APC depends on a variety of factors. The issues that influence the performance of a configuration are:

- Workload. Computationally intense workloads require more processing and onchip memory. Simpler processing requires more I/O bandwidth, because packets are moved more quickly between the queue controller and processors.

- Technology. Advances in technology allow higher levels of integration, which yields more processors and more memory on a chip.

- Power Consumption. With more components on a chip and higher clock rate, the power consumption of the APC becomes a critical issue.

- Cost. The overall size of the APC affects the cost of the router port and the overall router system.

Since the overall size of an APC is limited, there is a tradeoff between placing more processors or more memory onto the APC. More processors mean smaller onchip caches, which leads to inefficient execution and more traffic on the memory channel. Fewer processors mean larger on-chip caches and more efficient execution, but also limited overall processing power. It is a challenging problem to find an optimal configuration for the APC. Chapter 4 discusses an analytic solution for this optimization problem and shows results for our system.

## 2.4 Scalability

To illustrate the long-term usefulness of the proposed design, we describe its scalability under current technology trends. The design can be scaled in three dimensions:

- Increase in Number of Router Ports. The number of ports can be increased by configuring the multistage interconnection network to have a larger number of stages. For the design in [CFFT97], a three stage network can support up to 64 ports and has an aggregate capacity of 154 Gb/s, while a five stage network can support up to 512 ports and has an aggregate capacity of 1.2 Tb/s.

- Increase in Processing Capacity Per Port. One can increase (or decrease) the active processing capacity by incorporating more or fewer APC chips at each port. For systems with only a small amount of active processing, APCs can be omitted from most ports, and packets requiring active processing can be forwarded from the ports at which they arrive to one of the ports containing an APC.

- Increase in Processing Capacity per APC. Developments in technology allow more processors, memory, and I/O components to be implemented on a system-on-a-chip. This increases the overall processing power of the APC.

The most significant potential for more processing power lies in the higher levels of integration that can be achieved with newer generations of CMOS technology.

### 2.4.1 APC Design Scalability

To increase the per-port processing capacity of the router, multiple APCs can be arranged in a daisy-chain configuration that connects the APCs via the extension port on the I/O channel. Each interface that connects to another processing chip acts as a gateway and routes data to other APCs further down in the chain. This design requires that the I/O channel be able to handle the total bandwidth between the queue controller and the APC. It can be assumed that this requirement can be met even for faster link rates. Note, that the total amount of bandwidth between the queue controller and the application processing chips is at most twice the external link bandwidth, since each packet is sent at most once to the processing chips and sent at most once back to the queue controller. Since each processing chip has its own off-chip memory interfaces, the traffic from off-chip memory accesses is restricted to the

individual APC and does not aggregate over multiple chips. Finally, only data traffic that requires processing needs to be sent to an APC. While we expect processing to be an important element of future routers, we expect most packets to be forwarded without processing for the foreseeable future.

### 2.4.2 Technology Scaling

The trends in technology that are relevant to our design are increases in link speed, processor performance, and the transistor density and clock rates of Application-Specific Integrated Circuits (ASICs). The basis for our analysis is Moore's Law, which states that the number of components on an integrated circuit doubles roughly every eighteen months [Moo65]. This was first predicted in 1965 and has found to be accurate ever since [GGPY89]. It is expected that these trends will continue at least for another decade [Sem01].