#### Washington University in St. Louis

### Washington University Open Scholarship

McKelvey School of Engineering Theses & Dissertations

McKelvey School of Engineering

Summer 9-12-2023

## Theory and Application of Dynamic Analog Memory based on Fowler-Nordheim Quantum Tunneling

Mustafizur Rahman Washington University – McKelvey School of Engineering

Follow this and additional works at: https://openscholarship.wustl.edu/eng\_etds

#### **Recommended Citation**

Rahman, Mustafizur, "Theory and Application of Dynamic Analog Memory based on Fowler-Nordheim Quantum Tunneling" (2023). *McKelvey School of Engineering Theses & Dissertations*. 957. https://openscholarship.wustl.edu/eng\_etds/957

This Dissertation is brought to you for free and open access by the McKelvey School of Engineering at Washington University Open Scholarship. It has been accepted for inclusion in McKelvey School of Engineering Theses & Dissertations by an authorized administrator of Washington University Open Scholarship. For more information, please contact digital@wumail.wustl.edu.

#### WASHINGTON UNIVERSITY IN ST. LOUIS

McKelvey School of Engineering Department of Electrical & Systems Engineering

> Dissertation Examination Committee: Shantanu Chakrabartty, Chair Netanel Raviv Bruno Sinopoli Chuan Wang Ning Zhang

Theory and Application of Dynamic Analog Memory based on Fowler-Nordheim Quantum Tunneling by Mustafizur Rahman

A dissertation presented to the McKelvey School of Engineering of Washington University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> August 2023 St. Louis, Missouri

© 2023, Mustafizur Rahman

# **Table of Contents**

| List of | Figures                                                                  | $\mathbf{v}$ |

|---------|--------------------------------------------------------------------------|--------------|

| List of | Tables   •                                                               | viii         |

| Acknow  | wledgments                                                               | ix           |

| Abstra  | $\mathbf{ct}$                                                            | xi           |

| Chapte  | er 1: Introduction                                                       | 1            |

| 1.1     | Dynamic Memory in AI                                                     | 2            |

| 1.2     | Dynamic Memory in cryptographic security                                 | 5            |

| 1.3     | Contributions                                                            | 7            |

| 1.4     | Organization of this Dissertation                                        | 8            |

| Chapte  | er 2: Synaptic Memory Consolidation using FN-tunneling                   | 10           |

| 2.1     | Introduction                                                             | 10           |

| 2.2     | Results                                                                  | 14           |

|         | 2.2.1 FN-synapse Characterization                                        | 14           |

|         | 2.2.2 FN-synapse Network Capacity and Memory lifetime without plasticity |              |

|         | modulation                                                               | 17           |

|         | 2.2.3 Plasticity modulation of FN-Synapse Models                         | 19           |

|         | 2.2.4 Continual Learning using FN-synapse                                | 22           |

| 2.3     | Materials and Methods                                                    | 25           |

|         | 2.3.1 Weight Update For Differential Synaptic Model                      | 25           |

|         | 2.3.2 Optimal Usage Profile                                              | 26           |

|         | 2.3.3 Achieving Optimal Usage Profile on FN-synapse                      | 27           |

|         | 2.3.4 FN-synpase Network SNR Estimation for Random Pattern Experiment    | 28           |

|         | 2.3.5 FN-synapse with Tunable Consolidation Characteristics              | 31           |

|         | 2.3.6 Programming and Initialization of FN-synapses                      | 33           |

|         | 2.3.7 Hardware and Software Experiments for Random Pattern updates       | 34           |

|         | 2.3.8 Probabilistic FN-Synapse Model                                     | 35           |

|         | 2.3.9 Neural Network Implementation using FN-synapses                    | 37           |

| 2.4     | Discussion                                                               | 38           |

| Chapte | er 3: Adaptive Synaptic Array using FNDAM                                     | 42  |

|--------|-------------------------------------------------------------------------------|-----|

| 3.1    | Introduction                                                                  | 42  |

| 3.2    | Result                                                                        | 46  |

|        | 3.2.1 Dynamic analog memory with asymptotic non-volatile storage              | 46  |

|        | 3.2.2 Characterization of FN-DAM                                              | 49  |

|        | 3.2.3 FN-DAM based Co-design of Classifiers and Neural Networks               | 51  |

| 3.3    | Discussions                                                                   | 54  |

| 3.4    | Methods                                                                       | 58  |

|        | 3.4.1 Initialization of the FN-DAM array                                      | 58  |

|        | 3.4.2 FN Tunneling dynamics                                                   | 59  |

|        | 3.4.3 Weight decay model and FN-DAM dynamics                                  | 59  |

|        | 3.4.4 Chip-in-the-loop linear classifier training                             | 61  |

|        | 3.4.5 Memory Retention Model                                                  | 62  |

|        | 3.4.6 Chip-in-the-loop MLP training on Fisher-Iris dataset                    | 63  |

|        | 3.4.7 FN-DAM based CNN Implementation                                         | 64  |

|        | •                                                                             |     |

| Chapte | er 4: Cryptographic Key exchange based on FN-dynamical system                 | 65  |

| 4.1    | Introduction                                                                  | 65  |

| 4.2    | Related Works                                                                 | 67  |

| 4.3    | Self-powered Timer Security Primitives                                        | 68  |

|        | 4.3.1 Self-powered timers are immune to power side-channel attacks            | 68  |

|        | 4.3.2 Self-powered timers are immune to electromagnetic side-channel attacks  | 70  |

|        | 4.3.3 Dynamics of the self-powered timers can be synchronized                 | 70  |

|        | 4.3.4 Self-powered timers are designed for one-time read and tamper-resistant | 72  |

|        | 4.3.5 Bit generation using self-powered timer                                 | 73  |

|        | 4.3.6 Summary of hardware security primitives offered by self-powered timers  | 73  |

| 4.4    | SPoTKD Protocol                                                               | 74  |

| 4.5    | Security and Performance Analysis                                             | 77  |

| 4.6    | Noise Robustness                                                              | 88  |

| 4.7    | Error Correcting SPoTKD                                                       | 89  |

| 4.8    | Discussions and Conclusions                                                   | 92  |

|        |                                                                               |     |

| -      | er 5: SPRNG based on FN-dynamical system                                      | 94  |

| 5.1    | Introduction                                                                  | 94  |

| 5.2    | Results                                                                       | 97  |

|        | 5.2.1 Secure Self-powered Timers and Spatial Synchronization                  | 97  |

|        | 5.2.2 Secure Seed exchange protocol                                           | 99  |

|        | 0 1                                                                           | 101 |

|        |                                                                               | 102 |

|        |                                                                               | 105 |

| 5.3    |                                                                               | 106 |

|        |                                                                               | 106 |

|        | 5.3.2 Seed Generation                                                         | 107 |

|        | 5.3.3 Randomness Test                                                | 108  |

|--------|----------------------------------------------------------------------|------|

|        | 5.3.4 Extending SSPT lifetime through shifted seed generation        | 108  |

|        |                                                                      |      |

| Chapte |                                                                      | 111  |

| 6.1    | 0                                                                    | 111  |

| 6.2    | Future Direction                                                     | 112  |

| Refere | nces                                                                 | 113  |

| Appen  | dix A: Supplementary Information for Chapter 2                       | 126  |

|        |                                                                      | 126  |

| A.2    |                                                                      | 127  |

|        |                                                                      | 127  |

| A.3    |                                                                      | 131  |

| A.4    | Neural Network Architecture                                          | 132  |

| A.5    |                                                                      | 135  |

| A.6    | Detailed Derivations                                                 | 136  |

|        | A.6.1 Weight Update For Differential Synaptic Model                  | 136  |

|        |                                                                      | 138  |

|        | A.6.3 Signal-to-noise Ratio Estimation for Random Pattern Experiment | 139  |

| •      |                                                                      | 1 40 |

|        |                                                                      | 148  |

| B.1    | 1 1 0 0                                                              | 148  |

| B.2    |                                                                      | 149  |

| B.3    |                                                                      | 150  |

| B.4    |                                                                      | 151  |

| B.5    |                                                                      | 153  |

| B.6    |                                                                      | 154  |

| B.7    | 01                                                                   | 155  |

| B.8    | Retention of MLP parameters                                          | 157  |

# List of Figures

| Figure 1.1: | Picture of traditional memory devices                                                                      | 2  |

|-------------|------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1: | On-device memory consolidation using FN-synapses                                                           | 12 |

| Figure 2.2: | Experimental Weight Evolution of FN-synapse                                                                | 14 |

| Figure 2.3: | Experimental Characterization of a single FN-synapse                                                       | 16 |

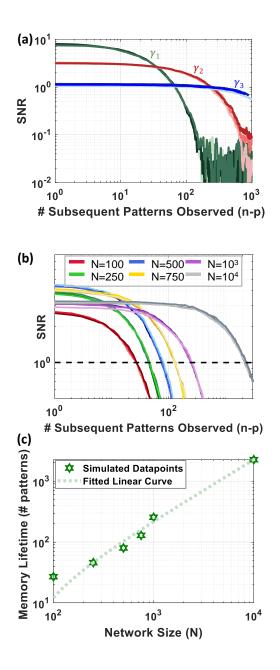

| Figure 2.4: | Comparison of measured and simulated memory consolidation for an<br>empty FN-synapse network               | 17 |

| Figure 2.5: | Network capacity and saturation experiments                                                                | 21 |

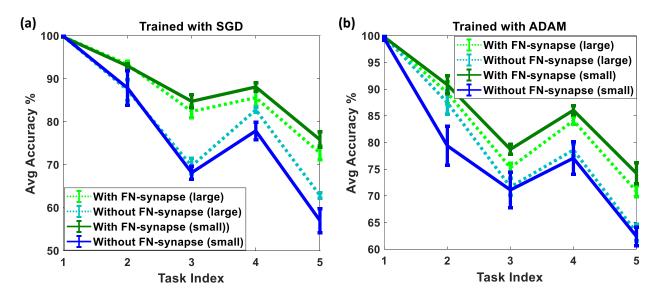

| Figure 2.6: | Continual learning benchmarks results and insights                                                         | 23 |

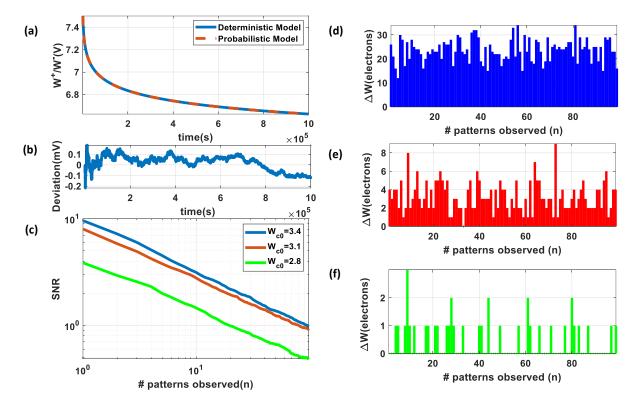

| Figure 2.7: | Comparison between the output of the probabilistic FN-synapse model and the deterministic behavioral model | 35 |

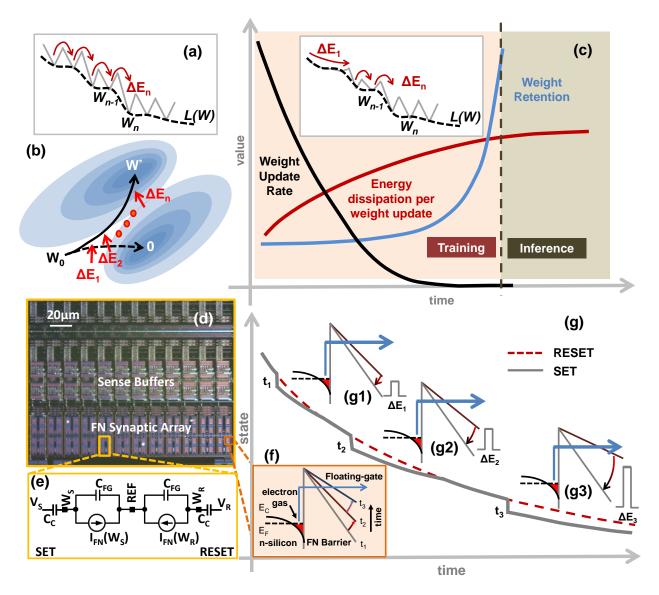

| Figure 3.1: | Motivation and principle of operation for the proposed synaptic memory device                              | 44 |

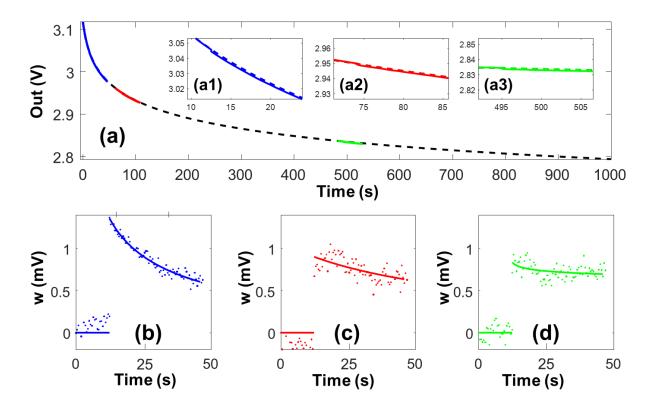

| Figure 3.2: | Adaptive response of FNDAM                                                                                 | 47 |

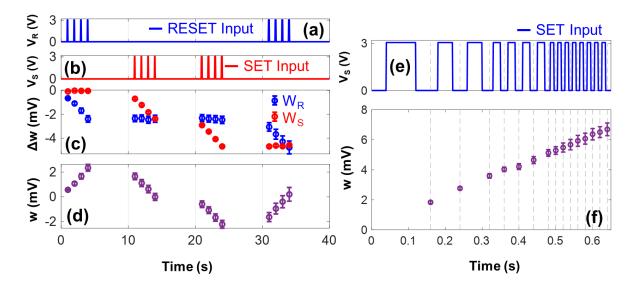

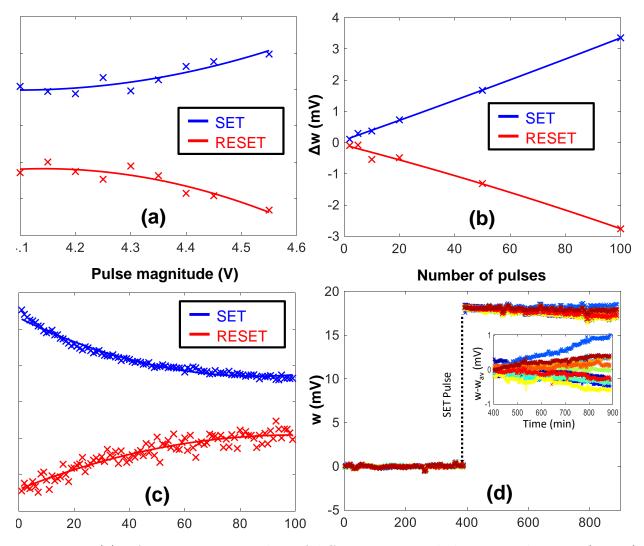

| Figure 3.3: | FNDAM memory update characterization                                                                       | 49 |

| Figure 3.4: | FNDAM device characterization                                                                              | 50 |

| Figure 3.5: | Synaptic memory for neuromorphic applications                                                              | 52 |

| Figure 3.6: | Synaptic memory for deep neural network tasks                                                              | 53 |

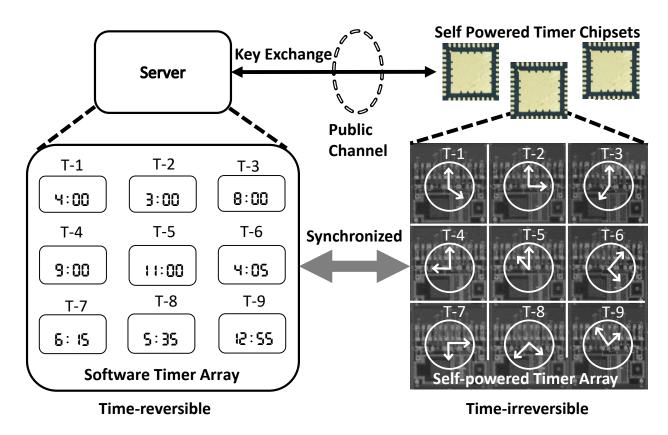

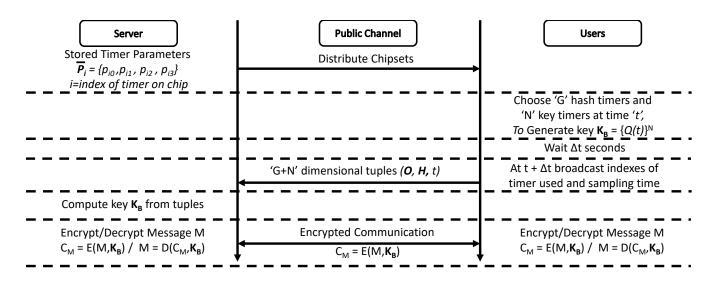

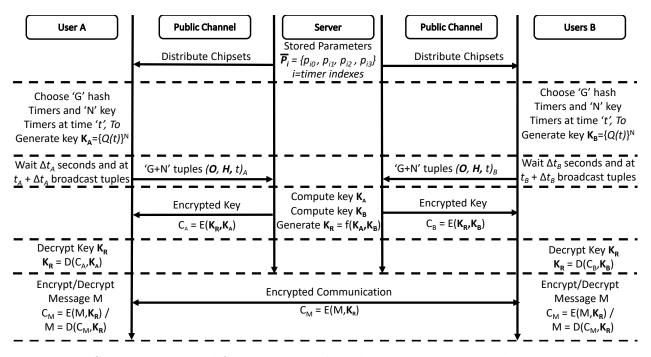

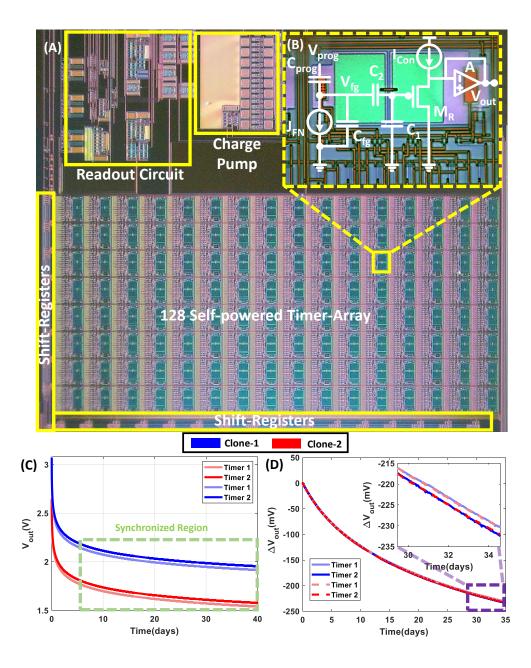

| Figure 4.1: | Framework for SPoTKD protocols                                                                             | 66 |

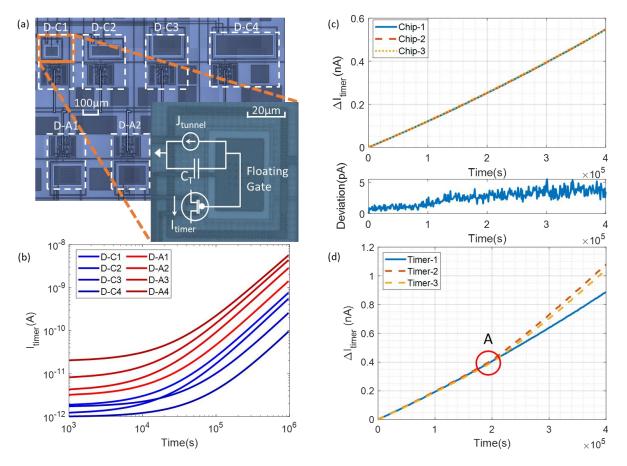

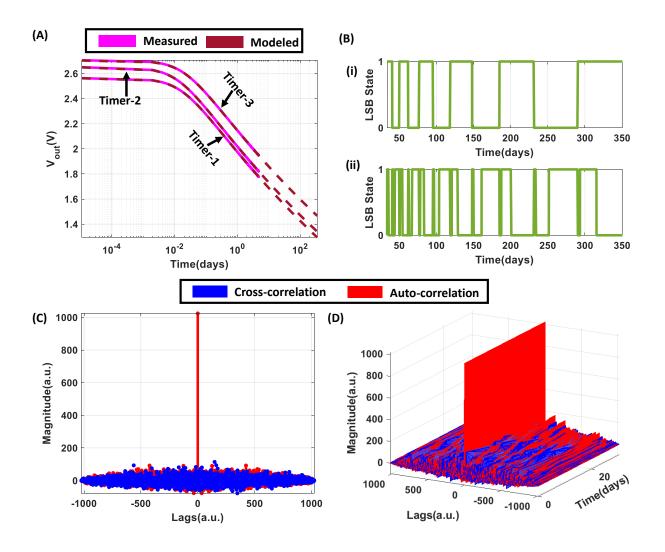

| Figure 4.2: | Measured results for FN-timers across multiple junctions and dies                                          | 69 |

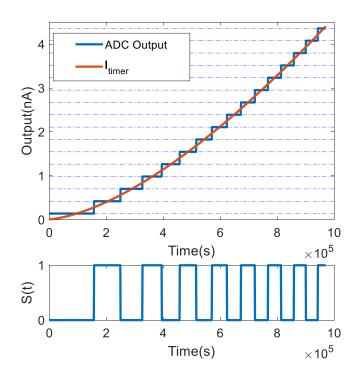

| Figure 4.3:  | Dynamic binary state $s(t)$ of a timer generated after the analog current is<br>read-out with an ADC                       | 72  |

|--------------|----------------------------------------------------------------------------------------------------------------------------|-----|

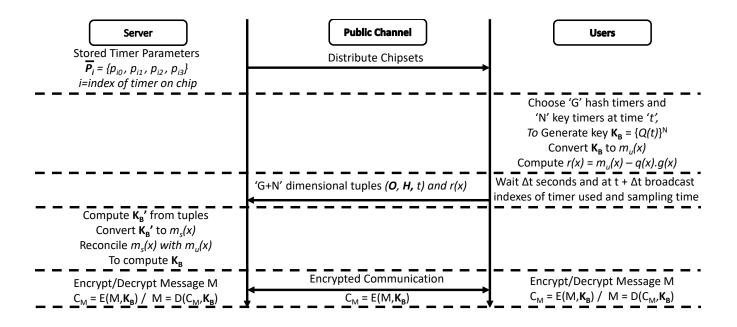

| Figure 4.4:  | Basic SPoTKD protocol between the server and a user                                                                        | 74  |

| Figure 4.5:  | SPoTKD protocol for exchanging keys between two users with the server acting as a trusted third party.                     | 76  |

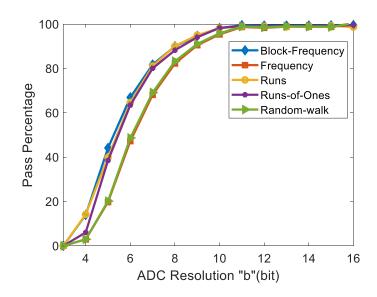

| Figure 4.6:  | Pass percentage obtained using the NIST randomness test suite applied to the keys generated using the SPoTKD protocol      | 77  |

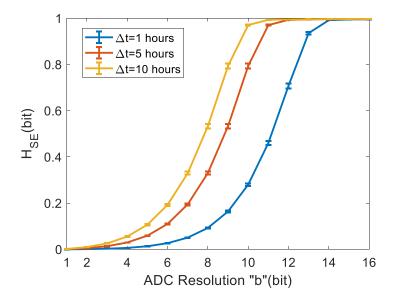

| Figure 4.7:  | Uncertainty per bit measured for three different waiting periods $\Delta t$                                                | 80  |

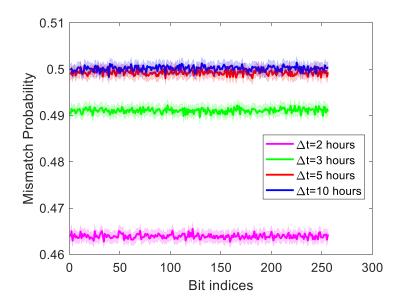

| Figure 4.8:  | Probability that the binary states of timers used in key generation have changed after the waiting period $\Delta t$ hours | 82  |

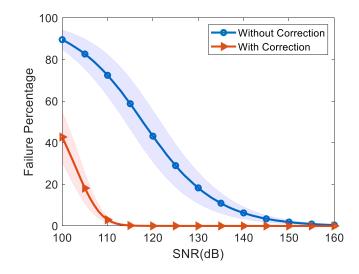

| Figure 4.9:  | Noise robustness of SPoTKD protocol                                                                                        | 88  |

| Figure 4.10: | Modified SPoTKD protocol between a server and a user incorporating error-correction                                        | 89  |

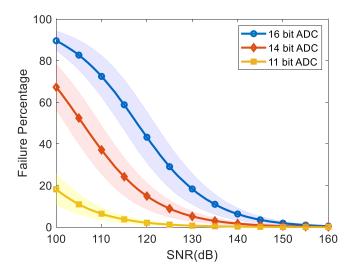

| Figure 4.11: | Performance of the SPoKTD protocol in the presence of noise when<br>error-correction is used                               | 90  |

| Figure 4.12: | Performance of the SPoTKD protocol when using error-correction and different resolution of ADC                             | 91  |

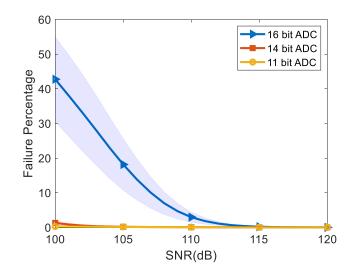

| Figure 5.1:  | Concept figure of an SSPT-based SPRNG                                                                                      | 95  |

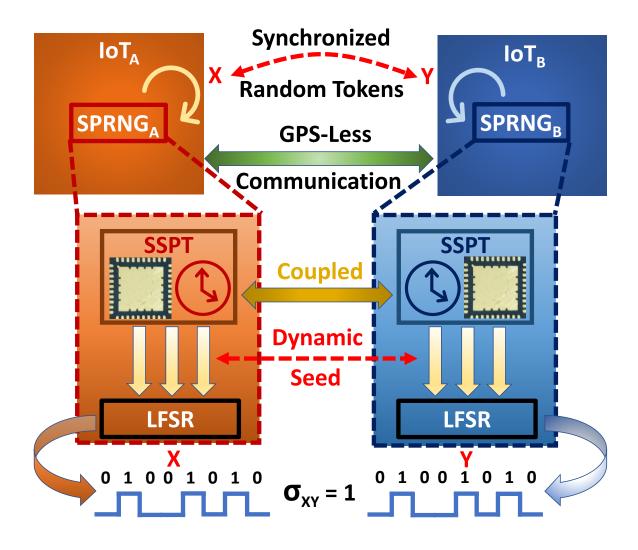

| Figure 5.2:  | Measured dynamics and synchronization results using fabricated SSPT array                                                  | 98  |

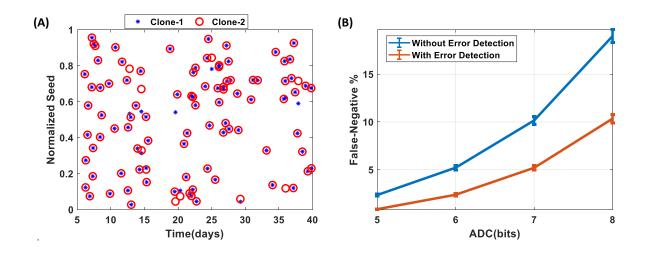

| Figure 5.3:  | Random Seed Generation and Synchronization from fabricated prototypes                                                      | 101 |

| Figure 5.4:  | Correlation between the outputs of LFSR for shifted seed $\ldots \ldots \ldots$                                            | 104 |

| Figure A.1:  | Equivalent circuit model of an FN-synapse                                                                                  | 126 |

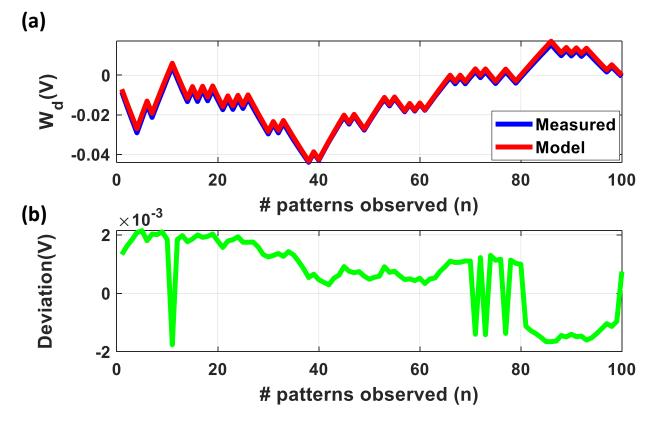

| Figure A.2:  | Comparison of weight $(W_d)$ stored in the FN-synapse and its software model                                               | 128 |

| Figure A.3:  | Comparison between the behavioral model and the analytical model of the FN-synapse                                         | 130 |

| Figure A.4: | Effect of initial plasticity $(W_{c0})$ of FN-synapse                                                                                            | 131 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure A.5: | The architecture of the neural network                                                                                                           | 133 |

| Figure A.6: | Task-wise accuracy comparison                                                                                                                    | 134 |

| Figure A.7: | Effect of network size on overall average accuracy                                                                                               | 135 |

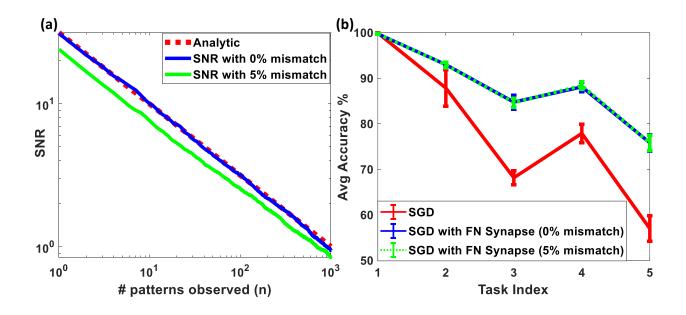

| Figure A.8: | Effect of mismatch in device characteristics                                                                                                     | 136 |

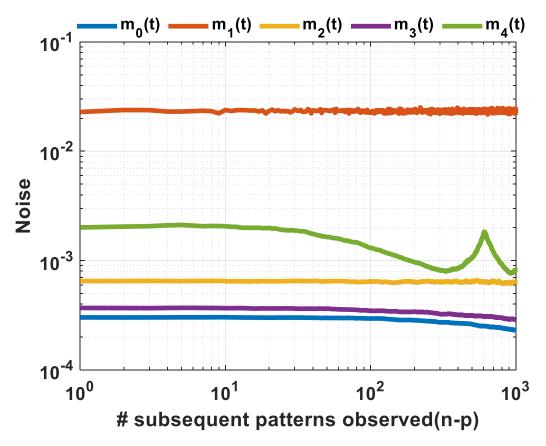

| Figure A.9: | Comparison of noise of FN-synapse networks composed of 1000 synapses following different synaptic models when exposed to 2000 patterns. $\ldots$ | 145 |

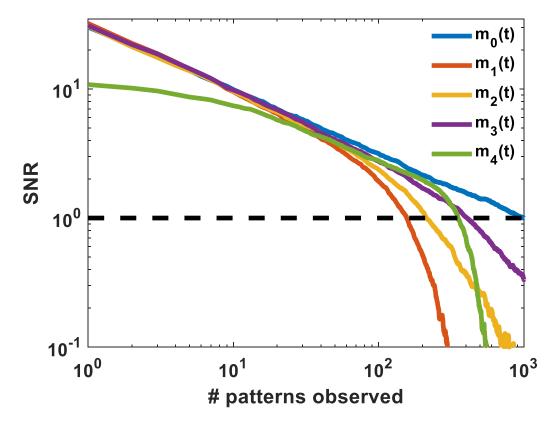

| Figure A.10 | : Comparison of SNR of an empty network of 1000 synapses with different modulation profiles $m(t)$ when exposed to 2000 patterns                 | 146 |

| Figure A.11 | : The SNR in the steady state for an FN-synapse network of size $N = 1000$                                                                       | 147 |

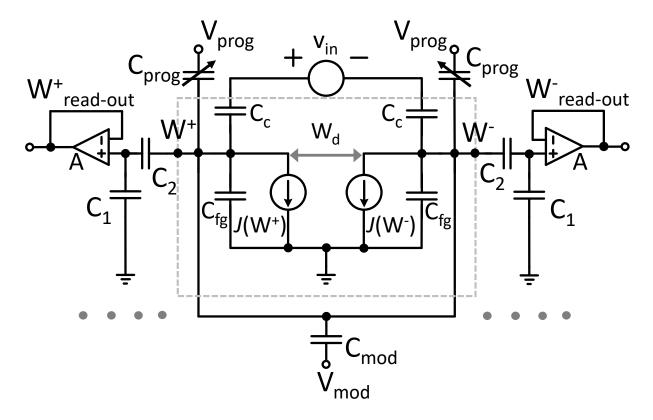

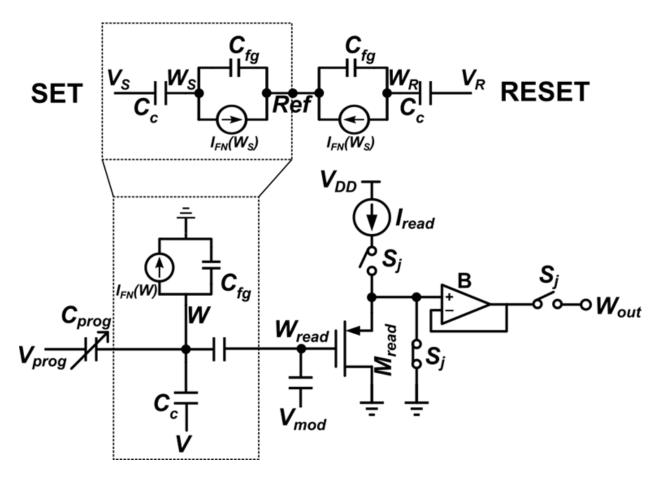

| Figure B.1: | Circuit implementation of the FN-DAM cell with read-out and program-<br>ming circuitry                                                           | 149 |

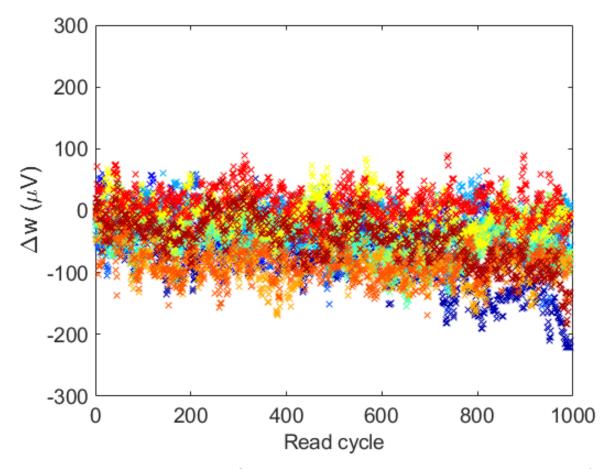

| Figure B.2: | Read disturbance reflected as a change in weight parameters measured from 12 FN-DAM devices                                                      | 150 |

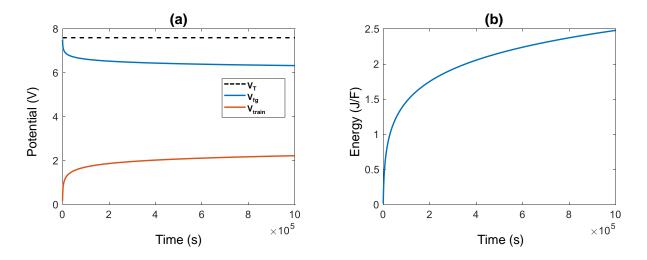

| Figure B.3: | Write energy dissipation estimation                                                                                                              | 151 |

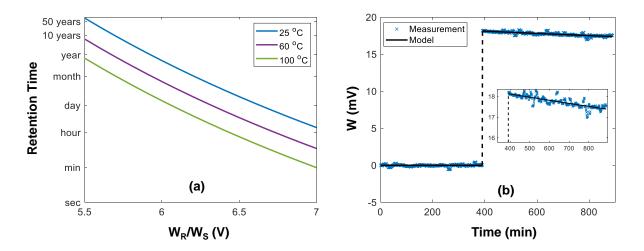

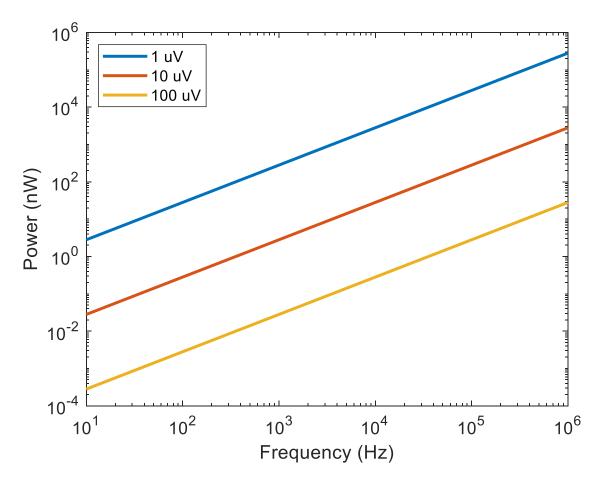

| Figure B.4: | Simulated memory retention time                                                                                                                  | 152 |

| Figure B.5: | Minimum power required to read floating gate voltage as a function of required readout speed. Noise floors are shown in the legend.              | 153 |

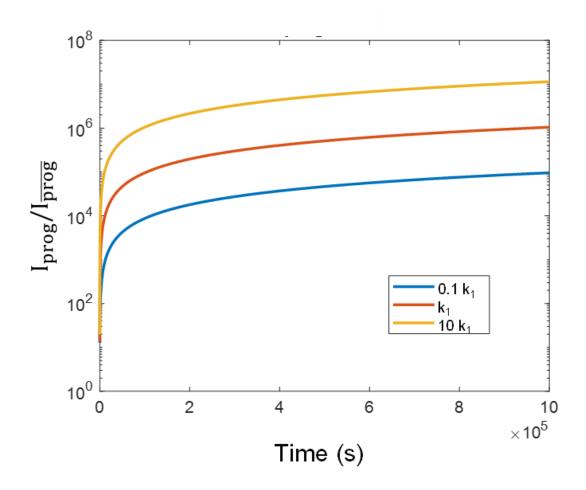

| Figure B.6: | Programming ratio for different $k_1$ parameters which can be controlled by changing the size of tunneling junction.                             | 154 |

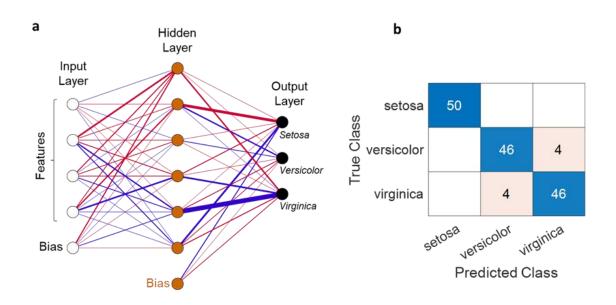

| Figure B.7: | MLP and CNN architecture                                                                                                                         | 155 |

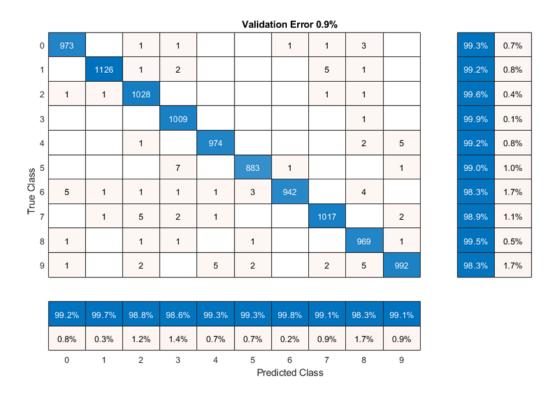

| Figure B.8: | Confusion matrix with for simulated CNN implementation of FN-DAM on MNIST dataset                                                                | 157 |

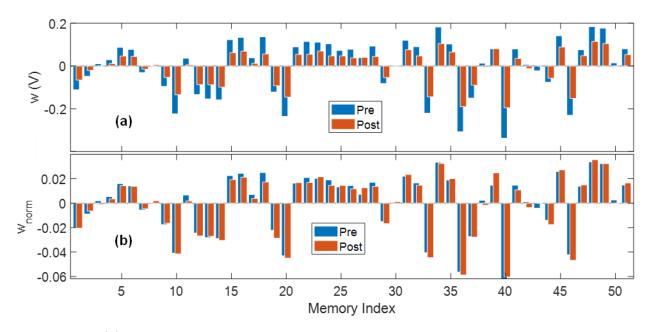

| Figure B.9: | Weight retention pre- and post-baking                                                                                                            | 158 |

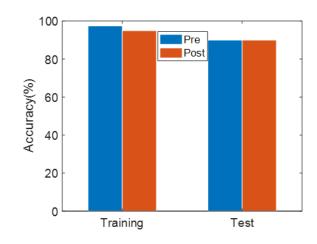

| Figure B.10 | : Training and test accuracy obtained using the pre-bake and post-bake values of weights stored on the FN-DAM.                                   | 159 |

# List of Tables

| Table 4.1: | Performance Comparison between SPoTKD and other state-of-the-art key exchange protocol                                                                       | 87  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 5.1: | Results showing the randomness of the numbers generated by SPRNG when tested with NIST test suites for both cases, a single LFSR and when two LFSR are XORed | 103 |

# Acknowledgments

First, I would like to be thankful to ALLAH for everything that has ever happened to me.

I would also like to thank my advisor Dr.Shantanu Chakrabartty who has always provided me with the necessary knowledge to work towards my goal and whose sincere interest and active involvement in my work have motivated me to complete my thesis. I am also very grateful to my thesis committee members Dr. Netanel Raviv, Dr. Bruno Sinopoli, Dr. Chuan Wang, and Dr. Ning Zhang for their valued advice and interest in my work.

My heartfelt thanks to my lab mates, both former and present ones. They have been both friends and family to me for the past five years. I would especially like to thank Dr. Darshit Mehta who has worked alongside me as a mentor and Subhankar Bose who has been more like a younger brother to me. I will forever be indebted to them for all the help that they provided. Also, a great heartfelt thanks to Dr. Oindrila Chatterjee and Dr. Ahana Gangopadhyay for listening to my whining and guiding me through every tough time. My gratitude towards the Clemens community Kaushik Dutta, Deepangshu Chatterjee, Sneha Dasgupta, Ankita Nandi, and Shreya Shah, all of whom love and support towards me and my family has been unparalleled. St Louis would have never felt like home without the company of these people.

I would also like to be thankful to my parents and elder brother who has believed in me since my childhood and motivated me to pursue my academic life abroad to achieve greatness. I remember that my father always used to say that one day I will get a doctorate degree (if I study properly). Somehow he always knew, even in my early childhood. My special admiration for my little child Nirvaan who has never failed to put a smile on my face when I got too overwhelmed by the work. And lastly, thanks to my partner in life Tasnuva who has been my constant support and has sacrificed a lot in order to let me pursue my dreams.

Mustafizur Rahman

Washington University in St. Louis August 2023 Dedicated to my family who make my world complete

especially Abbu watching me from Heaven.

#### ABSTRACT OF THE DISSERTATION

Theory and Application of Dynamic Analog Memory based on Fowler-Nordheim Quantum Tunneling

by

Mustafizur Rahman Doctor of Philosophy in Electrical Engineering Washington University in St. Louis, 2023 Professor Shantanu Chakrabartty, Chair

Traditionally, memory devices store information in a static manner be it charge-based devices like floating-gates of FeFET or any other method for that matter such as spin-based, electrochemical-based, magnetic-based, etc. But what if memory storage became dynamic in nature and you can control the dynamics? My thesis is based on these premises where I investigate the theory and application of Dynamic Analog Memory (DAM). In my thesis, I answer the questions on how to design such a DAM and what optimal characteristics it needs to have for it to demonstrate advantages over traditional memory devices.

To this end, my thesis first focuses on a self-powered dynamical system that is implemented by depositing charges on an electronically isolated poly-silicon island where the charge leaks through to a semiconductor substrate. The amount of leakage is synchronized not only across multiple tunneling junctions but also across different dies. The dynamical system can be desynchronized by coupling external signals to it. I designed a synaptic memory element that exploits the desynchronization between two dynamical systems to implement an analog memory. First, I characterize the plasticity and the energy required for updating the analog memory. Then I show tunable memory consolidation properties of these synaptic elements using a benchmark random-pattern experiment. Furthermore, I will show that when Fowler-Nordheim quantum tunneling process is used as the leakage mechanism for the DAM, the synaptic elements can exhibit optimal memory consolidation and task-specific based consolidation which can be used in continual learning scenarios. Finally, I also demonstrate that by exploiting the tradeoff between the memory retention period and the energy required for updating the analog memory information can be stored by expending less than 1pj of energy per bit during the training phase of an artificial neural network, four orders of magnitude improvement than conventional memory.

Next, I have implemented a novel class of quantum-secure dynamic encryption key distribution and authentication protocols exploiting the security primitives and synchronization capabilities of these self-powered dynamical systems. The FN-dynamical systems are not only synchronized with each other but also the dynamic profile can be modeled accurately with respect to time. I proposed a key exchange protocol that uses publicly available identical copies of self-powered chipsets where the temporal dynamics on the hardware chipsets are synchronized with its software clone i.e. the analytical model running on a server. I show that the dynamic keys derived from these temporal dynamics meet the National Institute of Standards and Technology (NIST) criteria. I also prove the security of these protocols under a standard model and against different adversarial attacks. I have also investigated the robustness of these protocols using hardware results and propose error-correcting protocols to mitigate noise-related artifacts. Finally, I propose a synchronized pseudo-random number generator (SPRNG) that uses a combination of a fast, low-complexity linear-feedback-shift-register (LFSR) based PRNG and a slow but secure, synchronized seed generator based on self-powered FN-dynamical system. I investigated protocols to periodically and securely generate random bits using the self-powered FN-dynamical system for seeding the LFSR. The time-varying random seeds extend and break the LFSR periodic cycles, thus making it difficult for an attacker to predict the random output or the random seed.

# Chapter 1

# Introduction

We humans have had the need to store information from the beginning of time and as such memory devices have existed long before the modern era. Since the time when human beings started to learn to communicate we have passed down our learnings to the new generation through some means of memory or storage devices. One of the earliest examples of such a memory device dates back to 2500 B.C. when Mesopotamians stored information about their laws, literature, religion, and sciences on impressed clay tablets. However, they soon found out that clay tablets lack the durability that they required. As such they started to etch their inscriptions onto stones as shown in Fig. 1.1 for longer retention of their information [81]. Fast forward a few thousand years and we have a new generation of information storage devices as can be seen in Fig. 1.1 [123]. In 1950 magnetic tape was used for storing information which is one of the oldest technologies for electronic data storage. Gradually, over the next 70 years, we introduced newer generations of electronic storage devices which decreased in form factors but became better at storing more information. Emphasis was once again given to retaining the information as long and as accurately as possible which meant that information was stored in a static manner. Therefore, the underlying principle in information storage throughout the history of memory devices has been the fact that they are static in nature. But what if the memory devices became dynamic meaning information was stored in a dynamic system rather than the conventional static devices? Can we satisfy the general criteria of memory devices, i.e. retention and accuracy, while at the same time exploring new frontiers in modern applications with such a dynamic memory?

My thesis is based on these premises where I investigate the theory and application of Dynamic Analog Memory (DAM). From a biological perspective, it makes sense for memory devices to store information in a dynamic system as it is very well known that biological synapses store memories through multiple electrochemical processes. Therefore, we might be able to take advantage of such a dynamic memory to further our advancement in the Artificial 2500 B.C. - 550 B.C

#### 1980 A.D. – 2023 A.D.

Figure 1.1: Evolution of memory device from being a stone slab in 2500 B.C. to electronic memory devices in modern era

Intelligence (AI) or neuromorphic engineering domain. In addition, when information is stored in a dynamic system, it inherently adds a layer of protection to the stored memory since it will not be enough just to know the state of the memory at any one particular moment to extract the information. Rather one would need to know other details such as the phase or initial condition of the system to decipher what is stored in them. This opens up potential applications in the cryptographic security domain. In my thesis, I answer the questions on how to design such a DAM and what optimal characteristics it needs to have for it to demonstrate advantages over traditional memory devices in the AI and cryptographic security domain.

## 1.1 Dynamic Memory in AI

There is a growing evidence from the field of neuroscience and neuroscience inspired AI about the importance of implementing synapses as a complex high-dimensional dynamical system [15, 46], as opposed to a simple and a static storage element, as depicted in standard neural networks [113]. This dynamical systems viewpoint has been motivated by the hypothesis that complex interactions between plethora of biochemical processes at a synapse produces synaptic metaplasticity [3] and plays a key role in synaptic memory consolidation [80]. Both

these phenomena have been observed in biological synapses [133, 132] where the synaptic plasticity (or ease of update) can vary depending on age and task-specific usage that is accumulated during the process of learning. In literature these long-term synaptic memory consolidation dynamics have been captured using different analytical models with varying degrees of complexity [15, 46, 109, 10, 44, 45]. One such model is the cascade model [15] which has been shown to achieve the theoretically optimal memory consolidation characteristic for benchmark random pattern experiments. However, the physical realization of cascade models as described in [15] uses a complex coupling of dynamical states and diffusion dynamics, which is difficult to mimic and scale *in-silico*. Similar optimal memory consolidation characteristics have been reported in the context of continual learning in artificial neural networks (ANN) where synapses that are found to be important for learning a specific task are consolidated (or become rigid) [69, 26, 82, 136, 78, 8]. As a result, when learning a new task the synaptic weight does not significantly deviate from the consolidated weights, hence, the network seeks solutions that work well for as many tasks as possible. However, these synaptic models are algorithmic in nature and it is not clear if the optimal consolidation characteristics can be naturally implemented on the synaptic device *in-silico*. Also, it is not clear if the consolidation properties of the physical synaptic device can be tuned to achieve different *plasticity-stability* trade-offs and hence can overcome the relative disadvantages of the EWC models. In my thesis, I investigate a simple differential memory device that operates using the physics of Fowler-Nordheim (FN) quantum-mechanical tunneling and show that such an on-device memory element can achieve tunable synaptic memory consolidation characteristics similar to the algorithmic consolidation models.

Another unresolved challenge in the design of energy-efficient machine learning (ML) and neuromorphic processors is the implementation of reliable and scalable synaptic weights or memory [23]. Ideally, the synaptic weights should be "analog" and should be implemented on a non-volatile, and yet easily modifiable storage device [130]. Furthermore, if these memory elements are integrated in proximity with the computing circuits or processing elements, then the resulting compute-in-memory (CIM) architecture [2, 128] has the potential to mitigate the "memory wall" [110, 61, 29] which refers to the energy-efficiency bottleneck in ML processors that arises due to repeated memory access. In most practical and scalable implementations, the processing elements are implemented using CMOS circuits; as a result, it is desirable that the analog synaptic weights be implemented using a CMOS-compatible technology. In literature, several multi-level non-volatile memory devices have been proposed for implementing analog synapses. These include two-terminal memristive devices

such as resistive random-access memories (RRAM) [6], magnetic random-access memories (MRAM) [47], Phase Change Memory (PCM) [22], Spin-Transfer Torque Magnetic RAM (STT-MRAM) [68], Conductive Bridge RAM [63] or the three-terminal devices like the floating-gate transistors [92], ferroelectric field-effect transistor-based memory (FeFET) [39], Charge Trap Memory [129] and Electrochemical RAMs (ECRAM) [120]. In all of these devices, the analog memory states are static in nature, where each of the states needs to be separated from others by an energy barrier  $\Delta E$ . For example, in RRAM devices the state of the conductive filament between two electrodes determines the stored analog value, whereas in charge-based devices like floating-gates or FeFET, the state of polarization determines the analog value. To ensure non-volatile storage, it is critical that the energy-barrier  $\Delta E$ is chosen to be large enough to prevent memory leakage due to thermal-fluctuations and other environmental disturbances. However, the height of the energy barrier  $\Delta E$  also sets the fundamental limit on the energy dissipated to switch between different analog storage states. For example, switching the RRAM memory state requires 100 fJ per bit [131], whereas STT-MRAM requires about 4.5pJ per bit [38]. A learning/training algorithm that adapts the stored weights in quantized steps  $(\ldots, W_{n-1}, W_n, W_{n+1}, \ldots)$  so as to minimize a system-level loss-function L(W) has to dissipate minimum energy of  $(\ldots, \Delta E_{n-1}, \Delta E_n, \Delta E_{n+1}, \ldots)$  for memory updates. Separating the static states by an energy-barrier also allows the learning algorithm to precisely control the parameter retention time (parameter leakage) between subsequent parameter updates, however, this mode of updates does not exploit the physics of learning to optimize for energy-efficiency. In many energy-efficient ML training formulations, and in particular analog ML systems, the loss-function L(W) is represented by an equivalent energy-functional of a physical ML system [76], and learning/training involves a natural evolution of the system dynamics towards the minimum energy (optimal) state based on input stimuli (or equivalently training data). Thus, the physics of the system evolution process selects the minimum energy path toward the desired optimum. A synaptic element that is matched to this system dynamics needs to be adaptive with respect to its memory retention time which can then be traded-off with respect to the energy-dissipation per update. In my thesis I present such a synaptic element that uses dynamical states (instead of static states) to implement analog memory and is matched to the dynamics of ML training.

## 1.2 Dynamic Memory in cryptographic security

Securing information exchange with internet-of-things (IoTs) is becoming ever more important due to the proliferation of these platforms in domains ranging from infrastructure-IoTs [11] to medical-IoTs [12]. In one study [1] it is claimed that around 98% of the IoT data traffic is unencrypted and hence vulnerable to a data breach. Conventional data encryption techniques like RSA are too computationally prohibitive to be universally implemented on these lowresource platforms and reducing the computational complexity makes the approach vulnerable to quantum attacks. For instance, it is estimated in literature that a quantum computer with 8194 logical qubits using Shor's Algorithm would be able to break the Rivest-Shamir-Adleman(RSA)[108] system with a key size of 4096 bits in 229 hours while for Discrete log problem with a key size of 521 bits it would take 55 hours for a quantum computer with 4719 logical qubits, again using the Shor's Algorithm [95]. Symmetric key algorithms like Advanced Encryption Standard (AES-256) can be customized for IoT platforms and are considered to be secure against quantum attack [95], provided the security of the initial key-exchange can be guaranteed. Quantum key distribution (QKD) [16] which is based on the principles of quantum-mechanics, like quantum entanglement [41] or the no-cloning principle [50], [101] could be used to guarantee the security of the initial key-exchange. However, one of the major drawbacks of current state-of-the-art QKD systems is that they require dedicated and specialized peer-to-peer communication links [124], [37], [72], [134]. Not only do these links require careful maintenance and calibration to ensure quantum-coherence, but these systems are also expensive and not portable. Hence, current QKD systems cannot be scaled for internet-scale key distribution [62],[19] and communications involving lightweight IoT devices with resource constraints will still be vulnerable to quantum attacks. Therefore, we need a framework that does not require any modifications to the existing communication infrastructure, can be scaled to a large number of IoTs, and is potentially secure against quantum attacks.

One such approach could be silicon-based chipsets with the capability of integrating billions of transistors and memory elements [32] which can be manufactured on a large scale and at a low-cost [55]. If a physical feature on these chipsets could be exploited to implement a secure one-way function, then a hardware-software approach could be used to support key distribution over public channels. In the literature, a few hardware-software key exchange methods have been proposed. In [36] a hardware-software key exchange technique was proposed that

exploited correlations across chaotic wavepackets in classic optical communications channels. However, the method still requires peer-to-peer connectivity between the users and hence has similar scaling disadvantages as QKD methods. The hardware-software approach proposed in [66] used chaos synchronization to distribute random keys over public channels. However, due to the lack of reliable synchronization, this approach incurs significant errors during decryption. Recently, Physical Unclonable Function(PUF) based hardware-based encryption key distribution has been proposed. A specific variant of this technique, described in [14] as Public Physical Unclonable Function (PPUF) has been used for public-key cryptography and leverages the difficulty of accessing physical information stored on chipsets. However, in PPUF the stored information is static in nature and hence is potentially vulnerable to machine learning attacks [34, 86]. To overcome this limitation, in my thesis, I propose a novel class of symmetric key distribution protocols that leverages basic security primitives offered by low-cost, hardware chipsets containing millions of self-powered micro-dynamical systems. The secret keys are stored in a dynamic manner and the encrypting keys are derived from the temporal dynamics of the device which makes the keys immune to any potential side-channel attacks, malicious tampering, or snooping.

Another aspect of securing wireless communications in internet-of-things (IoT) is the need for both generation and synchronization of random numbers in real-time. Random-numbergenerators (RNGs) are used for producing cryptographic keys which are basically a sequence of random binary numbers. In addition to using a random number as a secure token, for secure communications, there is also a need for synchronization of the tokens between the communicating parties. While asymmetric key encryption could be used to avoid this challenge, they are computationally too expensive to be universally implemented on these resource-constrained devices. On the other hand, a symmetric key encryption scheme can be customized for IoT platforms but requires a shared secret key [57]. Any static information stored on the IoT, such as a SecureID, used as the shared secret will be vulnerable to a machine learning type of attack [86]. Therefore, there is a need for a piece of dynamic information embedded into these IoT devices that can be synchronized in real-time. One such method for achieving this could be using a combination of a timing reference extracted from a global-positioning-system (GPS) and a timing reference generated locally using phasedlocked oscillators. Unfortunately, in many IoT applications, this framework is impractical due to resource constraints together with the fact that many IoT devices may not have access to a GPS signal. To overcome this challenge, in my thesis, I designed an architecture of a synchronized-PRNG (SPRNG) that can be used for generating synchronized pseudorandom binary sequences without the need for any GPS reference signal. The SPRNG uses a combination of a fast, low-complexity LFSR-based PRNG and a slow but secure, synchronized seed generator based on the self-powered dynamic memory elements [137, 91, 104].

## **1.3** Contributions

There are four significant contributions in this dissertation and they are summarized as follows.

- 1: I designed a differential dynamic analog memory device that stores information on a selfpowered micro-dynamic system. I show that when the dynamic system operates using the physics of Fowler-Nordheim (FN) quantum-mechanical tunneling, the fabricated memory device (FNDAM) can achieve optimal memory consolidation characteristics previously only shown in algorithmic consolidation models. This is the first work to show on-device task-specific memory consolidation properties which outperforms other algorithms when used in continual learning application. I have also characterized the memory capacity of an artificial neural network based on FNDAM and showed that on-device memory elements can achieve the theoretical limits.

- 2: I have investigated the energy-efficiency imbalance between the training and the inference phases observed in neuromorphic learning systems. I have proposed that data retention capacity can then be traded-off with respect to the energy dissipation per update to reduce the energy requirement during the training phase of an artificial neural network. I have shown that the dynamic nature of FNDAM can be exploited to match this profile. I have also performed chip-in-the-loop training with the fabricated FNDAM and have validated that energy usage during the training phase is much lower than other conventional memory. I show that information can be stored by expending less than 1pJ of energy per bit on FNDAM, a four orders of magnitude improvement.

- 3: I designed a novel class of symmetric key distribution protocols that leverages basic security primitives offered by low-cost, hardware chipsets containing millions of synchronized self-powered dynamic systems. I have derived encryption keys from the temporal dynamics of a physical device and showed that the keys are immune to any

potential side-channel attacks, malicious tampering, or snooping. I also show that the derived key-strings can pass the randomness test as defined by the National Institute of Standards and Technology (NIST) suite. The key-strings are then used in two SPoTKD (Self-Powered Timer Key Distribution) protocols that exploit the timer's dynamics as one-way functions: (a) protocol 1 facilitates secure communications between a user and a remote Server; and (b) protocol 2 facilitates secure communications between two users. I have investigated the security of these protocols under the standard model and against different adversarial attacks. Using Monte-Carlo simulations, I also investigate the robustness of these protocols in the presence of real-world operating conditions and propose error-correcting SPoTKD protocols to mitigate these noise-related artifacts.

4: I have designed a synchronized pseudo-random number generator (SPRNG) that uses a combination of a fast, low-complexity linear-feedback-shift-register (LFSR) based PRNG and a slow but secure, synchronized seed generator based on a self-powered dynamic system that has been previously used as time-keeping devices. I have explored protocols to periodically and securely generate random bits using the self-powered timers for seeding the LFSR. I have shown that the time-varying random seeds extend and break the LFSR periodic cycles, thus making it difficult for an attacker to predict the random output or the random seed. Using the National Institute of Standards and Technology (NIST) test suite I verify the randomness of the measured seeds using an ensemble of self-powered timers fabricated in a standard CMOS process and the random bit sequences generated by a software-seeded LFSR.

### 1.4 Organization of this Dissertation

The remaining chapters in this dissertation are organized as follows: Chapter 2 presents the construction of the FNDAM along with the details of the fabricated array of FNDAM. It contains the analytical derivation of consolidation properties of FNDAM which shows FN-tunneling as the optimum leakage process. It shows simulated results that conform with the derived analytical expressions. It also shows results validating the memory capacity of an artificial neural network based on FNDAM. Finally, it shows the results of the application of FNDAM in continual learning scenarios. The results in this chapter are based on [104]. **Chapter 3** builds up on the previous chapter and discusses the application of FNDAM regarding the energy efficiency of an artificial neural network during the training phase. It presents the argument for a tradeoff between memory retention and the energy barrier for a memory update in the training phase. It characterizes the weight update of FNDAM in response to various inputs. It includes details of a chip-in-the-loop training and corresponding results showing energy-efficiency balance between the training and the inference phases. Finally, it compares the energy usage of FNDAM with resistive random-access memories (RRAM) for training a deep neural network. The results in this chapter are based on [91].

**Chapter 4** presents the application of an FN-dynamical system in the cryptographic key exchange domain. The framework for the key exchange protocol is first described. After that, it discusses the unique features of an on-device FN-dynamical system i.e. security primitives which are then exploited to design a key exchange protocol called Self- Powered Timer Key Distribution (SPoTKD). It also contains the security analysis of SPoTKD under the standard model. The performance of SPoTKD is then compared with other state-of-the-art key exchange protocols. It also presents the noise robustness of the framework and explores an error correction version of SPoTKD. The results in this chapter are based on [106].

**Chapter 5** presents the concept of the synchronized pseudo-random number generator (SPRNG). It shows the complete system-on-chip prototype array of synchronized self-powered timers (SSPT) to generate dynamic random seeds for the LFSR. It also presents a secure seed exchange protocol for the SPRNG system. Measured results for random seed generation and synchronization from fabricated prototypes are shown. It also contains a statistical analysis of the random number generated using the NIST test suite. The results in this chapter are based on [105].

**Chapter 6** presents a summary of this research, along with key contributions of this dissertation and potential directions for future research.

# Chapter 2

# Synaptic Memory Consolidation using FN-tunneling

This chapter introduces the concept of differential dynamic analog memory based on FNtunneling along with the topic of memory consolidation. It explores how to achieve on-device synaptic memory consolidation using FNDAM. Since FNDAM was used primarily as a synaptic memory element in this chapter, it is thus being referred to as FN-synapse for the rest of the chapter. This chapter has supplemental information which is included in Appendix A. This chapter is based on the published work [104].

## 2.1 Introduction

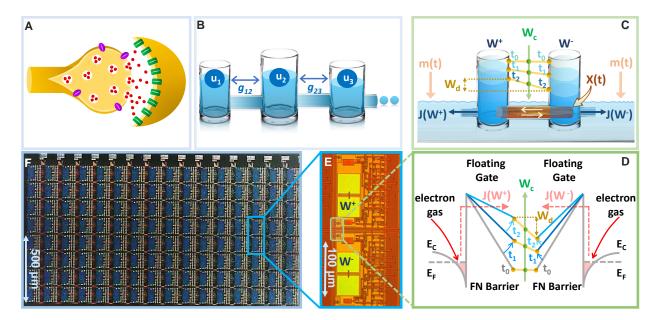

There is a growing evidence from the field of neuroscience and neuroscience-inspired AI about the importance of implementing synapses as a complex high-dimensional dynamical system [15, 46], as opposed to a simple and static storage element, as depicted in standard neural networks [113]. This dynamical systems viewpoint has been motivated by the hypothesis that complex interactions between the plethora of biochemical processes at a synapse (illustrated in Fig. 2.1(a)) produces *synaptic metaplasticity* [3] and plays a key role in *synaptic memory consolidation* [80]. Both these phenomena have been observed in biological synapses [133, 132] where the synaptic plasticity (or ease of update) can vary depending on age and task-specific usage that is accumulated during the process of learning. In literature, these long-term synaptic memory consolidation dynamics have been captured using different analytical models with varying degrees of complexity [15, 46, 109, 10, 44, 45]. One such model is the cascade model [15] which has been shown to achieve the theoretically optimal memory consolidation characteristic for benchmark random pattern experiments. However, the physical realization of cascade models as described in [15] uses a complex coupling of dynamical states and

diffusion dynamics (an example illustrated in Fig. 2.1(b) using a reservoir model), which is difficult to mimic and scale *in-silico*. Similar optimal memory consolidation characteristics have been reported in the context of continual learning in artificial neural networks (ANN) where synapses that are found to be important for learning a specific task are consolidated (or become rigid) [69, 26, 82, 136, 78, 8]. As a result, when learning a new task the synaptic weight does not significantly deviate from the consolidated weights, hence, the network seeks solutions that work well for as many tasks as possible. However, these synaptic models are algorithmic in nature and it is not clear if the optimal consolidation characteristics can be naturally implemented on the synaptic device *in-silico*. Also, it is not clear if the consolidation properties of the physical synaptic device can be tuned to achieve different *plasticity-stability* trade-offs and hence can overcome the relative disadvantages of the EWC models. In this work, we report that a simple differential device that operates using the physics of Fowler-Nordheim (FN) quantum-mechanical tunneling can achieve tunable synaptic memory consolidation characteristics similar to the algorithmic consolidation models. The operation of the synaptic device, referred to in this chapter as the FN-synapse, can be understood using a reservoir model as shown in Fig. 2.1 (c)). Two reservoirs with fluid levels  $W^+$  and  $W^-$  are coupled to each other using a sliding barrier X. The barrier is used to control the fluid flow from the respective reservoirs into an external medium. The respective flows, which are modeled by functions  $J(W^+)$  and  $J(W^-)$ , at time-instant t are modulated by the position of the sliding barrier X(t) and the level of fluid in the external reservoir m(t). In this reservoir model, the synaptic weight is stored as  $W_d = \frac{1}{2}(W^+ - W^-)$  whereas  $W_c = \frac{1}{2}(W^+ + W^-)$  serves as an indicator of synaptic usage with respect to time.

In the Methods section we show that for a synapse based on a general differential reservoir model (without making assumptions on the nature of the flow function J(.)) the synaptic weight  $W_d$  evolves in response to the external input X(t) according to the coupled differential equation

$$\frac{dW_d}{dt} = -r(t)W_d + X(t) \tag{2.1}$$

where

$$r(t) = \frac{d^2 W_c}{dt^2} \left(\frac{dW_c}{dt}\right)^{-1}$$

(2.2)

Figure 2.1: :(A) An illustration of a biological synapse with different coupled biochemical processes that determine synaptic dynamics (B) physical realization of the cascade model reported in [15] that captures the consolidation dynamics using fluid in reservoirs  $u_k$  that are coupled through parameters  $g_{kj}$ . (C) illustration of the FN-synapse dynamics using a differential reservoir model and its state at time-instants  $t_0, t_1$ , and  $t_2$ ;(D) Energy-band diagram to show the implementation of the reservoir model in (C) using the physics of Fowler-Nordheim quantum-mechanical tunneling where a single synaptic element (as shown in (E)) which stores the weight  $W_d$  as the differential charge stored between each tunneling junction *i.e.*  $W_d = \frac{W^+ - W^-}{2}$  and the common-mode tunneling voltage  $W_c$  as the average of the individual charges *i.e.*  $W_c = \frac{W^+ + W^-}{2}$  and (E) micrograph of a single FN-synapse;(F) Micrograph of an array of FN-synaptic devices fabricated in a standard silicon process.

is a time-varying decay function that models the dynamics of the synaptic plasticity as a function of the history of synaptic activity (or its usage). The usage parameter  $W_c$  evolves according to

$$\frac{dW_c}{dt} = -J\left(W_c\right) + m(t) \tag{2.3}$$

based on the functions J(.) and m(t). Equations 2.1- 2.3 show that the weight  $W_d$  update does not directly depend on the non-linear function J(.) but implicitly through the commonmode  $W_c$ . Furthermore, equation 2.1 conforms to the weight update equation reported in the EWC model [69] where it has been shown that if r(t) varies according to the network Fisher information metric, then the strength of a stored pattern or memory (typically defined in terms of signal-to-noise ratio) decays at an optimal rate of  $1/\sqrt{t}$  when the synaptic network is subjected to random, uncorrelated memory patterns. In Methods, we show that if the objective is to maximize the operational lifetime of the synapse, then equating the time-evolution profile in equation 2.2 to  $r(t) \approx \mathcal{O}(1/t)$  [69] leads to an optimal J(.) of the form  $J(V) \propto V^2 \exp(-\beta/V)$  where  $\beta$  is a constant. The expression for J(V) matches the expression for a Fowler-Nordheim (FN) quantum-mechanical tunneling current [79] indicating that optimal synaptic memory consolidation could be achieved on a physical device operating on the physics of FN quantum-tunneling.

To verify on-device optimal consolidation dynamics we fabricated an array of FN-synapses and Fig. 2.1 (d)-(e) shows the micrograph of the fabricated prototype. In the Methods Section, we show the mapping of the differential reservoir model using the physical variables associated with FN quantum tunneling and Fig. 2.1(f) shows the mapping using an energy-band diagram. Similar to our previous works [137, 138, 106], the tunneling junctions have been implemented using polysilicon, silicon-di-oxide, and n-well layers, where the silicon-di-oxide forms the FN-tunneling barrier for electrons to leak out from the n-well onto a polysilicon layer. The polysilicon layer forms a floating-gate where the initial charge can be programmed using a combination of hot-electron injection or quantum-tunneling [91, 90]. The synaptic weight is stored as a differential voltage  $W_d = \frac{1}{2}(W^+ - W^-)$  across two floating-gates as shown in Fig. 2.1 (f). The voltages on the floating-gates  $W^+$  and  $W^-$  at any instant of time are modified by the differential signals  $\pm \frac{1}{2}X(t)$  that are coupled onto the floating-gates. The dynamics for updating  $W^+$  and  $W^-$  are determined by the respective tunneling currents J(.)which discharge the floating-gates. In the Appendix A Fig. A.1 we describe the complete equivalent circuit for the FN-synapse along with the read-out mechanism used in this work to measure  $W_d$ . The presence of additional coupling capacitors in Fig. S1 provides a mechanism to inject a common-mode modulation signal m(t) into the FN-synapse. We will show in the results section that m(t) can be used to tune the memory consolidation characteristics of the FN-synapse array to achieve memory capacity similar to or better than the cascade consolidation models (with different degrees of complexities) or the task-specific synaptic consolidation corresponding to the EWC model.

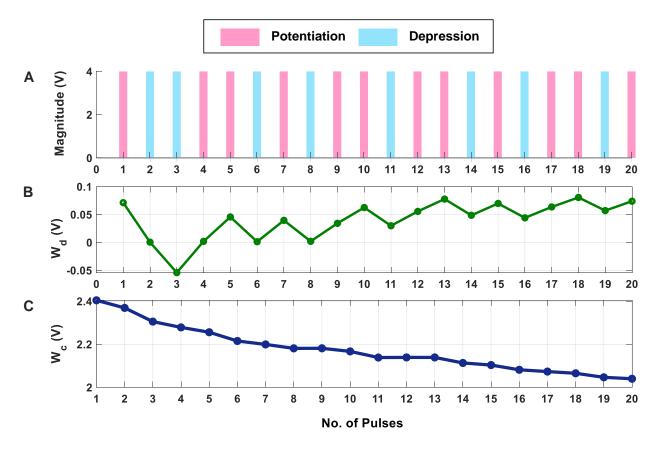

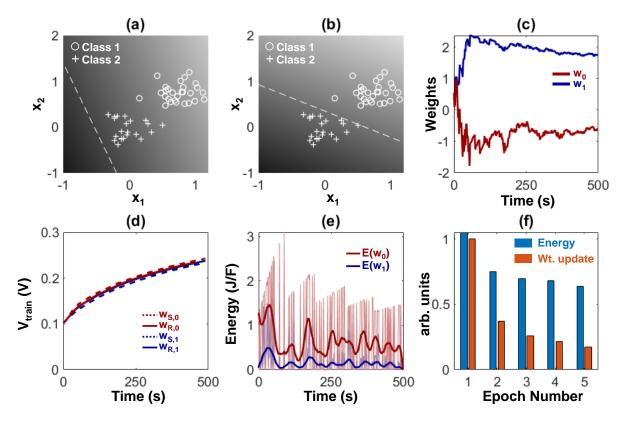

Figure 2.2: (A) A random set of *potentiation* and *depression* pulses of equal magnitude and duration applied to the FN-synapse leading to (B) bidirectional evolution of weight  $(W_d)$  and (C) the corresponding trajectory followed by the common-mode tunneling node  $(W_c)$ .

### 2.2 Results

#### 2.2.1 FN-synapse Characterization

The first set of experiments was designed to understand the *metaplasticity* exhibited by FNsynapses and how the synaptic weight and usage change in response to external stimulation. The charge stored on the floating-gates in the FN-synapse was first initialized according to the procedure described in the Methods Section and in the Appendix A. The tunneling barrier thickness in FN-synapse prototype shown in Fig. 2.1 (d)-(e) was chosen to be greater than 12nm which makes the probability of direct-tunneling of electrons across the barrier to be negligible. The probability of FN-tunneling of electrons across the barrier (as shown in Fig. 2.1 (f)) is reduced to be negligible by lowering the electric potential of the tunneling nodes  $W^+$  and  $W^-$  (see Fig. A.1 in the Appendix A) with respect to the reference ground to be less than 5V. In this state, the FN-synapse behaves as a standard non-volatile memory storing a weight proportional to  $W_d = W^+ - W^-$ . To increase the magnitude of the stored weight a differential input pulse  $\pm \frac{1}{2}X$  is applied across the capacitors that are coupled to the floating-gates (see Fig S1). The electric potential of the floating-gate  $W^-$  is increased beyond 7.5V where the FN-tunneling current  $J(W^-)$  is significant. At the same time the electric potential of the floating-gate  $W^+$  is also pushed higher but  $W^- > W^+$  such that the FN-tunneling currents  $J(W^+) < J(W^-)$ . As a result, the  $W^-$  node discharges at a rate that is faster than the  $W^+$  node. After the input pulse is removed, the potential of both  $W^-$  and  $W^+$  are pulled below 5V and hence the FN-synapse returns to its non-volatile state.

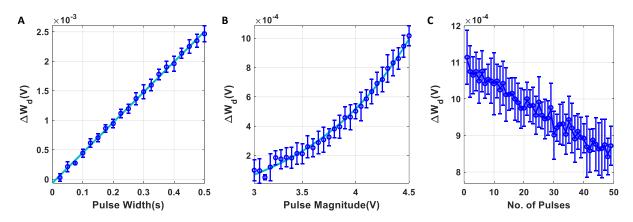

Fig. 2.2 (a)-(c) shows the measured responses which show that an FN-synapse can store both the weight and the usage history. When a series of *potentiation* and *depression* pulses of equal magnitude and duration is applied to the FN-synapse, as shown in Fig. 2.2 (a), the weight stored  $W_d$  evolves bidirectionally (like a random walk) due to the input pulses (see Fig. 2.2 (b)). Meanwhile, the common-mode potential  $W_c$  decreases monotonically with the number of input pulses irrespective of the polarity of the input, as shown in Fig. 2.2 (c). Therefore,  $W_c$  reliably tracks the usage history of the FN-synapse whereas  $W_d$  stores the weight of the synapse. Fig. 2.3 (a) and (b) show the measured weight update  $\Delta W_d$  in response to different magnitudes and duration of the input pulses. For this experiment the common-mode  $W_c = \frac{1}{2}(W^+ + W^-)$  is held fixed. In Fig. 2.3 (a) we can observe that for a fixed magnitude of input voltage pulses (= 4V)  $\Delta W_d$  changes linearly with pulse width. Whereas Fig. 2.3 (b) shows that the updated  $\Delta W_d$  changes exponentially with respect to the magnitude of the input pulses (duration = 100 ms). Thus, the results show that pulse width modulation or pulse density modulation provides more accurate control over the synaptic updates. Furthermore, in regard to energy dissipation per synaptic update pulse width modulation is also more attractive than using pulse magnitude variation. The energy required to write each time on FN-synapse can be estimated by measuring the energy drawn from the differential input source X in Fig. S1 to charge the coupling capacitor  $C_c$  and is given by

$$E_{write} = \frac{1}{2}C_c(X)^2 \tag{2.4}$$

This means that using a smaller pulse magnitude accompanied by longer pulse width is preferable to the other way around in the context of write energy dissipation for the same

Figure 2.3: : (A) Dependence of change in magnitude of weight with change in pulsewidth which follows a linear trajectory defined by y = mx + c (where m = 0.005136 and  $c = -6.227 \times 10^{-5}$ ). (B) Dependence on pulse magnitude of the input pulse which follows an exponential trajectory defined by  $y = c \times exp(ax + b) + d$  (where a = 1, b = -6.611, c = 0.009959 and d = -0.0002142). (C) Change in the magnitude of successive weight updates ( $\Delta W_d$ ) corresponding to a repeated stimulus.

desired change in weight. However, this would come at a cost of slower writing speed. Therefore, a trade-off exists. For the fabricated FN-synapse prototype, the magnitude of the coupling capacitor  $C_c$  is approximately 200f F which leads to 400f J for an input voltage pulse change of 2V across  $C_c$ . For the differential input voltage pulse of 4V, a total of 800f J of energy was dissipated for each potentiation and depression of the synaptic weights. When the common-mode  $W_c$  is not held fixed, irrespective of whether the weight  $W_d$  is increased or decreased (depending on the polarity of the input signal) the common-mode always decreases. Thus,  $W_c$  serve as an indicator of the usage of the synapse. Fig. 2.3 (c) shows the *metaplasticity* exhibited by an FN-synapse where we measured  $\Delta W_d$  as a function of usage by applying successive *potentiation* input pulses of constant magnitude (4V) and width (100ms). Fig. 2.3 (c) shows that when the synapse is modulated with the same excitation successively, the amount of weight update decreases monotonically with increasing usage, similar to the response illustrated in Fig. 2.1 (c) and (f).

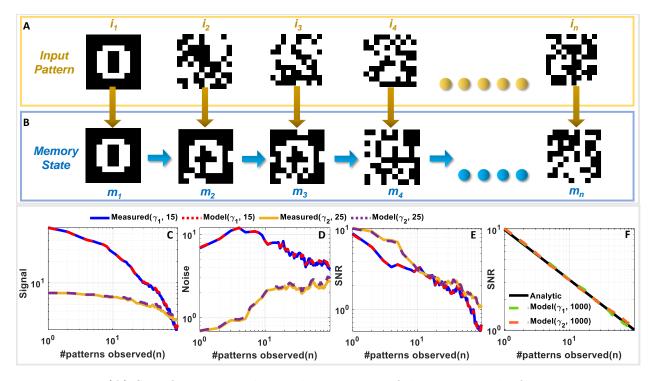

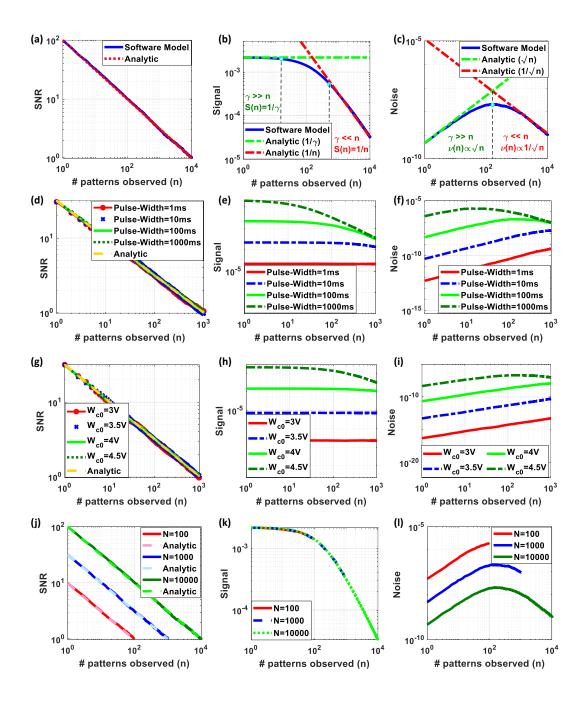

Figure 2.4: : (A) Set of  $10 \times 10$  randomized noise inputs fed to a network of 100 FN-synapses initialized to store an image of the number 0 and (B) the corresponding memory evolution. Comparison of (C) signal strength, (D) noise strength and (E) SNR for a network size of 100 synapses measured using the fabricated FN-Synapse array (shown in Fig. 2.1(F)) over 25 (for  $\gamma_1$ ) and 15 (for  $\gamma_2$ ) Monte-Carlo runs. (F) SNR comparison of the  $\gamma_1$  and  $\gamma_2$  models with the analytical model over 1000 Monte Carlo simulations. The legends associated with the plots are specified as ( $\gamma$ , Number of Monte-Carlo runs).

# 2.2.2 FN-synapse Network Capacity and Memory lifetime without plasticity modulation

The next set of experiments was designed to understand the FN-synaptic memory consolidation characteristics when the array is excited using a random binary input pattern (*potentiation* or *depression* pulses). This type of benchmark experiment is used extensively in memory consolidation studies [15, 69] since analytical solutions exist for limiting cases that can be used to validate and compare the experimental results. A network comprising of NFN-synapses is first initialized to store zero weights (or equivalently  $W^- = W^+$ ). New memories were presented as random binary patterns (N dimensional random binary vector) that are applied to the N FN-synapses through either *potentiation* or *depression* pulses. Each synaptic element was provided with balanced input i.e. an equal number of *potentiation*  and depression pulses. The goal of this experiment is to track the strength of a memory that is imprinted on this array in the presence of repeated new memory patterns. This is illustrated in Fig 2.4 (a) and (b) where an initial input pattern (a 2D image of the number '0' comprising of 10x10 pixels) is written on a memory array. The array is then subjected to images of noise patterns that are statistically uncorrelated to the initial input pattern. It can be envisioned that as additional new patterns are written to the same array, the strength of a specific memory (of the image '0') will degrade. Similar to the previous studies [15, 69] we quantify this degradation in terms of signal-to-noise ratio (SNR). If n denotes the number of new memory patterns that have been applied to an empty FN-synapse array (initial weight stored on the network is zero), then the Methods Section shows that for the  $p^{th}$  update the retrieval memory signal S(n, p) power, the noise  $\nu(n, p)$  power and the SNR(n, p) can be expressed analytically as

$$S^{2}(n,p) = \frac{1}{(n+\gamma)^{2}}; \quad \nu^{2}(n,p) = \frac{n}{N(n+\gamma)^{2}}; \quad SNR(n,p) = \sqrt{\frac{N}{n}}.$$

(2.5)

where  $\gamma > 0$  is a device parameter that depends on the initialization condition, material properties, and duration of the input stimuli.

Equation 2.5 shows that the initial SNR is  $\sqrt{N}$  and the SNR falls off according to a power-law decay with a slope of  $\frac{1}{\sqrt{n}}$ . Like previous consolidation studies [15] we will assume that a specific memory pattern is retained as long as its SNR exceeds a predetermined threshold (unity in this experiment). Therefore, according to equations 2.5 the network capacity and memory lifetime for FN-synapse scales linearly with the size of the network N when the initial weight across all synapses is zero. We verified the analytical expressions in equation 2.5for a network size of N = 100 using results measured from the FN-synapse chipset. Details of the hardware experiment are provided in the Methods. Fig. 2.4 (c), (d), and (e) shows the retrieval signal, noise, and SNR obtained from the fabricated FN-synapse network for two different values of  $\gamma$ . We observe that the SNR obtained from the hardware results conforms to the analytical expressions relatively well. The slight differences can be attributed to the Monte-Carlo simulation artifacts (only 25 and 15 iterations were carried out). In Fig. S3 we show verification of these analytic expressions using a behavioral model of the FN-synapse which mimics the hardware prototype with great accuracy (as shown in Fig. S2). Details on the derivation of FN-synapse model are provided in the Methods Section. The simulated results in Fig. 2.4 (c), (d), and (e) verify that results from the software model can accurately track the hardware FN-synapse measurements for both values of  $\gamma$  when subjected to the same stimuli. Therefore, FN-synapse and its behavioral model can be used interchangeably. The results in Fig. 2.4 (f) also show that when the number of iterations on the Monte-Carlo simulation is increased (1000 iterations), the simulated SNR closely approximates the analytic expression. This verifies that hardware FN-synapse is also capable of exactly matching the optimal analytic consolidation characteristics. Fig. 2.3 (c) shows the measured evolution of weights stored in the FN-synapse where initially the weights grow quickly but after a certain number of updates settle to a steady value irrespective of new updates. This implies that the synapses have become rigid with an increase in their usage. This type of memory consolidation is also observed in EWC models which have been used for continual learning. However, note that, unlike EWC models that need to store and update some measure of Fisher information, whereas, here the physics of the FN-synapse device itself can achieve similar memory consolidation without any additional computation.

#### 2.2.3 Plasticity modulation of FN-Synapse Models

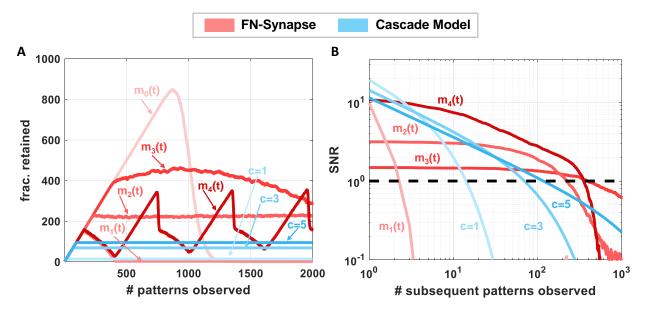

In our next set of experiments, we verified that the plasticity of FN-synapses can be adjusted to mimic the consolidation properties of both EWC and steady-state models (such as cascade models). While the EWC model only allows for the retention of old memories, steadystate/cascade models allow for both memory retention and forgetting. As a result, these models avoid *blackout catastrophe* whereas an EWC network is unable to retrieve any previous memories or store new experiences as the network approaches its capacity. Steady-state models allow the network to gracefully forget old memories and continue to remember new experiences *indefinitely*. For an FN-synapse network, a coupling capacitor in each synapse (shown in Fig. S1) which is driven by a global voltage signal  $V_{mod}(t)$  (which produces  $m(t) = \frac{dV_{mod}(t)}{dt}$ ) can control the plasticity of the FN-synapse to mimic the characteristics of a steady-state model. Details of the modified FN-synapse achieving a steady-state response are provided in the Methods Section. To understand and compare the blackout catastrophe in FN-synapse models with a steady-state model e.g. the cascade model we define the metric #patterns.retained as the total number of memory patterns whose SNR exceeds 1 at any given point of time. The # patterns. retained for FN-synapse network with modulation profiles  $m_0(t)$ ,  $m_1(t)$ ,  $m_2(t)$ ,  $m_3(t)$  and  $m_4(t)$  of size N = 1000 is shown in Fig. 2.5 (a) together with those for cascade models of different levels of complexity [15] (denoted by

c = 1, ..., 5). In order to calculate the *#patterns.retained* the SNR resulting from each stimulus was calculated and tracked at every observation to determine the number of such stimuli that had a corresponding SNR greater than unity. The profiles of  $m_1(t)$ ,  $m_2(t)$  and  $m_3(t)$ are produced by changing  $V_{mod}(t)$  at each update as three quarter, half and quarter of the average of  $\Delta W_d$  across all the synapses during the latest update respectively while  $m_0(t)$ is achieved through a constant voltage signal  $V_{mod}(t)$ . We can observe in Fig. 2.5 (a) that the FN-synapse network with  $m_0(t)$  forgets all observed patterns in addition to not forming any new memories as # patterns.retained goes to zero as the network capacity is reached starting from an empty network. Whereas in the case for FN-synapse under  $m_1(t)$  and  $m_2(t)$ modulation profile the *#patterns.retained* reaches a finite value similar to that of the cascade models. This indicates that the FN-synapse network when subjected to plasticity modulation profiles continues to form new memory while gracefully forgetting the old ones. For the  $m_3(t)$  modulation profile the network is slowly evolving and has yet to reach the steady state condition within 2000<sup>th</sup> update. The FN-synapse network under the  $m_4(t)$  modulation profile, which switches between  $m_0(t)$  and  $m_1(t)$  periodically, is in an oscillatory steady-state with the same periodicity as the modulation profile itself. However, note that the network does not suffer from blackout catastrophe and has a variable capacity. This shows that the capacity of the FN-synapse network can also be tuned to the specificity of different applications. From the figure, we also observe that the steady state network capacity for  $m_2(t)$  modulation profile is higher than that of cascade models. Note here that network capacity for cascade models may be increased by increasing the complexities of the synaptic model. Nevertheless, we find that network capacity for FN-synapse is comparable to cascade models of moderate complexities.

In order to understand the plasticity modulation further, we investigated the SNR for patterns introduced to a non-empty network. For this experiment, we tracked the  $1000^{th}$  pattern observed by the network of N = 1000 synapse. Fig 2.5 (b) shows the SNR of this pattern under  $m_1(t) - m_4(t)$  modulation profile along with cascade models of various complexity. Note that the x-axis now represents the age of the stimulus, i.e. the number of patterns observed after the tracked pattern. For the modulation profile  $m_1(t)$  the initial SNR is large, comparable to that of cascade models, but the SNR falls off quickly indicating high plasticity. Whereas for modulation profile  $m_2(t)$  and  $m_3(t)$  the initial SNR is smaller than  $m_1(t)$  but it falls off at a much later time similar to cascade models with high complexities. These SNR profiles for FN-synapse model with modulation  $m_1(t) - m_3(t)$  are similar to that of a constant weight decay synaptic model used in deep learning neural network as a regularization method.

Figure 2.5: : Comparison of (A) no. of patterns retained by networks composed of 1000 synapses following different synaptic models when exposed to 2000 patterns and (B) steady-state SNR of the  $1000^{th}$  update (p = 1000) of networks consisting of 1000 synapses with various synaptic models when exposed to subsequent updates.

On the other hand, the SNR profile for the  $1000^{th}$  pattern under  $m_4(t)$  modulation has both high initial SNR and a large lifetime. However, from Fig 2.5 (b) we observe that the network is in an oscillatory state which indicates that this profile is specific to the  $1000^{th}$  pattern, and if we tracked any other pattern the SNR profile would be different. This is not the case for the cascade models which would consistently have similar SNR profiles irrespective of the pattern that is tracked. Nevertheless, this SNR profile for the FN-synapse model would repeat itself corresponding to the periodicity of the modulation profile. This suggests that the amount of plasticity and memory lifetime for the FN-synapse model is readily tunable and depends on the amount of modulation provided to the network. We have also verified that the synaptic strength of FN-synapse is bounded similarly to that of the cascade models. This can be observed in Fig. S11 which shows that the variance in retrieval signal (Noise) of an FN-synapse network with both constant modulation and time-varying modulations remains bounded. Furthermore, Fig. S12 shows that plasticity modulation indeed introduces a forgetting mechanism as the SNR for different modulation profiles (when tracked from an empty network) starts to fall off earlier than the one without modulation. In addition to different modulation profiles, the plasticity-lifetime tradeoff of the FN-synapse model can also be achieved by varying the parameter  $\gamma$  as shown in Fig S13. Therefore, our synaptic

models can exhibit memory consolidation properties similar to both EWC and steady-state models while being physically realizable and scalable for large networks.

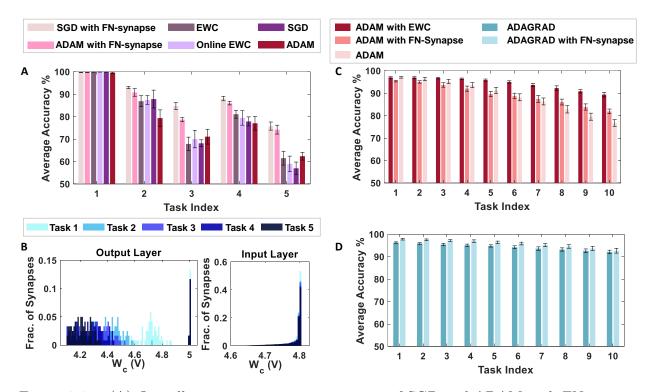

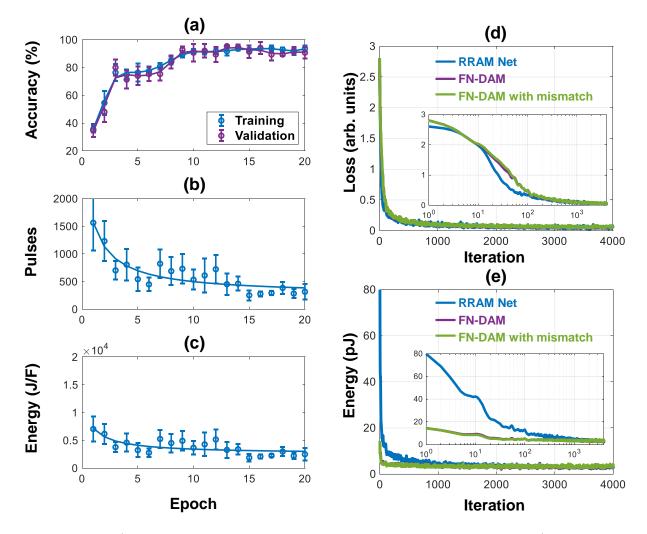

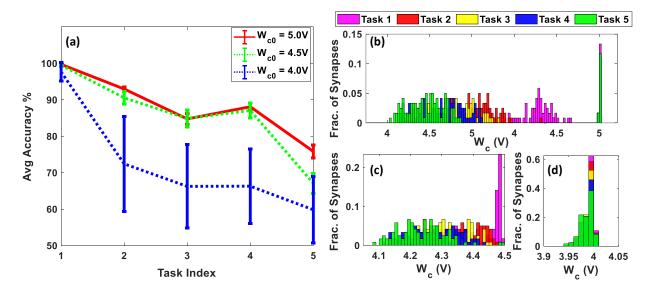

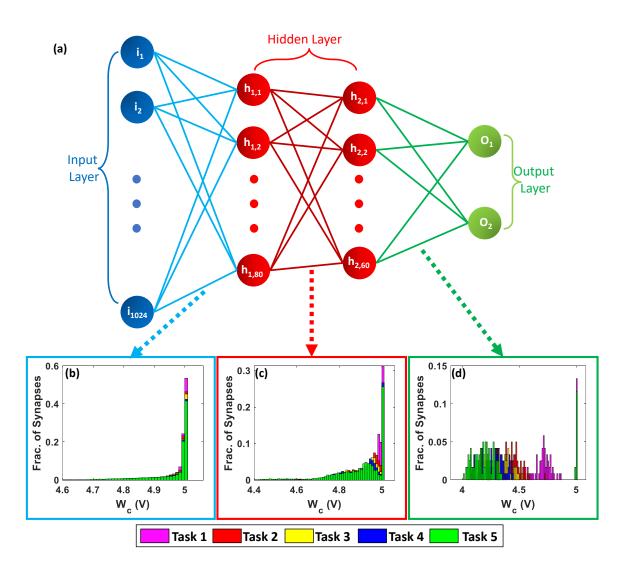

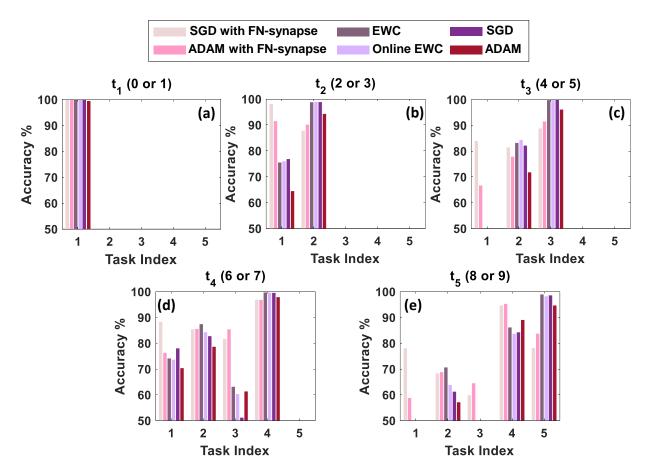

#### 2.2.4 Continual Learning using FN-synapse

The next set of experiments was designed to evaluate the performance of FN-synapse neural network for a benchmark continual learning task. A fully-connected neural network with two hidden layers was trained sequentially on multiple supervised learning tasks. Details of the neural network architecture and training are given in the Methods Section and in Appendix A. The network was trained on each task for a fixed number of epochs and after the completion of its training on a particular task  $t_n$ , the dataset from  $t_n$  was not used for the successive task  $t_{n+1}$ .

The aforementioned tasks were constructed from the Modified National Institute of Standards and Technology (MNIST) dataset, to address the problem of classifying handwritten digits in accordance with schemes popularly used in several continual-learning literature [58]. Also known as incremental domain learning using split-MNIST dataset, each task of this continual learning benchmark dictates the neural network to be trained as a binary classifier which distinguishes between a set of two hand-written digits, i.e. the network is first trained to distinguish between the set [0, 1] as  $t_1$  and is then trained to distinguish between [2, 3] in  $t_2$ , [4, 5] in  $t_3$ , [6, 7] in  $t_4$  and [8, 9] in  $t_5$ . Thus, the network acts as an even-odd number classifier during every task.

Fig. S7 (a)-(e) compares the task-wise accuracy of networks trained with different learning and consolidation approaches. Note here that the absence of a data-point corresponding to a particular approach indicates that the accuracy obtained is below 50%. All the approaches taken into consideration perform equally well at learning  $t_1$  as illustrated in Fig. S7 (a). However, as the networks learn  $t_2$  (see Fig. S7 (b)), the performance of both EWC [69] and online EWC [82] degrade for task  $t_1$  as do the networks with conventional memory using SGD and ADAM. The FN-synapse based networks on the other hand retain the accuracy of task  $t_1$  far better in comparison. This advantage in retention comes at the cost of learning  $t_2$  marginally poorer than others. This trend of retaining the older memories or tasks far better than other approaches continues in successive tasks. Particularly, if we consider the retention of  $t_1$  when the networks are trained on  $t_3$  (see Fig. S7 (c)), it can be observed

Figure 2.6: : (A) Overall average accuracy comparison of SGD and ADAM with FN-synapse, ADAM with EWC and Online EWC, SGD and ADAM with conventional memory. (B) Distribution of the usage profile of weights in the output layer and the input layer of the FN-synapse neural network. Overall Average Accuracy comparison of incremental-domain learning scenarios on the Permuted MNIST dataset using (C)ADAM with EWC, ADAM with FN-Synapse and ADAM with conventional memory and (D)ADAGRAD with conventional memory and ADAGRAD with FN-synapse