## Washington University in St. Louis Washington University Open Scholarship

All Computer Science and Engineering Research

**Computer Science and Engineering**

Report Number: WUCSE-2004-53

2004-09-15

# TCP Processor: Design, Implementation, Operation, and Usage

David V. Schuehler

There is a critical need to perform advanced data processing on network traffic. In order to accom-plish this, protocol processing must first be performed to reassemble individual network packets into consistent data streams representing the exact dataset being transferred between end systems. This task is currently performed by protocol stacks running on end systems. Similar protocol processing opera-tions are needed to process the data on the interior of the network. Given millions of network connections operating on multi-gigabit per second network links, this task is extremely difficult. The TCP-Processor addresses this challenge. It is a hardware circuit designed to... **Read complete abstract on page 2**.

Follow this and additional works at: https://openscholarship.wustl.edu/cse\_research Part of the Computer Engineering Commons, and the Computer Sciences Commons

### **Recommended Citation**

Schuehler, David V., "TCP Processor: Design, Implementation, Operation, and Usage" Report Number: WUCSE-2004-53 (2004). *All Computer Science and Engineering Research*. https://openscholarship.wustl.edu/cse\_research/1026

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160.

This technical report is available at Washington University Open Scholarship: https://openscholarship.wustl.edu/ cse\_research/1026

## TCP Processor: Design, Implementation, Operation, and Usage

David V. Schuehler

### **Complete Abstract:**

There is a critical need to perform advanced data processing on network traffic. In order to accom-plish this, protocol processing must first be performed to reassemble individual network packets into consistent data streams representing the exact dataset being transferred between end systems. This task is currently performed by protocol stacks running on end systems. Similar protocol processing operations are needed to process the data on the interior of the network. Given millions of network connections operating on multi-gigabit per second network links, this task is extremely difficult. The TCP-Processor addresses this challenge. It is a hardware circuit designed to perform TCP stream reassembly operations for 8 million bidirectional TCP connections at OC-48 (2.5 Gbps) data rates. This document takes an indepth look at the TCP-Processor technology, related stream processing applications, and other utilities that support the development of the TCP-Processor.

## TCP-Processor: Design, Implementation, Operation and Usage

David V. Schuehler

Department of Computer Science and Engineering Applied Research Lab Washington University 1 Brookings Drive, Box 1045 Saint Louis, MO 63130

WUCSE-2004-53 http://www.arl.wustl.edu/arl/projects/fpx

September 15, 2004

#### Abstract

There is a critical need to perform advanced data processing on network traffic. In order to accomplish this, protocol processing must first be performed to reassemble individual network packets into consistent data streams representing the exact dataset being transferred between end systems. This task is currently performed by protocol stacks running on end systems. Similar protocol processing operations are needed to process the data on the interior of the network. Given millions of network connections operating on multi-gigabit per second network links, this task is extremely difficult.

The TCP-Processor addresses this challenge. It is a hardware circuit designed to perform TCP stream reassembly operations for 8 million bi-directional TCP connections at OC-48 (2.5 Gbps) data rates. This document takes an in-depth look at the TCP-Processor technology, related stream processing applications, and other utilities that support the development of the TCP-Processor.

## Contents

| 1 | Intro | oduction                                          | 7  |

|---|-------|---------------------------------------------------|----|

| 2 | Envi  | ronment                                           | 9  |

|   | 2.1   | Washington University Gigabit Switch              | 9  |

|   | 2.2   | Field-programmable Port Extender                  | 10 |

|   | 2.3   | NCHARGE                                           | 11 |

|   | 2.4   | FPX-in-a-Box                                      | 11 |

|   | 2.5   | Protocol Wrappers                                 | 11 |

| 3 | Inter | mals                                              | 13 |

|   | 3.1   | Endianness                                        | 15 |

|   | 3.2   | Packet Parameters                                 | 15 |

|   | 3.3   | Flow Control                                      | 16 |

|   | 3.4   | External Memories                                 | 16 |

|   | 3.5   | Configuration Parameters                          | 16 |

|   | 3.6   | TCP Processor                                     | 18 |

|   | 3.7   | TCP Proc                                          | 19 |

|   | 3.8   | TCP Input Buffer                                  | 20 |

|   | 3.9   | TCP Engine                                        | 22 |

|   | 3.10  | State Store Manager                               | 28 |

|   | 3.11  | TCP Routing                                       | 34 |

|   | 3.12  | TCP Egress                                        | 37 |

|   | 3.13  | TCP Stats                                         | 40 |

| 4 | Strea | amExtract                                         | 44 |

|   | 4.1   | StreamExtract_Module                              | 45 |

|   | 4.2   | StreamExtract                                     | 46 |

|   | 4.3   | LEDs                                              | 46 |

|   | 4.4   | Serialization/Deserialization (Endoding/Decoding) | 46 |

|   |             | 4.4.1                                                                                             | TCPSerializeEncode                                                                                      | 50                                                                                                                                                         |

|---|-------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |             | 4.4.2                                                                                             | TCPSerializeDecode                                                                                      | 51                                                                                                                                                         |

| 5 | ТСР         | LiteWr                                                                                            | appers                                                                                                  | 52                                                                                                                                                         |

|   | 5.1         | TCPDe                                                                                             | eserialize                                                                                              | 53                                                                                                                                                         |

|   | 5.2         | TCPRe                                                                                             | eserialize                                                                                              | 53                                                                                                                                                         |

|   | 5.3         | PortTra                                                                                           | acker                                                                                                   | 53                                                                                                                                                         |

|   |             | 5.3.1                                                                                             | PortTracker_Module                                                                                      | 55                                                                                                                                                         |

|   |             | 5.3.2                                                                                             | PortTrackerApp                                                                                          | 55                                                                                                                                                         |

|   |             | 5.3.3                                                                                             | ControlProcessor                                                                                        | 56                                                                                                                                                         |

|   | 5.4         | Scan .                                                                                            |                                                                                                         | 58                                                                                                                                                         |

|   |             | 5.4.1                                                                                             | Scan_Module                                                                                             | 59                                                                                                                                                         |

|   |             | 5.4.2                                                                                             | ScanApp                                                                                                 | 60                                                                                                                                                         |

|   |             | 5.4.3                                                                                             | ControlProcessor                                                                                        | 64                                                                                                                                                         |

|   |             | 5.4.4                                                                                             | StateStore                                                                                              | 66                                                                                                                                                         |

|   |             |                                                                                                   |                                                                                                         |                                                                                                                                                            |

| 6 | Usag        | ge                                                                                                |                                                                                                         | 69                                                                                                                                                         |

| 6 | Usag<br>6.1 | -                                                                                                 | Extract                                                                                                 |                                                                                                                                                            |

| 6 | -           | -                                                                                                 | Extract                                                                                                 | 70                                                                                                                                                         |

| 6 | -           | Stream                                                                                            |                                                                                                         | 70<br>70                                                                                                                                                   |

| 6 | -           | Stream 6.1.1                                                                                      | Compile                                                                                                 | 70<br>70<br>71                                                                                                                                             |

| 6 | -           | Stream<br>6.1.1<br>6.1.2                                                                          | Compile                                                                                                 | 70<br>70<br>71<br>71                                                                                                                                       |

| 6 | -           | Stream<br>6.1.1<br>6.1.2<br>6.1.3                                                                 | Compile                                                                                                 | 70<br>70<br>71<br>71<br>71<br>72                                                                                                                           |

| 6 | -           | Stream<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                                                        | Compile                                                                                                 | <ul> <li>70</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>72</li> </ul>                                                                         |

| 6 | -           | Stream<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6                                      | Compile                                                                                                 | <ul> <li>70</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>72</li> <li>73</li> </ul>                                                             |

| 6 | 6.1         | Stream<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6                                      | Compile .   Generating Simulation Input Files .   Simulate .   Synthesize .   Place & Route .   Setup . | <ul> <li>70</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>72</li> <li>73</li> <li>74</li> </ul>                                                 |

| 6 | 6.1         | Stream<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>Scan &                            | Compile                                                                                                 | <ul> <li>70</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>72</li> <li>73</li> <li>74</li> </ul>                                                 |

| 6 | 6.1         | Stream<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>Scan &<br>6.2.1                   | Compile                                                                                                 | <ul> <li>70</li> <li>70</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>72</li> <li>73</li> <li>74</li> <li>75</li> </ul>                         |

| 6 | 6.1         | Stream<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>Scan &<br>6.2.1<br>6.2.2          | Compile                                                                                                 | <ul> <li>70</li> <li>70</li> <li>70</li> <li>71</li> <li>71</li> <li>71</li> <li>72</li> <li>72</li> <li>73</li> <li>74</li> <li>75</li> <li>75</li> </ul> |

| 6 | 6.1         | Stream<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>Scan &<br>6.2.1<br>6.2.2<br>6.2.3 | Compile                                                                                                 | 70<br>70<br>71<br>71<br>72<br>72<br>73<br>74<br>75<br>75<br>75                                                                                             |

|   | 6.3 | New Applications                | 77 |

|---|-----|---------------------------------|----|

|   |     | 6.3.1 Client Interface          | 78 |

|   | 6.4 | Runtime Setup                   | 78 |

|   | 6.5 | Known Problems                  | 83 |

|   |     | 6.5.1 Xilinx ISE 6.2i           | 83 |

|   |     | 6.5.2 Synplicity 7.5            | 84 |

|   |     | 6.5.3 Outbound IPWrapper Lockup | 85 |

| 7 | Gen | erating Simulation Input Files  | 85 |

|   | 7.1 | I I I I                         | 85 |

|   | 7.1 |                                 | 86 |

|   |     | r r                             |    |

|   | 7.3 |                                 | 88 |

|   | 7.4 | sramdump                        | 88 |

|   | 7.5 | Cell Capture                    | 90 |

|   | 7.6 | Internal Data Captures          | 92 |

| 8 | Con | clusion                         | 92 |

| 9 | Арр | endix                           | 94 |

|   | 9.1 | StatsCollector                  | 94 |

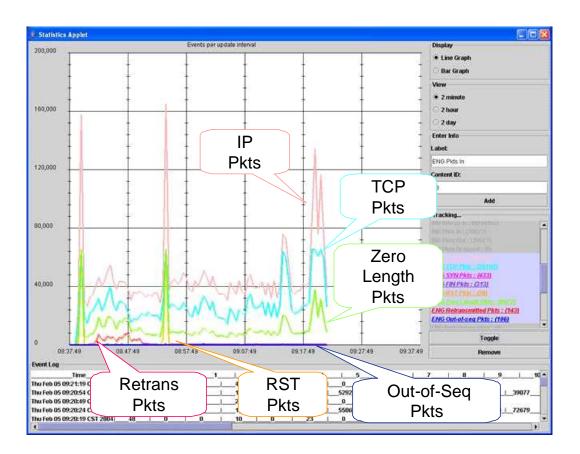

|   | 9.2 | StatApp                         | 96 |

|   | 9.3 | SNMP Support                    | 97 |

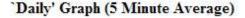

|   | 9.4 | MRTG Charting                   | 98 |

# List of Figures

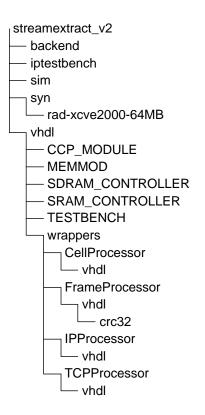

| 1  | Layout of Directory Tree                                        | 8  |

|----|-----------------------------------------------------------------|----|

| 2  | Washington University Gigabit Switch Loaded with Four FPX Cards | 10 |

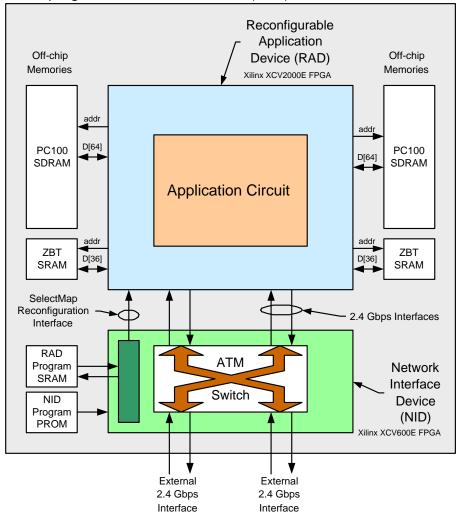

| 3  | Field Programmable Port Extender                                | 12 |

| 4  | Hierarchy of TCP-Processor Components                           | 15 |

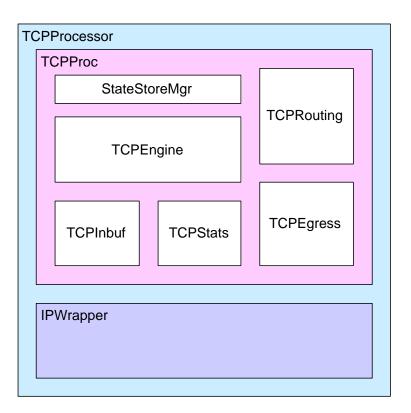

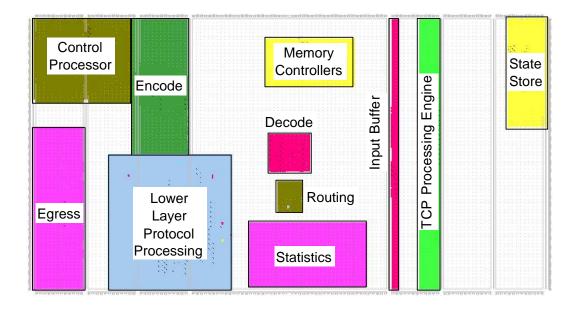

| 5  | TCPProcessor Layout                                             | 19 |

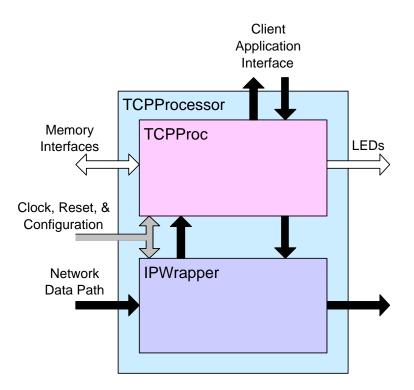

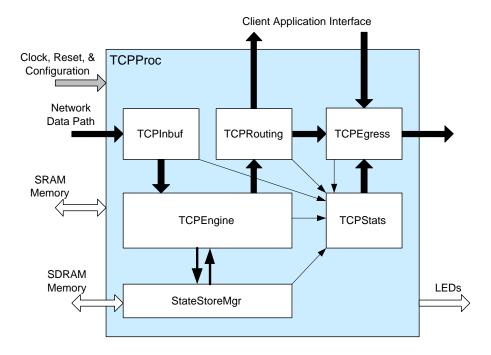

| 6  | TCPProc Layout                                                  | 20 |

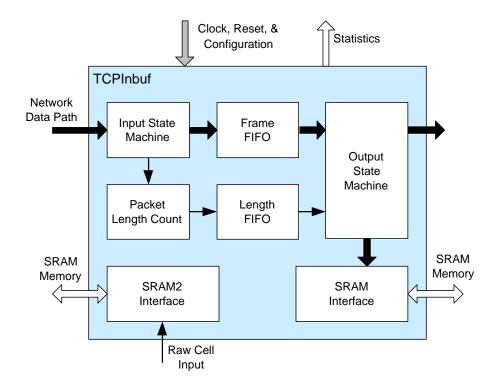

| 7  | TCPInbuf Layout                                                 | 21 |

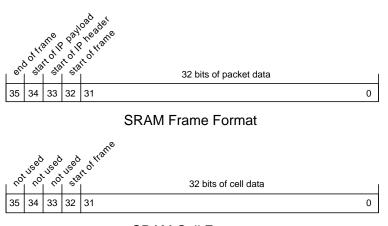

| 8  | SRAM data Formats                                               | 23 |

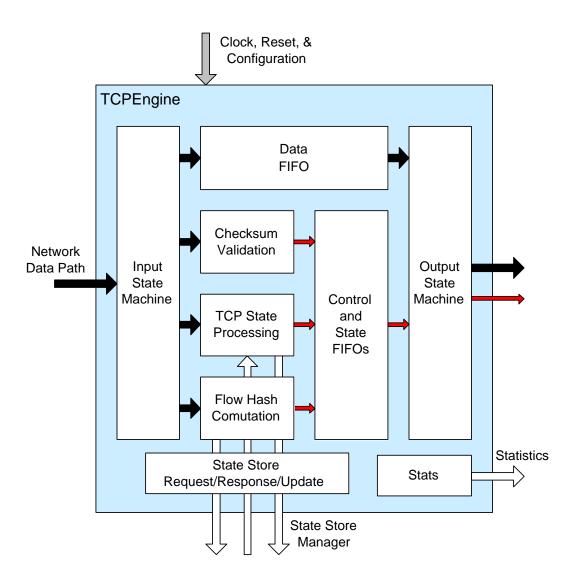

| 9  | TCPEngine Layout                                                | 24 |

| 10 | Control FIFO data format                                        | 27 |

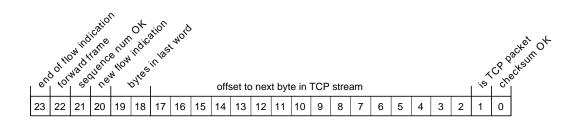

| 11 | Data FIFO data format                                           | 28 |

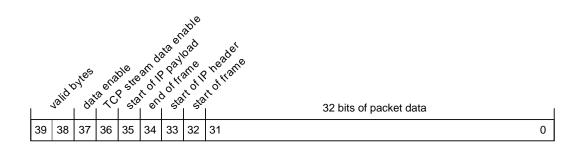

| 12 | Layout of StateStoreMgr                                         | 29 |

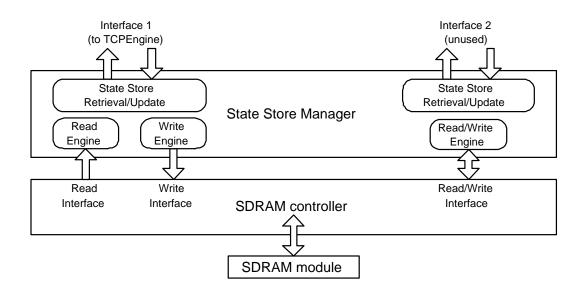

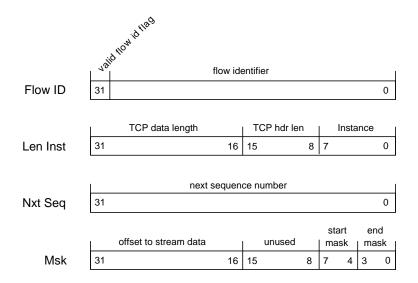

| 13 | Per-Flow Record Layout                                          | 32 |

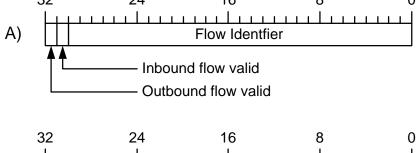

| 14 | Frontside RAM Interface Connections                             | 33 |

| 15 | TCPRouting Component                                            | 35 |

| 16 | TCP Outbound Client Interface                                   | 36 |

| 17 | Flowstate Information                                           | 37 |

| 18 | TCPEgress Component                                             | 38 |

| 19 | TCPEgress FIFO Format                                           | 39 |

| 20 | TCP Inbound Client Interface                                    | 41 |

| 21 | Stats Packet Format                                             | 42 |

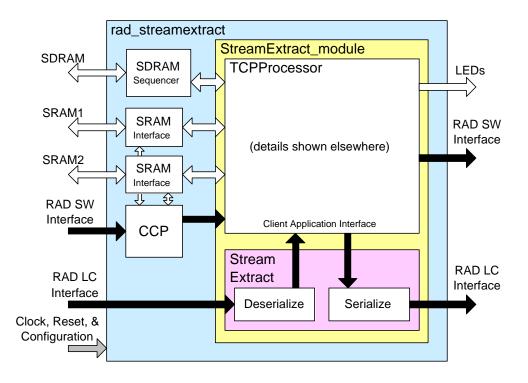

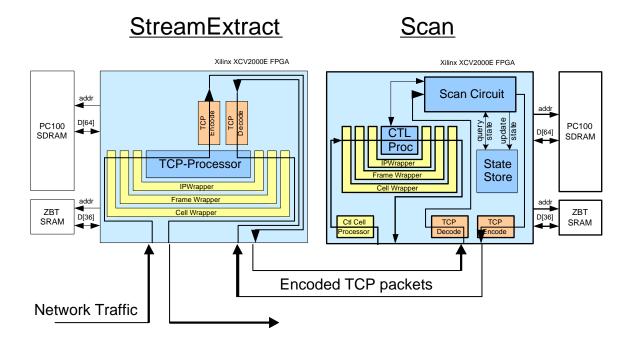

| 22 | StreamExtract Circuit Layout                                    | 45 |

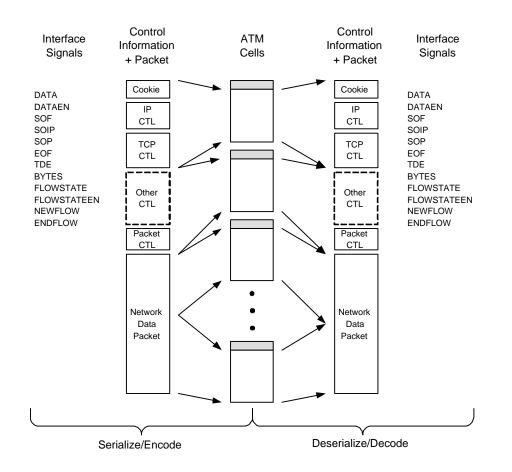

| 23 | Packet Serialization and Deserialization Technique              | 47 |

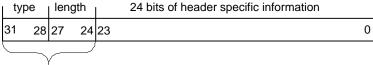

| 24 | Control Header Format                                           | 48 |

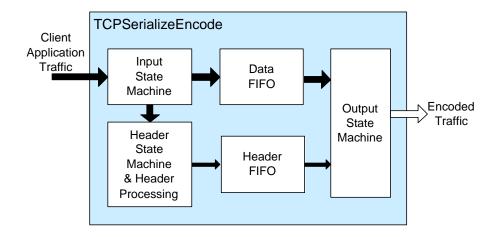

| 25 | TCPSerializeEncode Circuit Layout                               | 50 |

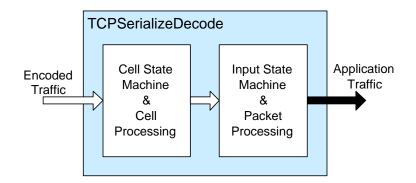

| 26 | TCPSerializeDecode Circuit Layout                               | 52 |

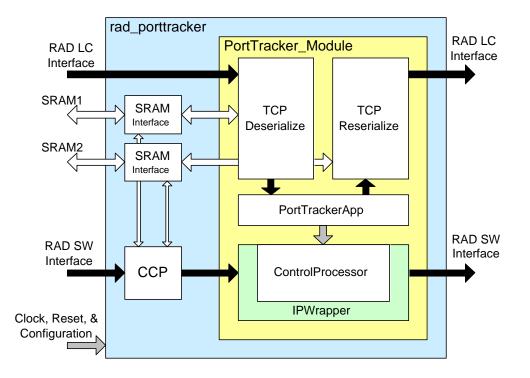

| 27 | PortTracker Circuit Layout                                      | 54 |

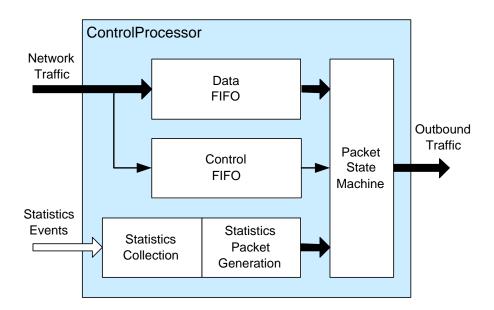

| 28 | PortTracker ControlProcessor Layout                             | 56 |

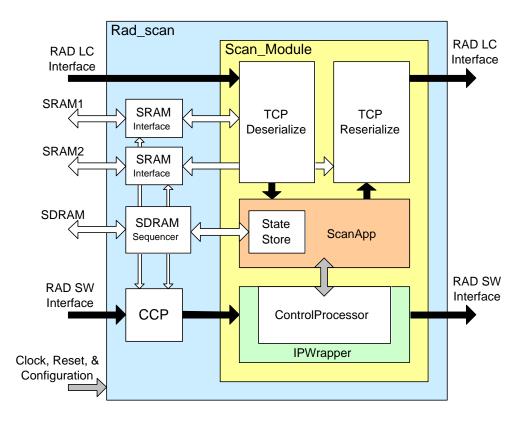

| 29 | Scan Circuit Layout                             | 59 |

|----|-------------------------------------------------|----|

| 30 | ScanApp Circuit Layout                          | 61 |

| 31 | Scan ControlProcessor Layout                    | 65 |

| 32 | Scan Control Packet Format                      | 67 |

| 33 | Layout of StateStore                            | 68 |

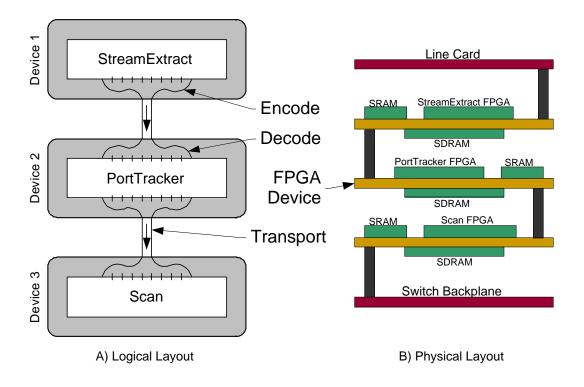

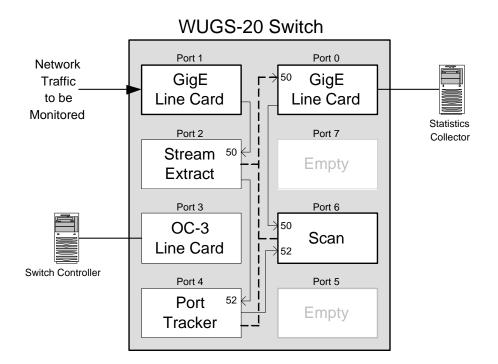

| 34 | Multidevice Circuit Layout                      | 70 |

| 35 | StreamExtract Circuit Layout on Xilinx XCV2000E | 73 |

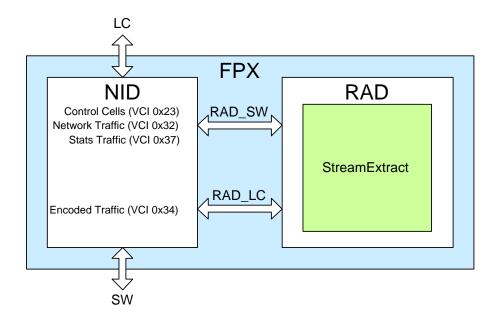

| 36 | StreamExtract NID Routes                        | 74 |

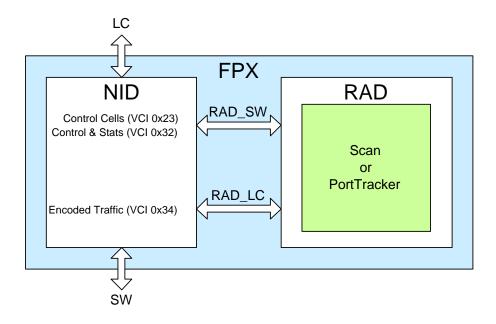

| 37 | Scan/PortTracker NID Routes                     | 77 |

| 38 | Multidevice Circuit Layout                      | 79 |

| 39 | Active Monitoring Switch Configuration          | 80 |

| 40 | Passive Monitoring Switch Configuration         | 82 |

| 41 | Passive Monitoring FPX-in-a-Box Configuration   | 84 |

| 42 | Operation of SRAMDUMP Utility                   | 89 |

| 43 | SRAM data Formats                               | 90 |

| 44 | CellCapture Circuit Layout                      | 91 |

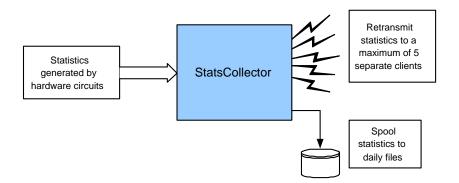

| 45 | StatsCollector Operational Summary              | 95 |

| 46 | Sample StatApp Chart                            | 97 |

| 47 | Sample MRTG Generated Chart                     | 98 |

## **1** Introduction

The TCP-Processor technology was born out of the desire to process Transmission Control Protocol (TCP) [1]-based data streams within extensible networking devices. Initial efforts to process TCP packets in a hard-ware circuit resulted in the development of the TCP-Splitter technology [2]. The TCP-Processor takes the TCP-Splitter technology several steps further and represents a more mature and feature rich implementation of a TCP processing circuit.

This technical report provides detailed information about the TCP-Processor (version 2). The source code and build environment can be retrieved from the URL: http://www.arl.wustl.edu/projects/fpx/fpx\_internal/tcp/source/streamextract\_source\_v2.zip.

Figure 1 illustrates the directory structure for this distribution. All source, make, and project files required to compile, simulate, synthesize and build the StreamExtract circuit are included in this distribution. The StreamExtract circuit contains the TCP-Processor logic and supports multidevice TCP stream processing applications. The standard project layout format common to other FPX group projects is used for this project. The list below gives a brief summary of the contents of each subdirectory in the distribution:

backend- Contains files needed to perform backend simulations.

**iptestbench**- Contains utilities for generating input files used during simulation.

- sim- Contains files necessary to compile and simulate the StreamExtract circuit.

- syn- Contains the Synplicity project used when synthesizing the StreamExtract circuit.

- syn/rad-xcve2000e-64MB- Contains the files required to perform place and route functions. This resultant BIT file will be deposited in this directory.

- vhdl- Contains all VHDL source for the StreamExtract circuit. The top level is contained in the rad\_streamextract.vhd file.

- vhdl/CCP\_MODULE- Contains the source files for the control cell processor. NCHARGE communicates with the CCP to allow remote access to SRAM devices.

- vhdl/MEMMOD- Contains the manufacturer-supplied source files required to simulate the memory devices used on the FPX platform.

- vhdl/SDRAM\_CONTROLLER- Contains Sarang's SDRAM memory controller. This circuit is documented in a technical report [3].

- vhdl/SRAM\_CONTROLLER- Contains the SRAM memory controller. This circuit is documented in a

Figure 1: Layout of Directory Tree

technical report [4].

- **vhdl/TESTBENCH** Contains the testbench simulation environment utilized by ModelSim to reconstruct the environment of the FPX platform when performing simulations.

- vhdl/wrappers/CellProcessor/vhdl- Contains the source for the ATM cell wrapper.

vhdl/wrappers/FrameProcessor/vhdl- Contains the source for the AAL5 frame wrapper.

vhdl/wrappers/IPProcessor/vhdl- Contains the source for the IP wrapper.

vhdl/wrappers/TCPProcessor/vhdl- Contains the source for the TCP-Processor.

From the root directory the **make compile** command will compile the source VHDL files, the **make sim** command will start up ModelSim to perform functional simulation, the **make syn** command will synthesize the VHDL using Synplicity, and the **make build** command will perform place and route functions utilizing Xilinx tools.

Section 2 of this paper provides information about the operational environment of the TCP-Processor and the hardware platform utilized for development, debugging and testing of the circuit. Section 3 describes the internal workings of the TCP-Processor in detail. Section 4 describes the StreamExtract circuit, which contains the TCP-Processor logic and supports multi-device TCP stream processing applications. Section 5 describes the TCPLiteWrappers and applications which utilize these wrappers to implement TCP flow processing applications. Section 6 covers the specific steps necessary to compile, simulate, synthesize, place & route, and run the suite of TCP processing circuits. In addition, information about how to integrate solutions with the TCP-Processor is also provided. Section 7 provides information on various methods for generating simulation input files. Section 8 provides concluding remarks. The Appendix covers associated utilities which store, process, chart, and rebroadcast statistics information generated by the TCP processing circuits described in this document.

## 2 Environment

The Applied Research Laboratory (ARL) at Washington University in St. Louis has a distinguished history of performing high-speed networking research [5]. The TCP-Processor leverages previous research work performed by faculty, staff, and students at this facility[6]. The following subsections briefly describe some of the hardware, software, and circuit designs which were used to support the development of the TCP-Processor.

The TCP-Processor was designed, implemented and tested to operate within the context of the Field-Programmable Port Extender (FPX). While this circuit is not limited to this environment, minor modifications to the TCP-Processor would most likely be required for it to operate on a different hardware platform. For the purposes of this technical report, it is assumed that the FPX platform is the underlying hardware device for the TCP-Processor.

#### 2.1 Washington University Gigabit Switch

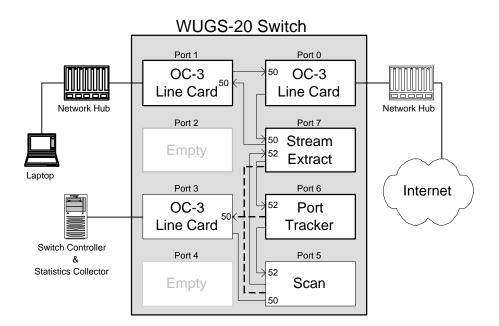

The Washington University Gigabit Switch (WUGS) [7] is an eight port ATM switch interconnected by an underlying switching fabric. Data paths on the switch are 32 bits wide. The backplane of the switch was designed to drive each of the eight ports at a data rate of 2.4 Gbps to achieve an aggregate bandwidth of 20

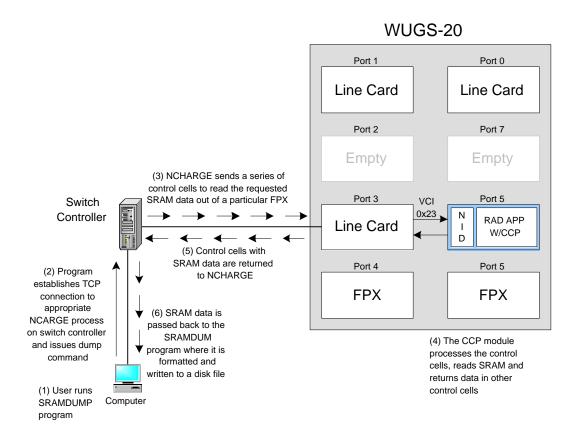

Figure 2: Washington University Gigabit Switch Loaded with Four FPX Cards

Gbps.

Each of the eight ports supports several different types of adapter cards. The current set of adapter cards includes a Gigabit Ethernet line card, a Gigabit ATM line card, an OC3 ATM line card, the Smart Port Card (SPC), the Smart Port Card II (SPC2), and the Field-programmable Port Extender (FPX). The SPC and SPC2 contain a Pentium processor and Pentium III processor respectively, and can execute a version of the Unix operating system which supports software-based packet processing [8]. Figure 2 shows a WUGS switch populated with four FPX cards, two OC-3 line cards, and two GLink line cards.

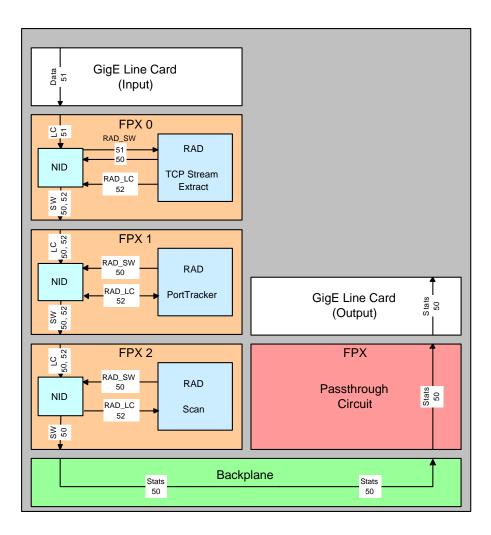

### 2.2 Field-programmable Port Extender

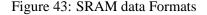

The Field-programmable Port Extender (FPX) [9] is a research platform which supports the processing of high-speed network traffic with reconfigurable devices. All processing on the FPX is implemented in reconfigurable logic with FPGAs. One FPGA on the system is called the Reprogrammable Application Device (RAD) and is implemented with a Xilinx Virtex XCV2000E (earlier models of the FPX use the XCV1000E) [10]. The RAD can be dynamically reconfigured to perform user-defined functions on packets traversing through the FPX. The second FPGA device on the FPX is called the Network Interface Device (NID) and

is implemented with a Xilinx Virtex XCV600E FPGA. The NID, which is statically programmed at power up, controls data routing on the FPX platform and is also responsible for programming the RAD. The system contains five parallel banks of memory that include both Zero Bus Turnaround (ZBT) pipelined Static Random Access Memory (SRAM) for low-latency access to off-chip memory and Synchronous Dynamic RAM (SDRAM) to enable buffering of a gigabyte of data. Network interfaces allow the FPX to interface at speeds of OC-48 (2.4 gigabits per second). The RAD device can be remotely reprogrammed by sending specially configured control cells to the device. A diagram of the components of the FPX platform can be seen in Figure 3 [11].

#### 2.3 NCHARGE

A suite of tools called NCHARGE (Networked Configurable Hardware Administrator for Reconfiguration and Governing via End-systems) remotely manages control and configuration of the FPX platform [12]. NCHARGE provides a standard Application Programming Interface (API) between software and reprogrammable hardware modules. Using this API, multiple software processes can communicate to one or more FPX cards using standard TCP/IP sockets.

#### 2.4 FPX-in-a-Box

The FPX platform can be used either in conjunction with a WUGS switch or independently as part of a standalone solution. The FPX cards have a network interface port on both the top and bottom of the card, enabling stacking of other FPX or line cards under and over them. The FPX-in-a-box system provides a simple backplane which supports two stacks of FPX cards with a line card placed at the top of each stack. The provides a small footprint system which is capable of performing complex network processing at OC-48 data rates without requiring a underlying switch fabric. Systems needing complex flow processing can be implemented by stacking multiple FPX cards and distributing circuits across the multiple FPGA devices.

#### 2.5 **Protocol Wrappers**

FPX cards process Internet packets using a set of Layered Protocol Wrappers [16, 13, 14]. Each protocol wrapper performs processing on a different protocol layer for inbound and outbound traffic. These protocol wrappers create a framework that allows upper layer protocol processing to be isolated from any underlying protocols. The protocol wrapper library includes an ATM Cell wrapper, an AAL5 Frame wrapper, an IP

Figure 3: Field Programmable Port Extender

protocol wrapper and a UDP protocol wrapper. The Cell Wrapper validates the Header Error Checksum (HEC) field in the ATM cell header and performs routing based on the cell's Virtual Channel Identifier (VCI) and Virtual Path Identifier (VPI). The Frame Wrapper performs Segmentation and Reassembly (SAR) operations converting cells into packets and packets back into cells. The IP Wrapper performs processing

of IP packets. The TCP-Processor circuit interfaces with the IP, Frame and Cell Wrappers for processing network traffic.

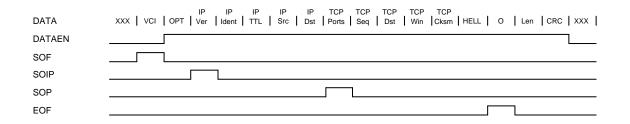

The IPWrapper sends and receives IP packets utilizing a 32-bit wide data bus for carrying data and several associated control signals. These control signals include a start of frame (SOF) signal, a start of IP header (SOIP) signal, a start of payload (SOP) signal, and an end of frame (EOF) signal. Packets themselves can be broken down into five sections as described in Table 1.

| Data            | Control signals   | Comment                                                    |  |

|-----------------|-------------------|------------------------------------------------------------|--|

| ATM VCI         | SOF               | first word of packet                                       |  |

| preamble dataen |                   | zero or more words inserted before the start of the packet |  |

| IP header       | dataen, SOIP, EOF | IP header information                                      |  |

| IP payload      | dataen, SOP, EOF  | IP payload information                                     |  |

| trailer         | dataen            | contains AAL5 trailer fields                               |  |

#### Table 1: IP packet contents

The IPWrapper is hard-coded to process only the traffic that enters on VCI 50 (0x32) or VCI 51 (0x33). Because of this implementation feature, all network traffic processed by the IPWrapper must arrive on VCI 50 (0x32) or VCI 51 (0x33). This includes TCP traffic to be processed by the TCP-Processor and control traffic used to remote command and control various circuit designs. In order to process data on a VCI other than 50 (0x32) or 51 (0x33), VHDL code changes will be required in the lower layered protocol wrappers.

## **3** Internals

The TCP-Processor is a subcomponent of the StreamExtract application which will be discussed in the next section. The TCP-Processor interfaces to the previously mentioned layered protocol wrappers and provides protocol processing for TCP packets. More specifically, the TCP-Processor is concerned with reassembling application data streams from individual TCP packets observed on the interior of the network. This section will focus on the specifics of the TCP-Processor.

The source code for TCP-Processor is located in the directory vhdl/wrappers/TCPProcessor /vhdl found in the streamextract\_source\_v2.zip distribution file. The following VHDL source modules can be found there and comprise the core of the TCP-Processor technology:

- tcpprocessor.vhd- Top level TCP-Processor circuit. The external interface includes configuration parameters, clock and control signals, inbound and outbound 32-bit UTOPIA interfaces which provides access to raw ATM cells, two separate SRAM interfaces, a single SDRAM interface, and four output signals tied to LEDs. The TCPProcessor component interfaces the lower layer protocol wrappers with the core TCP-Processor.

- tcpproc.vhd- This module encapsulates the individual components which make up the TCP-Processor. Network traffic is routed between the external interfaces and the various subcomponents.

- **tcpinbuf.vhd** The TCPInbuf component provides inbound packet buffering services for the TCP-Processor when back pressure or flow control is driven by downstream components. This module also ensures that data loss occurs on packet boundaries.

- tcpengine.vhd- The TCPEngine component performs TCP processing. It communicates with the state store manager to retrieve and store per-flow context information.

- **statestoremgr.vhd** The StateStoreMgr context storage and retrieval services. A simple external interface is exposed and all complex interactions with SDRAM are handled here.

- tcprouting.vhd- The TCPRouting module routes packets previously processed by the TCPEngine to either the client monitoring circuit, the outbound TCPEgress module, or to the bit bucket. Additional control signals indicate how each packet should be routed.

- tcpstats.vhd- The TCPStats component collects statistical information from other components and maintains internal event counters. On a periodic basis, a UDP statistics packet is generated and sent to the configured destination address.

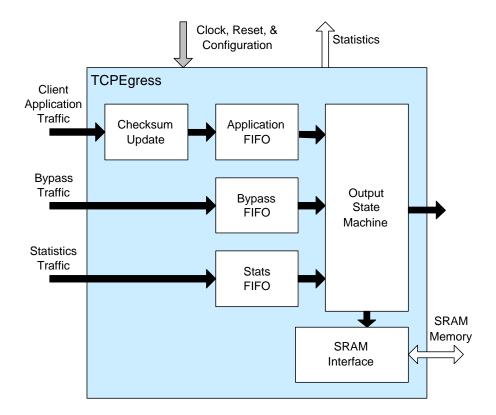

- tcpegress.vhd- The TCPEgress module merges statistics traffic from the TCPStats component, bypass traffic from the TCPRouting component, and return traffic from the client monitoring application. TCP checksum values can also be regenerated for TCP packets returning from the client monitoring application to support flow modification.

The components of the TCP-Processor directly correspond to the various source files. To simplify the layout of the circuit, each component is completely contained in a single, unique source file. Figure 4 diagrams the components of the TCP-Processor and their relative significance in the VHDL hierarchy.

Figure 4: Hierarchy of TCP-Processor Components

## 3.1 Endianness

The TCP-Processor was developed with little endian constructs. In all signal vectors, the least significant bit is the lowest bit of the vector (usually bit zero). This is the most intuitive method for representing data and is used throughout the TCP-Processor and associated circuits. The TCP-Processor has been constructed to work with network headers using little endian constructs, even though network byte order is a big endian format.

## 3.2 Packet Parameters

The TCP-Processor supports packet lengths of 1500 bytes or less. When the circuit is presented with packets larger than 1500 bytes, the viability of the operation of the circuit is not guaranteed. The circuit could likely

handle larger packets, but would be subject to lockups when packet lengths exceed the buffering capacity of internal FIFOs.

The TCP-Processor does not support IP fragments. IP defragmentation is a lower layer protocol function which should occur within the IPWrapper. The IPWrapper does not contain any logic to reassemble IP fragments into complete packets, or even validate the IP packet length. The behavior of the circuit is currently undefined when IP fragments are processed.

#### 3.3 Flow Control

Within the confines of the TCP-Processor, it is assumed that whenever the TCA signal is driven low, the sending component can continue to send data until the end of the current packet is reached. This behavior contrasts with how the other protocol wrapper circuits manage flow control signals. The advantage of this behavior is that it simplifies the logic associated with processing TCA signals. The disadvantage is that it requires larger buffers and/or FIFOs in order to store the additional data after deasserting TCA. This behavior is internal to the TCP-Processor and affects components within the TCP-Processor and any client monitoring application which interfaces with the TCP-Processor. When interfacing with the IP Wrapper, the TCP-Processor conforms to its flow control semantics.

### 3.4 External Memories

The TCP-Processor utilizes SDRAM memory module 1 to maintain per-flow context information. This task completely consumes this memory module and it should therefore not be used for any other purpose. SDRAM memory module 2 is not used by the TCP-Processor and is available for other features, such as IP packet defragmentation or TCP packet reordering. The two SRAM banks are used to capture packet data for debugging purposes. By eliminating the debugging feature, both of these high speed memory devices could be used for other purposes.

### 3.5 Configuration Parameters

The TCP-Processor uses several configuration parameters to control its operational behavior. The following list describes each of those parameters in detail, along with possible values and the effect that parameter has on the operation of the TCP-Processor circuit:

- num\_pre\_hdr\_wrds- Passed to the IPWrapper component where it is used to determine the start of the IP packet header. Known possible values for this parameter are 0 for ATM environments, 2 for ATM environments with a two word LLC header, 4 for gigabit Ethernet environments, and 5 for gigabit Ethernet environments with a VLAN tag.

- simulation- Indicates whether or not the TCP-Processor circuit should operate in simulation mode. When set to 1, memory initialization (the zeroing of external memory) is skipped. Additionally, all accesses to external SDRAM are performed at address location zero. This parameter enables the quick simulation of network traffic because the initialization of large external memories is avoided. This parameter should be set to 0 when building circuits to operate in hardware.

- **skip\_sequence\_gaps-** When set to 1, this parameter indicates that the TCPEngine should skip sequence gaps and track the highest sequence number associated with every flow. If a sequence gap occurs, the TCPEngine sets the NEW\_FLOW flag to indicate that data in this packet represents a new stream of bytes. The FLOW IDENTIFIER and the FLOW INSTANCE NUMBER will remain the same as the previous packet associated with the same flow. This information can be used by the monitoring application to determine the occurrence of a sequence gap. When set to 0, the TCP-Processor drops out-of-sequence packets until packets with the appropriate sequence number arrive.

- **app\_bypass\_enabled** Utilized by the TCPRouting module which determines where to route packets. When set to 1, retransmitted packets, non-classified TCP packets (see next configuration parameter), and non-TCP packets are allowed to bypass the client monitoring application and pass directly to the TCPEgress component. When this parameter is set to 0, all packets are routed to the client monitoring application.

- **classify\_empty\_pkts-** Indicates whether or not TCP packets which contain no user data should be classified. Performance of the circuit can be improved by avoiding classification of these packets because it takes longer to classify a packet and associated it with a flow than it takes for these small packets to be transmitted on an OC-48 (2.5Gbps) link. When enabled, all TCP packets are classified. This parameter should be enabled if the client monitoring application is tracking the connection setup/teardown sequences or is trying to process bidirectional traffic and match acknowledgment numbers with corresponding sequence numbers of traffic in the opposite direction.

- **cksum\_update\_ena-** When set to 1, the TCPEgress component will validate the TCP checksum for all TCP packets passed in by the client monitoring application. If the TCP checksum value is determined

to be incorrect, a correcting suffix is added to the end of the packet which will replace the erroneous checksum value with the proper checksum value. When set to 0, no checksum processing is performed by the TCPEgress component.

- stats\_enabled- Indicates whether or not a statistics packet should be generated at a periodic time interval. When set to 1, the generation of statistics packets is enabled and conforms to the following configuration parameters. When set to 0, statistics information will not be kept nor transmitted.

- stats\_id- This 8-bit wide configuration parameter can be used to differentiate statistics generated by multiple TCP-Processors. For example, a certain configuration consists of three different instances of the TCP-Processor circuit. All three are sending statistics information to the same collection facility. This configuration parameter differentiates the statistics information among the three different TCP-Processor circuits.

- stats\_cycle\_count- This 32-bit wide configuration parameter indicates the interval, in clock cycles, between the sending of a UDP packet containing statistics information collected during the previous collection interval. This parameter is highly dependent on the frequency of the oscillator used to drive the RAD. During simulations, this parameter can be set to a very small number so that statistics packets are generated on a much more frequent basis.

- stats\_vci- This 8-bit wide configuration parameter specifies the VCI on which the statistics packet should be generated. By altering this value, statistics packets can be routed differently than normal monitored traffic.

- stats\_dest\_addr- This 32-bit wide configuration parameter specifies the destination IP address for the statistics packets.

- stats\_dest\_port- This 16-bit wide configuration parameter specifies the destination UDP port number for the statistics packets.

### 3.6 TCP Processor

The TCPProcessor component provides the top level interface for the TCP-Processor and is implemented in the tcpprocessor.vhd source file. Within this component, the lower layered protocol wrappers are integrated with the various TCP processing components. Figure 5 contains a layout of the TCPProcessor circuit along with groupings of the main signal bundles and how they are connected between external interfaces and internal components.

Figure 5: TCPProcessor Layout

### 3.7 TCP Proc

The TCPProc component provides an integration point for the core components of the TCP-Processor circuit and is implemented in the tcpproc.vhd source file. The TCP-Processor has been broken into several manageable modules in order to isolate the various functionalities of the components. It consists of the following six components: TCPInbuf, TCPEngine, StateStoreMgr, TCPRouting, TCPEgress, and TCPStats. Well-defined interfaces allow data to transition between these components. The interface specification will be described in later sections. Figure 6 describes a layout of the TCPProc circuit along with some of the main interconnections between components.

Two SRAM memory interfaces are connected through the external interface of the TCPProc component. Inside the TCPProc component, there are three possible connection points for the two SRAM devices: two in the TCPInbuf module and one in the TCPEgress module. In order to accommodate this difference, the

Figure 6: TCPProc Layout

TCPProc maintains a virtual NOMEM1 memory device. Selected NOMEM1 signals are driven to give the appearance that the memory device is always available, but writes to the device never take place and reads from the device always result in the value of zero. By changing the connections within the TCPProc circuit, selected subcomponent interfaces can be connected to the external memory devices and others can be connected to the virtual device. This allows network traffic to be captured to memory at various locations within the circuit to aid in debugging.

### 3.8 TCP Input Buffer

Network traffic that enters the TCP-Processor is first processed by the TCPInbuf component and is implemented in the tcpinbuf.vhd source file. It provides packet buffering services to the TCP-Processor when there are periods of downstream delay and back pressure is applied by downstream components via a flow control signal. In addition, the TCPInbuf component ensures that only fully formed IP packets are passed into the downstream TCP-Processor components. The TCPInbuf component always asserts the up-

Figure 7: TCPInbuf Layout

stream flow control signal, indicating that it is always ready to receive data. If its internal buffers are filled to capacity, then TCPInbuf manages the dropping of packets form the network instead of deasserting the TCA flow control signal. Figure 7 describes the layout of the TCPInbuf component.

As network traffic enters the TCPInbuf component, it is first processed by the input state machine. The state machine determines whether the packet should be dropped (because the Frame FIFO is full) or should be inserted into the Frame FIFO. A separate packet length counting circuit counts the number of 32-bit words associated with the packet which are inserted into the Frame FIFO. At the end of the packet, this length value is written to the Length FIFO. If only a portion of the packet was successfully written to the Frame FIFO (because the FIFO filled up while inserting words), then only the length associated with the number of words actually inserted into the Frame FIFO is passed to the Length FIFO.

The output state machine can utilize two different methods to retrieve data from the FIFOs and forward it downstream: uncounted mode and counted mode. The uncounted mode is used when there are no packets queued in the Frame FIFO. This mode has a performance benefit because it does not induce a store and forward delay for the packet while the packet length is being computed. When the output state machine detects a non-empty Frame FIFO and empty Length FIFO, it will enter the uncounted processing mode. Packet data words are clocked out of the Frame FIFO and passed to the output interface of the TCPInbuf component. When the final word of the packet is read from the Frame FIFO, then the length of the packet is read from the Length FIFO.

After there has been some downstream delay in the system and one or more packets are queued up in the Frame and Length FIFOs, the counted mode is entered. This mode is also entered when the output state machine is in the idle state and data is present in both the Length and Frame FIFOs. The packet length is first read from the Length FIFO. Bits 8 through 0 indicate the length in units of 32-bit words. Bit 9 is a special drop flag which indicates whether or not the packet should be dropped. This flag is set whenever an incomplete packet is inserted into the Frame FIFO. If the drop flag is set, then the specified number of words is read from the Frame FIFO and discarded. If the drop flag is zero, the the specified number of words is read from the Frame FIFO and passed to the output interface of the TCPInbuf component.

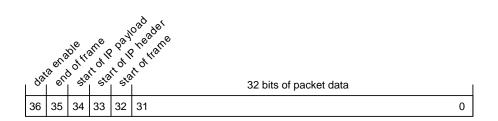

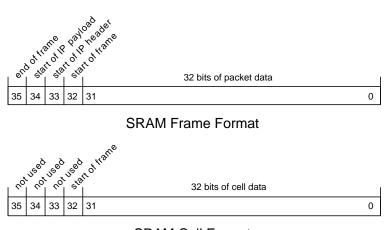

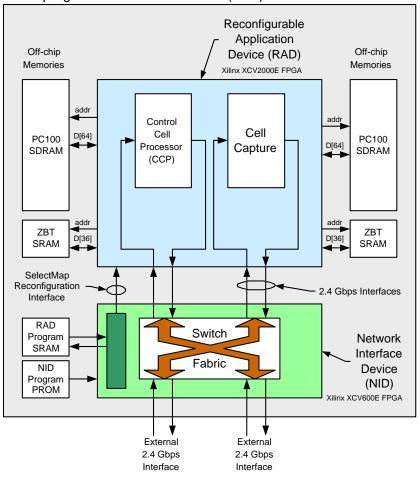

The packet storage and SRAM signals manage two separate SRAM devices used to capture packet data for debugging purposes. After reset, both SRAM memory devices are initialized to zero. The control circuits are configured to use locations 1 through 262,143 as a ring buffer. Packets passed to the outbound interface are written to the first SRAM interface and inbound ATM cells from the external RAD interface are written to the second SRAM interface. When the termination criteria has been met (check source for logic), then the memory update logic is put into a mode where it stores the current memory write address to location zero. In this manner, the 262,143 32-bit packet data words can be captured prior to the detected event. Packets (frames) and cells are stored in the standard format required by the SRAMDUMP utility. This layout of the 36-bit SRAM memory for both of these formats can be seen in Figure 8.

### 3.9 TCP Engine

The TCPEngine component is the workhorse component of the TCP-Processor and is implemented in the tcpengine.vhd source file. All of the complex protocol processing logic resides here. Figure 9 shows a breakdown of the major logic blocks and data flow through the component. Network traffic travels left to right. Flow classification and interactions with the state store manager are handled at the bottom of the diagram. The input state machine and output state machine are noted by separate boxes at the left and right

SRAM Cell Format

Figure 8: SRAM data Formats

sides of the figure. Additional state machines manage interactions with the state store manager. These are contained in the state store request/response/update block of logic.

This component has evolved over time and contains remnants of logic for features which are no longer utilized. The direction signal and the multiple hash computations are just a couple examples of this extra logic. This VHDL code remains in case it is required again in the future. Since this document describes a version of the TCP-Processor which contains this unused logic, its presence is noted.

The first series of processes described in the source file generate event signals which are passed to the TCPStats component. These signals pulse for one clock cycle whenever the associated event counter should be incremented.

When IP packets enter the TCPEngine, the input state machine processes them first. It tracks the main processing state for the TCPEngine component while processing inbound packet data. The individual states refer to the part of the packet being processed. IP header processing states include version, identifier, protocol, source IP, destination IP, and option fields. TCP header processing states include ports, sequence number, acknowledgment number, data offset, checksum, and option fields. Data0 and data1 states represent processing of TCP payload data. The copy state is entered when a non-TCP packet is encountered and the circuit switches to a mode where it just copies the packet to the Frame FIFO and no other processing is performed. The length and CRC states refer to the AAL5 trailer fields which are tacked on to the end of the

Figure 9: TCPEngine Layout

packet. The WFR state is entered when waiting for a response from the state store manager.

The next section of logic deals with extracting protocol-specific information from the protocol headers. This information includes the IP header length, an indication of whether or not the protocol is TCP, the TCP header length, the current header length, the value of various TCP flags, the source IP address, the destination IP address, and the TCP port numbers.

Next a hash value is computed based on the source IP address, the destination IP address, and the source and destination TCP ports. Many different hashing algorithms have been used throughout the development of the TCP-Processor and source code still exists for several of them. The current hash scheme is hash3. This involves combining the results of a CRC calculation over the various input values. The hash algorithm is constructed such that packets in the forward and reverse directions hash to the same value. This is accomplished by XORing the source fields with the destination fields in an identical manner. The resultant hash value is 23 bits wide, which corresponds to  $2^{23}$  or 8,388,608 unique hash values. This hash value is passed to the state store manager which performs the flow classification operation.

The next section of logic deals with operations required to initiate a flow lookup operation via the state store manager. A request state machine handles the required state transitions. After initiating the request, the state machine enters a hibernate state waiting for the end of input processing for the current packet. This ensures that multiple state store manager lookup requests are not made for one single packet. The sequence of data words which are passed to the state store manager when initiating a request for per-flow context information is listed in Table 2.

|              | Request data                           |  |

|--------------|----------------------------------------|--|

| Request word | (32 bit field)                         |  |

| 1            | "000000000" & computed hash value      |  |

| 2            | source IP address                      |  |

| 3            | destination IP address                 |  |

| 4            | source TCP port & destination TCP port |  |

Table 2: State Store Request Sequence

The following section contains logic to manage the per-flow context data returning from the state store manager. A response state machine tracks this response data. There are three paths that can be traversed through the state machine. The first is entered when a new flow context record is returned from the state store manager, the second corresponds to a valid flow context lookup of an existing flow, and the third is entered when a per-flow context lookup is not performed and a place holder is required. Table 3 shows the state transitions along with the data returned from the state store manager. Bit 31 of the first response word indicates whether or not the response corresponds to a new flow (value 0) or an existing flow (value 1). The returned flow identifier is a 26-bit value. The low two bits of the flow identifier (bits 1-0) are always

zero. Utilizing the whole flow identifier as a memory address for the SDRAM on the FPX platform provides access to a separate 32-byte section of memory for each unique flow. Bit 2 of the flow identifier is a direction bit. If only traffic propagating the network in a single direction is being monitored, then the value of this bit will always be zero. This also implies that 64 bytes of data can be stored for each unidirectional flow. If bidirectional traffic is being monitored, then the flow identifiers of outbound and inbound traffic associated with the same TCP connection will differ only by the value of this bit. There is no correlation between the value of this bit and the direction of the traffic. The only conclusion that can be drawn is that packets with flow identifiers that have the bit set are traversing the network in the opposite direction of packets with flow identifiers that have the bit cleared.

|               | New flow |                            | Existing flow |                            |

|---------------|----------|----------------------------|---------------|----------------------------|

|               |          | Response data              |               | Response data              |

| Response word | State    | (32 bit field)             | State         | (32 bit field)             |

| 1             | Idle     | "000000" & flow identifier | Idle          | "100000" & flow identifier |

| 2             | Instance | x"000000" & instance       | Sequence      | current sequence number    |

| 3             |          |                            | Instance      | x"000000" & instance       |

Table 3: State Store Response Sequence

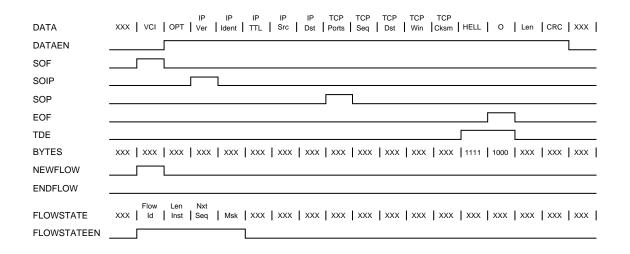

The next section of logic contains processes which perform the protocol-specific processing functions of the TCP-Processor. This includes a process which loads state/context information into the app state FIFO. When the NIL states are entered, zero values are written into this FIFO instead of valid data. This occurs when processing non-TCP packets. The contents of this FIFO will eventually be passed to the client monitoring application via the flowstate signal lines. Four data words are written to this FIFO for every packet processed. The data words either contain zeros or valid context information, depending on the type of packet being processed and the TCP-Processor configuration settings. Other logic in this section of code computes a byte offset to the first byte of new data for the flow and computation of the next sequence expected sequence number.

Logic also exists to send updated per-flow context information to the state store manager. The updated context information includes the next expected sequence number for the flow and an indication of whether or not the connection is being terminated. A signal can also be passed to the state store manager indicating that an update is not being generated and the state store manager should return to its request processing state.

Figure 10: Control FIFO data format

Signals also exist which indicate whether or not this packet is associated with a new flow, keep track of the flow identifier, and compute the length of the TCP payload. The checksum calculation logic comes next in the source file. This logic selects the appropriate words of the IP header, TCP header, and TCP payload to be used in the TCP checksum calculation.

The following section of logic writes control information into the control FIFO. The control FIFO contains information relating to the validity of the TCP checksum, an indication of whether or not this is a TCP packet, the offset to the next byte in the TCP data stream, the number of bytes in the last data word of the packet, a new flow indication, an indication of whether or not the sequence number is in the proper range, an indication of whether or not the packet should just be forwarded (i.e. for retransmitted packets), and an end-of-flow indication. The layout of this data can be seen in Figure 10.

The next process is associated with writing packet data into the data FIFO. The data inserted into this FIFO includes 32 bits of packet data, a start of frame indication, a start of IP header indication, an end of frame indication, a start of IP payload (start of TCP header) indication, a TCP stream data enable signal, a regular data enable signal, and a valid bytes vector indicating how many bytes contain stream data. The valid bytes vector is offset by one, so the value "00" indicates one valid byte, "01" indicates two valid bytes, "10" indicates three valid bytes, and "11" indicates four valid bytes.

The remainder of the TCPEngine VHDL code is responsible for retrieving data out of the three FIFOs, performing some final data modifications, and passing the information out of the TCPEngine component and onto the TCPRouting component. This whole process is driven by the output state machine which, upon detecting a non-empty control FIFO and app state FIFO, initiates the sequence of events to read information from the FIFOs and pass it to the external interface. Control signals are sent to the control, data, and app state FIFOs to start extracting their contents. As data is retrieved from the data FIFO, computations are

Figure 11: Data FIFO data format

carried out to generate the valid\_bytes signal which indicates the number of valid TCP bytes (zero, one, two, three, or four) contained on the packet data bus. Data read from the app state FIFO is passed to the flowstate vector. An offset mask and a length mask are added to this set of data which specify a mask of valid bytes for the first and last words of the stream data that should be considered part of the TCP data stream by the client monitoring application. The offset signals are used to determine where in the packet the client monitoring application should start processing TCP stream data.

#### 3.10 State Store Manager

The StateStoreMgr component provides simple interfaces for accessing and updating per-flow context information stored in external SDRAM and is implemented in the statestoremgr.vhd source file. The StateStoreMgr provides two separate interfaces for accessing per-flow context information. The first interface is used by the TCPEngine. A per-flow hash value is presented along with the source IP, destination IP, and source and destination TCP ports. The StateStoreMgr is responsible for navigating to the existing context record for that flow, or allocating new memory to hold context information for the flow. The second interface is unused. It was originally developed to provide the back end of the TCP-Processor access to per-flow context information and supported flow blocking and application state storage services. This second interface is not utilized in this version of the TCP-Processor, but much of the logic remains in place for possible future use.

A version of the TCP-Processor which supports flow blocking and application state storage can be found at the following URL: http://www.arl.wustl.edu/projects/fpx/fpx\_internal/tcp /source/streamcapture\_source.zip. Please note that the StreamCapture version of the TCP-

Figure 12: Layout of StateStoreMgr

Processor is an older version of the source and is not documented here.

By separating the logic which manages the per-flow context memory, different lookup, retrieval and memory management algorithms can easily be implemented without requiring complex changes to the TCPEngine. The SDRAM memory controller utilized by the StateStoreMgr (developed by Sarang Dharmapurikar) provides three separate interfaces: a Read only interface, a Write only interface and a Read/Write interface. Figure 12 shows the layout of the StateStoreMgr state machines and their interaction with other components. As previously stated, the second request/update interface is unused. The data bus to the SDRAM controller is 64 bits wide and the data bus exposed by the StateStoreMgr is 32 bits wide. In order to handle the transition between the two different bus widths, an separate 8x64 dual-ported RAM block is utilized in each of the interfaces.

The first process of the statestoremgr.vhd source file generates pulses relating to internal events which are passed to that TCPStats module which maintains statistical counters. The statistical events include the occurrence of a new connection, the occurrence of a reused connection (i.e. an active flow context record has been reclaimed and is being used to keep state information for a different flow), the occurrence of a terminated flow (i.e. an existing TCP connection has been closed and no longer requires state storage resources).

The remainder of the StateStoreManager logic is divided into two major sections. The first deals with frontside processing associated with Interface 1 and the second deals with backside processing associated with Interface 2. Interface 1 is connected to the TCPEngine and performs the flow classification, context storage and retrieval operations required by the TCP-Processor. Interface 2 is not used in this instance, but contains logic for performing flow blocking and application state storage services. Enhancements have been made to Interface 1 which have not been incorporated into Interface 2. Before attempting to utilize Interface 2, the inconsistencies between the two interfaces will have to be resolved.

The operations of Interface 1 are driven by the request1 state machine. Upon detecting a request, the state machine traverses through states to save the additional request data. It enters a delay state waiting for a memory read operation to complete. Once data is returned from external memory, a sequence of states are traversed which are responsible for returning results to the requestor. There is also a state to handle the processing of a context update message. There are extra states contained within this state machine which are never reached. These states support the retrieval of client monitoring application context information which is not supported in this version of the TCP-Processor. The next four processes capture flags which are stored in SDRAM. Two of these flags indicate whether the inbound traffic is valid and whether the outbound traffic is valid. The other two flags indicate whether or not the inbound or outbound flow has been terminated. These four signals help the StateStoreMgr to determine the operational state of the context record of a particular TCP flow (i.e. whether or not the record is idle, active for inbound traffic, active for outbound traffic, or whether traffic in either direction has been shut down). It is important to note that the inbound and outbound traffic directions do not correspond to the specific direction of the traffic, but just that inbound traffic is moving in the opposite direction of outbound traffic. Across multiple TCP flow context records, the inbound traffic in each of these flows may actually be moving through the network in different directions.

The subsequent two processes handle performing the exact flow context matches between the context record stored in external memory and the four-tupple of source IP address, destination IP address, and source and destination TCP ports passed in by the requestor. The match1 circuit is performing the match for outbound traffic and the match2 circuit is performing the match for inbound traffic (i.e. the match2 circuit swaps the source and destination parameters).

The following processes store individual data items from the context record returned from external memory. The current sequence numbers for both outbound and inbound traffic are stored along with the

instance identifier for that flow. As the per-flow context data is clocked in from memory, these data values are pulled off of the SDRAM read data bus. The instance identifiers are maintained for each flow record. Every time a different TCP connection is associated with a flow record, the instance identifier of that record is incremented. This provides a simple mechanism for downstream stream monitoring clients to quickly identify when a flow record is reclaimed and a different TCP connection is mapped to the same flow identifier (ie, memory record).

The next set of processes stores data items passed in as part of the initial request or computed along the way. The flow hash value, one of these data items, is used as the initial index into the state store manager hash table. The direction flop determines the direction of the flow based on which of the two flow matching processes returns a successful match. The upd\_direction stores the packet direction during update processing. This allows the request engine to start processing another lookup request. As the source IP addresses, destination IP addresses, and the TCP port values are passed in from the requestor, they are saved and used in later comparisons by the match processes.

The response1 engine is responsible for generating a response to the requesting circuit. It generates response data based on the current processing state, results of the match operations, and the value of the valid flags. The response sequence differs depending on whether or not there was a successful per-flow record match. If an existing flow record is not found, a flow identifier and an instance number are returned. If an existing flow record is found, the current sequence number is also returned. Table 3 shows the returned data in both of these scenarios.

A read state machine manages the interactions with the SDRAM controller read interface. It sequences through PullWait, TakeWait and Take states as defined by the memory controller (developed by Sarang Dharmapurikar). Prepare and Check states ensure that the frontside and backside engines are not trying to operate on the same per-flow record at the same time. Since the backside engine is not used in this incarnation of the TCP-Processor, these states will never be entered. The read engine uses the aforementioned states and drives the SDRAM controller signals to affect a read operation.

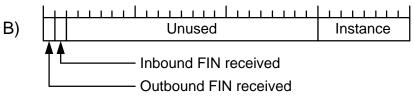

The memory layout of a bidirectional per-flow context record is shown in Figure 13. There are many unused bytes in the structure which can be utilized in conjunction with future circuit enhancements. The source IP address, the destination IP address and the source and destination TCP ports are stored within the per-flow record so that (1) an exact match can be performed to ensure that the per-flow record corresponds to the flow being retrieved and (2) the direction of the traffic (either outbound or inbound) can be determined.

| 63         |                   |                   |              |  |

|------------|-------------------|-------------------|--------------|--|

|            | See A below       | Unused            |              |  |

|            | See B below       | Source IP Address |              |  |

|            | Outbound Sequence | Destination       | IP Address   |  |

|            | Inbound Sequence  | Src TCP Port      | Dst TCP Port |  |

|            | Unused            | Unused            |              |  |

|            | Unused            | Unused            |              |  |

|            | Unused            | Unused            |              |  |

|            | Unused            | Unu               | ised         |  |

|            |                   |                   |              |  |

| 32 24 16 8 |                   |                   |              |  |

|            |                   |                   |              |  |

Figure 13: Per-Flow Record Layout

The current sequence number for both outbound and inbound traffic and an 8-bit instance identifier are also stored within the per-flow record. This instance value is incremented each time a new flow is stored in a context record. Four 1-bit flags indicate whether or not outbound traffic is valid, inbound traffic is valid, outbound traffic has ended and inbound traffic has ended.

The next couple of processes indicate whether or not the frontside engine is active and if active, the memory address of the per-flow record being accessed. When both the frontside and backside engines are

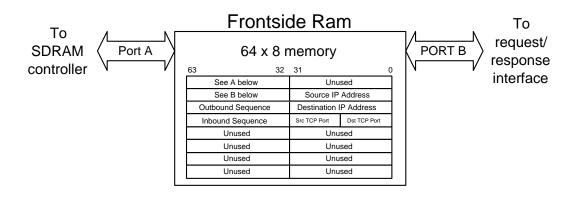

Figure 14: Frontside RAM Interface Connections

utilized, these signals are used to ensure that both engines don't try to manipulate the same context record, potentially leaving the record in an inconsistent state. In addition, three counters keep track of the take count, the app count, and the update count. The take count refers to the data words being returned from SDRAM. The app count refers to the application-specific context information stored in the context record. The storage of application specific context information is not utilized in this version of the TCP-Processor. The update count keeps track of memory update processing.

The SDRAM controller utilized by the StateStoreMgr contains a 64-bit wide data bus. The external request/response interface uses a 32-bit wide data bus. An internal dual-ported memory block moves data between these two busses. This memory block is called frontside\_ram. Two engines control the movement of data in and out of the memory. As data is clocked in from external memory, the frontside\_ram\_A\_engine writes this data into the frontside\_ram. This data is written 64 bits at a time which matches the width of the memory interface. The frontside\_ram\_A\_engine also reads data out of the frontside\_ram where it is written to the external memory device. If the application context storage feature were enabled, then read operations utilizing the frontside\_ram\_B\_engine would read application data from the frontside\_ram to be used in the response sequence to the TCPEngine. The logic still exists for this task, but the state which drives the operation is never entered. Updates to the per-flow context record are written to the frontside\_ram utilizing the frontside\_ram\_B\_engine. Figure 14 shows the various interactions with the frontside\_ram.

The following section of logic contains the write state machine which manages interactions with the write interface of the memory controller. This state machine is also responsible for initializing memory after

reset. A series of states are entered which request the memory bus and write zeros to all memory locations of the external memory module. This initializes memory to a known state prior to any per-flow context record storage or retrieval operations. The write engine ensures the correct interaction with the write interface of the memory controller.

The next grouping of processes are responsible for incrementing a memory address utilized during memory initialization and a flag to indicate that initialization has completed. Additionally, there are signals to hold the update information passed in via the external interface. These signals include the new sequence number and a finish signal which indicates that the TCP connection is being terminated. The final process of the frontside section maintains a counter utilized when writing data to external memory.

The processes associated with the backside request/response interface are listed in the remainder of the source file. The actions by these processes closely mirror the actions of the frontside interface. Because of the similarity to the frontside processing and the fact that the backside interface is not used in this implementation of the TCP-Processor, detail will not be presented on each of these processes and signals.

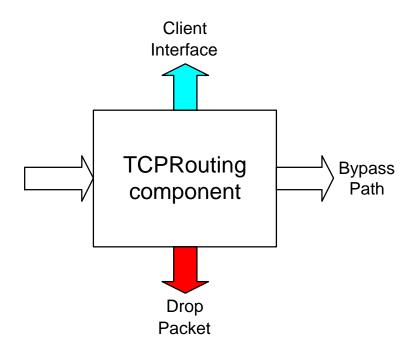

# 3.11 TCP Routing

The TCPRouting component is responsible for routing the packets and associated information that arrive from the TCPEngine component and is implemented in the tcprouting.vhd source file. These packets can be routed to either the client monitoring interface (the normal traffic flow), the TCPEgress component (the bypass path), or the bit bucket (i.e. dropped from the network). Figure 15 shows the layout of the TCPRouting component.

The first process in the tcprouting.vhd source file generates the statistics event signals passed to the TCPStats component. These signals keep track of the number of packets passed to each of the output interfaces. Additionally, there is a two-bit vector which keeps an accurate count of the TCP stream bytes passed to the application interface. This count does not include retransmitted data. The next group of processes contain flops which copy all inbound data to internal signals. These internal signals are used when passing data to the output interfaces. One state machine in this component tracks the start and the end of a packet. The processing states include idle, data, length, and crc states. The final two states indicate the end of an IP packet. Since the TCPEngine contains a store and forward cycle, packets are always received by the TCPRouting component as a continuous stream of data.

The next two processes determine whether or not to enable the client application interface, the bypass

Figure 15: TCPRouting Component

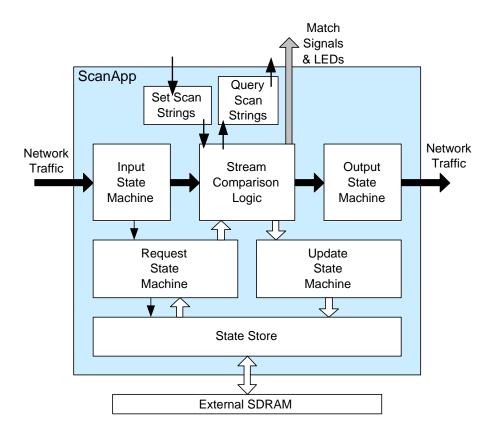

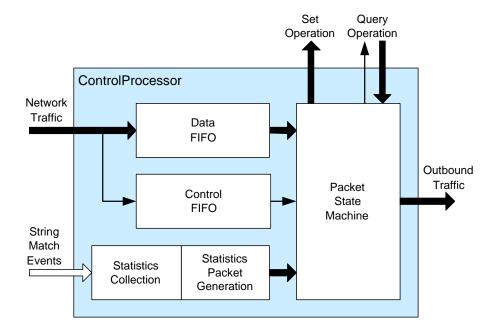

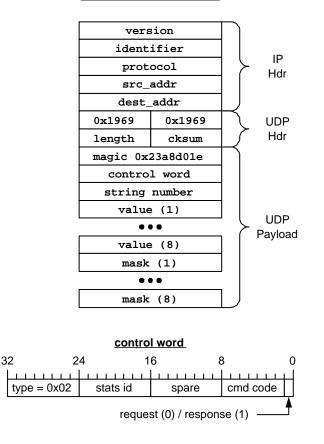

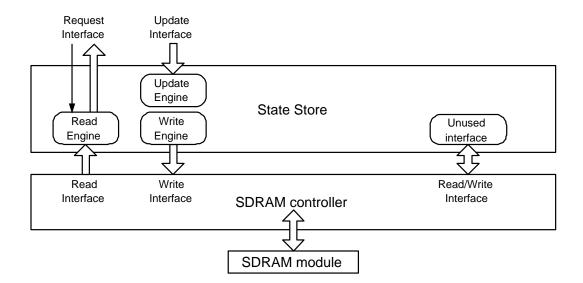

interface, or neither interface (i.e. drop packet). Information passed in from the TCPEngine and the current configuration setting are used to make this decision. Two enable signals are generated which are used by subsequent processes which actually drive the output signals. The remainder of the processes drive output signals to either the client application interface or the bypass interface. These processes look at the current processing state and the value of the aforementioned enable signals to determine whether or not to connect the internal data signals to the output interfaces.