#### Washington University in St. Louis

#### Washington University Open Scholarship

All Computer Science and Engineering Research

Computer Science and Engineering

Report Number: WUCSE-2004-42

2004-08-09

#### Scheduling Algorithms for CIOQ Switches

Prashanth Pappu and Jonathan S. Turner

Most scalable switches are required to buffer packets at both their inputs and outputs to overcome the slow memory speeds of packet queues. This thesis deals with the design of scheduling algorithms for such Combined Input and Output Queued (CIOQ) switches. For crossbar based CIOQ switches, we demonstrate the underperformance of commercially used scheduling algorithms under overload traffic conditions using targeted stress tests and present ideas to develop robust, stress resistant versions of these algorithms that are still simple enough to be implemented in high speed switches. To regulate the flow of traffic in buffered, multi-stage switches, we introduce... Read complete abstract on page 2.

Follow this and additional works at: https://openscholarship.wustl.edu/cse\_research

Part of the Computer Engineering Commons, and the Computer Sciences Commons

#### **Recommended Citation**

Pappu, Prashanth and Turner, Jonathan S., "Scheduling Algorithms for CIOQ Switches" Report Number: WUCSE-2004-42 (2004). All Computer Science and Engineering Research. https://openscholarship.wustl.edu/cse\_research/1016

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160.

This technical report is available at Washington University Open Scholarship: https://openscholarship.wustl.edu/cse\_research/1016

#### Scheduling Algorithms for CIOQ Switches

Prashanth Pappu and Jonathan S. Turner

#### **Complete Abstract:**

Most scalable switches are required to buffer packets at both their inputs and outputs to overcome the slow memory speeds of packet queues. This thesis deals with the design of scheduling algorithms for such Combined Input and Output Queued (CIOQ) switches. For crossbar based CIOQ switches, we demonstrate the underperformance of commercially used scheduling algorithms under overload traffic conditions using targeted stress tests and present ideas to develop robust, stress resistant versions of these algorithms that are still simple enough to be implemented in high speed switches. To regulate the flow of traffic in buffered, multi-stage switches, we introduce a novel mechanism called distributed scheduling. Distributed scheduling is similiar to crossbar scheduling used in switches with small port counts, but is both distributed and coarse-grained to enable high-speed implementations of scheduling algorithms in high capacity, high performance switches. In this thesis, we comprehensively study and evaluate distributed scheduling.

## SEVER INSTITUTE OF TECHNOLOGY DOCTOR OF SCIENCE DEGREE

#### DISSERTATION ACCEPTANCE

(To be the first page of each copy of the dissertation)

DATE: July 27, 2004

STUDENT'S NAME: Prashanth Pappu

This student's dissertation, entitled <u>Scheduling Algorithms for CIOQ Switches</u> has been examined by the undersigned committee of five faculty members and has received full approval for acceptance in partial fulfillment of the requirements for the degree Doctor of Science.

| APPROVAL: | <br>Chairman |

|-----------|--------------|

|           |              |

|           | <br>         |

|           |              |

|           |              |

|           | <br>         |

|           |              |

Short Title: Scheduling Algorithms for Switches Pappu, D.Sc. 2004

# WASHINGTON UNIVERSITY SEVER INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

#### SCHEDULING ALGORITHMS FOR CIOQ SWITCHES

by

Prashanth Pappu

Prepared under the direction of Dr. Jon Turner

A dissertation presented to the Sever Institute of Washington University in partial fulfillment of the requirements for the degree of

Doctor of Science

August, 2004

Saint Louis, Missouri

## WASHINGTON UNIVERSITY SEVER INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

| ABSTRACT                                |

|-----------------------------------------|

| SCHEDULING ALGORITHMS FOR CIOQ SWITCHES |

| by Prashanth Pappu                      |

| ADVISOR: Dr. Jon Turner                 |

| August, 2004<br>Saint Louis, Missouri   |

Most scalable switches are required to buffer packets at both their inputs and outputs to overcome the slow memory speeds of packet queues. This thesis deals with the design of scheduling algorithms for such Combined Input and Output Queued (CIOQ) switches.

For crossbar based CIOQ switches, we demonstrate the underperformance of commercially used scheduling algorithms under overload traffic conditions using targeted *stress tests* and present ideas to develop robust, *stress resistant* versions of these algorithms that are still simple enough to be implemented in high speed switches.

To regulate the flow of traffic in buffered, multi-stage switches, we introduce a novel mechanism called distributed scheduling. Distributed scheduling is similar to crossbar scheduling used in switches with small port counts, but is both distributed and coarse-grained to enable high-speed implementations of scheduling algorithms in high capacity, high performance switches. In this thesis, we comprehensively study and evaluate distributed scheduling.

## Contents

| Li       | st of | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | s                                               |

|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Li       | st of | Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | es                                              |

| A        | cknov | wledgn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ${f nents}$                                     |

| 1        | Intr  | oducti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | on                                              |

|          | 1.1   | The Se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | cheduling Problem                               |

|          |       | 1.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Anatomy of a Router                             |

|          |       | 1.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Output Queuing (OQ)                             |

|          |       | 1.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Combined Input and Output Queuing (CIOQ)        |

|          | 1.2   | CIOQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Switches                                        |

|          |       | 1.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Crossbar based CIOQ Switches                    |

|          |       | 1.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Buffered, Multi-stage CIOQ Switches             |

|          | 1.3   | Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Overview                                        |

|          |       | 1.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Stress Resistant Crossbar Scheduling Algorithms |

|          |       | 1.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Distributed Scheduling                          |

|          |       | 1.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Organization                                    |

| <b>2</b> | Rela  | $\mathbf{ated}  \mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}_{\mathbf{L}}}}}}}}}}$ | iterature Survey                                |

|          | 2.1   | Systen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | n Model and Definitions                         |

|          |       | 2.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Arrival Traffic                                 |

|          |       | 2.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Stability Results                               |

|          |       | 2.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Worst Case Results                              |

|          |       | 2.1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Chapter Organization                            |

|          | 2.2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ng Policies                                     |

|          | _     | 2.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FIFO Queueing                                   |

|          |       | 2.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Virtual Output Queuing                          |

|   | 2.3 | Crossbar based switches                     | 12 |

|---|-----|---------------------------------------------|----|

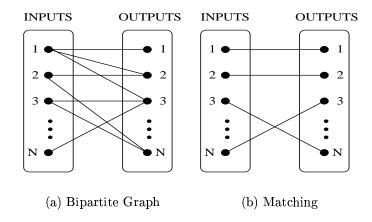

|   |     | 2.3.1 Bipartite Graph Matching              | 12 |

|   |     | 2.3.2 Maximum Size Matching                 | 13 |

|   |     | 2.3.3 Maximum Weight Matching               | 14 |

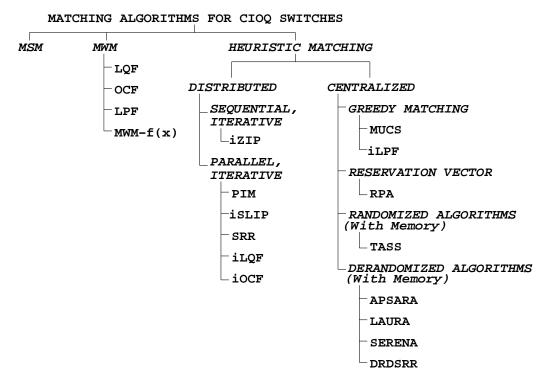

|   |     | 2.3.4 Heuristic Matching Algorithms         | 16 |

|   |     | 2.3.5 Sequential and Iterative Matching     | 17 |

|   |     | 2.3.6 Parallel and Iterative Matching       | 18 |

|   |     | 2.3.7 Greedy Matching                       | 19 |

|   |     | 2.3.8 Reservation Vector                    | 20 |

|   |     | 2.3.9 Randomized Algorithms with Memory     | 20 |

|   |     | 2.3.10 De-Randomized Algorithms with Memory | 21 |

|   |     | 2.3.11 Matrix Decomposition                 | 22 |

|   |     | 2.3.12 Birkhoff-von Neumann scheduler       | 23 |

|   |     | 2.3.13 Work Conserving Schedulers           | 24 |

|   |     | 2.3.14 Complexity Comparison                | 24 |

|   |     | 2.3.15 Performance Comparison               | 25 |

|   | 2.4 | Buffered Multi-stage Switches               | 25 |

|   | 2.5 | Load Balanced Switches                      | 26 |

|   | 2.6 | Summary                                     | 27 |

| 3 | Str | ess Resistant Scheduling Algorithms         | 32 |

|   | 3.1 | Introduction                                | 32 |

|   |     | 3.1.1 Implementation Complexity             | 32 |

|   |     | 3.1.2 Theory vs Simulation                  | 32 |

|   |     | 3.1.3 Inadmissible Traffic Conditions       | 33 |

|   |     | 3.1.4 Chapter Outline                       | 34 |

|   | 3.2 |                                             | 34 |

|   |     | 3.2.1 Throughput Metrics                    | 34 |

|   |     | 3.2.2 Miss Fraction                         | 36 |

|   |     | 3.2.3 Admissible Traffic Patterns           | 36 |

|   |     | 3.2.4 Stress Test                           | 38 |

|   | 3.3 | Crossbar Schedulers                         | 40 |

|   |     | 3.3.1 Parallel Iterative Matching (PIM)     | 40 |

|   |     |                                             | 41 |

|   |     | 3.3.3 APSARA                                | 42 |

|   |      | 3.3.4   | Lowest Occupancy Output First Algorithm (LOOFA) | $4^{2}$ |

|---|------|---------|-------------------------------------------------|---------|

|   | 3.4  | Perfor  | mance Evaluation                                | 43      |

|   |      | 3.4.1   | Miss fraction vs Delay                          | 43      |

|   |      | 3.4.2   | Varying Speedup and Number of Iterations        | 44      |

|   |      | 3.4.3   | Stress Test                                     | 48      |

|   |      | 3.4.4   | Conclusions                                     | 49      |

|   | 3.5  | Stress  | Resistant Algorithms                            | 49      |

|   | 3.6  | Lowes   | t Layer Selection                               | 50      |

|   |      | 3.6.1   | Lowest Layer Selection - Random (LLS-R)         | 52      |

|   |      | 3.6.2   | Lowest Layer Selection - Slip (LLS-S)           | 52      |

|   |      | 3.6.3   | Performance Evaluation                          | 53      |

|   | 3.7  | Using   | Output Backlogs in Edge Weights                 | 55      |

|   |      | 3.7.1   | Minimum Weight Matching (MinWM)                 | 56      |

|   |      | 3.7.2   | Shortest Output Longest Input First (SOLIF)     | 57      |

|   | 3.8  | Appro   | ximate LOOFA (A-LOOFA)                          | 59      |

|   |      | 3.8.1   | Hardware implementation of matching             | 59      |

|   |      | 3.8.2   | Odd-Even Sorting                                | 61      |

|   |      | 3.8.3   | Input permutation                               | 62      |

|   |      | 3.8.4   | Implementation issues                           | 62      |

|   |      | 3.8.5   | Performance Evaluation                          | 63      |

| 4 | Dist | tribute | ed Scheduling                                   | 65      |

|   | 4.1  | Introd  | uction                                          | 65      |

|   | 4.2  | Distril | buted Scheduling                                | 66      |

|   |      | 4.2.1   | Mechanism                                       | 66      |

|   |      | 4.2.2   | Constraints                                     | 67      |

|   |      | 4.2.3   | Distributed Scheduling vs Crossbar Scheduling   | 68      |

|   | 4.3  | Work    | Conserving Scheduling Algorithms                | 68      |

|   |      | 4.3.1   | Problem Definition                              | 68      |

|   |      | 4.3.2   | System Model                                    | 69      |

|   |      | 4.3.3   | Maximal and Ordered Scheduling Algorithms       | 70      |

|   | 4.4  | Batch   | Critical Cells First Algorithm                  | 71      |

|   |      | 4.4.1   | VOQ Ordering                                    | 71      |

|   |      | 4.4.2   |                                                 | 71      |

|   |      | 4.4.3   | Proof                                           | 73      |

|                  | 4.5    | Batch        | Least Occupied Output First Algorithm    | 75  |

|------------------|--------|--------------|------------------------------------------|-----|

|                  |        | 4.5.1        | VOQ Ordering                             | 75  |

|                  |        | 4.5.2        | Example                                  | 76  |

|                  |        | 4.5.3        | Proof                                    | 76  |

|                  | 4.6    | Impler       | nentation of Maximal, Ordered Schedulers | 82  |

|                  | 4.7    | Distrib      | outed, Iterative Schedulers              | 84  |

|                  | 4.8    | Distrib      | outed BLOOFA (DBL)                       | 85  |

|                  |        | 4.8.1        | Example                                  | 86  |

|                  |        | 4.8.2        | Performance Analysis (Stress Test)       | 87  |

|                  |        | 4.8.3        | Performace Analysis (Bursty Traffic)     | 89  |

|                  |        | 4.8.4        | Contention Factor                        | 91  |

|                  | 4.9    | The O        |                                          | 92  |

|                  |        | 4.9.1        | · · ·                                    | 93  |

|                  |        | 4.9.2        |                                          | 95  |

|                  | 4.10   | $\Delta$ -OL |                                          | 97  |

|                  |        | 4.10.1       | Example                                  | 98  |

|                  |        | 4.10.2       | Distributed OLA                          | 98  |

|                  |        | 4.10.3       | Performance Analysis                     | 00  |

|                  | 4.11   | Practic      | cal Considerations                       | 01  |

|                  | 4.12   | Future       | Work                                     | 03  |

| 5                | Con    | cludin       | g Remarks                                | )5  |

| $\mathbf{R}_{0}$ | eferei | ices .       |                                          | )7  |

| <b>1</b> 7:      | ita    |              | 1.                                       | 1 / |

## List of Tables

| 2.1 | Comparison of run-time complexity of various scheduling algorithms      |    |

|-----|-------------------------------------------------------------------------|----|

|     | for crossbar based CIOQ switches                                        | 29 |

| 2.2 | Comparison of run-time complexity of various scheduling algorithms      |    |

|     | for crossbar based CIOQ switches (continued from Table 2.1)             | 30 |

| 2.3 | Summary of performance results of various scheduling algorithms for     |    |

|     | crossbar based CIOQ switches under various traffic conditions           | 31 |

| 4.1 | Notation used in describing batch critical cells first algorithm        | 71 |

| 4.2 | Notation used in describing the batch least occupied output first algo- |    |

|     | rithm                                                                   | 76 |

| 4.3 | Notation used in describing the output leveling algorithm               | 93 |

## List of Figures

| 1.1               | Router Architecture                                                                                                                              | 2        |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2               | Crossbar based switch.                                                                                                                           | 4        |

| 1.3               | Buffered crossbar switch element                                                                                                                 | 5        |

| 1.4               | Multi-stage switch                                                                                                                               | 5        |

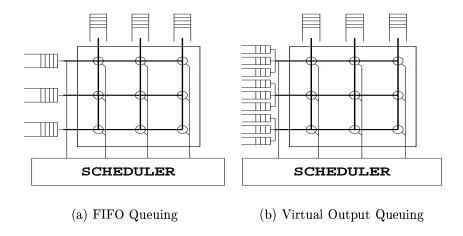

| 2.1               | FIFO vs Virtual Output Queuing                                                                                                                   | 11       |

| 2.2               | Representation of the scheduling problem in a CIOQ switch as a bi-                                                                               |          |

|                   | partite graph and a corresponding matching                                                                                                       | 13       |

| 2.3               | Classification of various heuristic matching algorithms used in schedul-                                                                         |          |

|                   | ing CIOQ switches.                                                                                                                               | 16       |

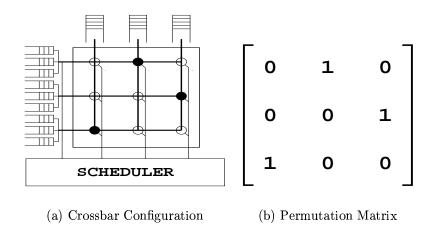

| 2.4               | Configuration of a 3x3 crossbar and the corresponding permutation                                                                                |          |

|                   | matrix                                                                                                                                           | 22       |

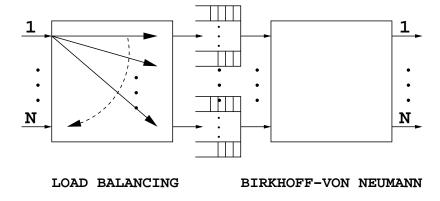

| 2.5               | The Load Balanced switch.                                                                                                                        | 26       |

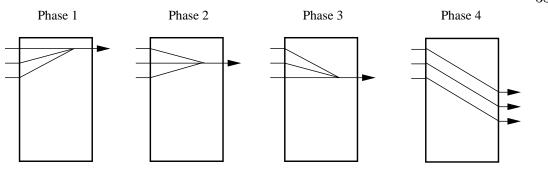

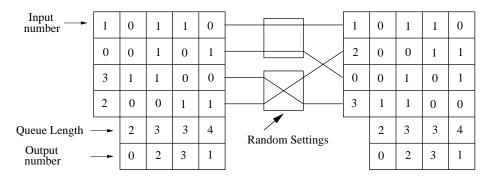

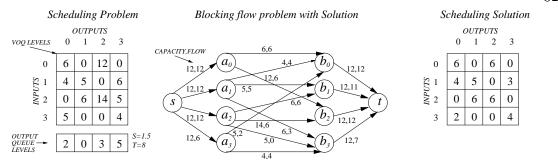

| 3.1               | Example of stress test with 3 participating inputs and 4 phases                                                                                  | 38       |

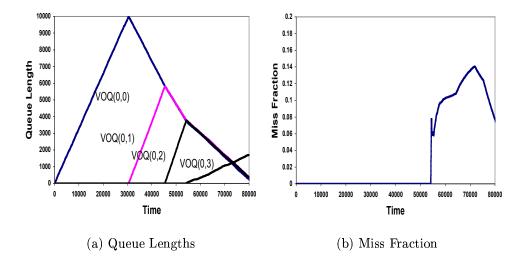

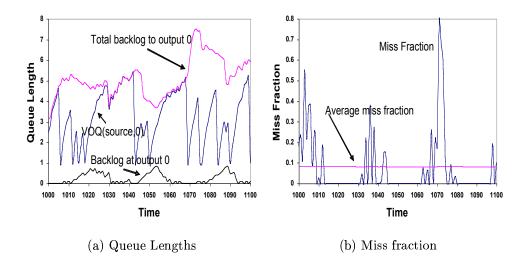

| 3.2               | Queue lengths of various VOQs and miss fraction for PIM under a                                                                                  |          |

|                   |                                                                                                                                                  |          |

|                   | stress test with 3 participating inputs and 4 phases. (N=16, speedup=1.5)                                                                        | 39       |

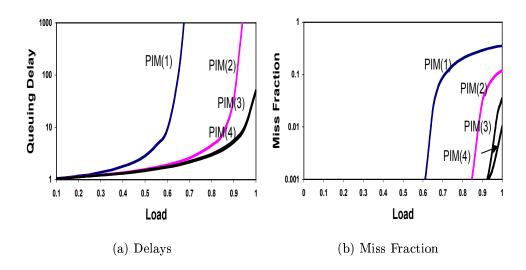

| 3.3               | stress test with 3 participating inputs and 4 phases. (N=16, speedup=1.5) Average delays and miss fractions for various iterations of PIM, N=16, | 39       |

|                   |                                                                                                                                                  | 39<br>43 |

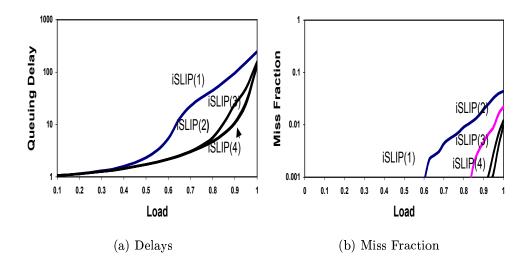

|                   | Average delays and miss fractions for various iterations of PIM, N=16,                                                                           |          |

| 3.3               | Average delays and miss fractions for various iterations of PIM, N=16, speedup=1.0                                                               |          |

| 3.3               | Average delays and miss fractions for various iterations of PIM, N=16, speedup=1.0                                                               | 43       |

| 3.3               | Average delays and miss fractions for various iterations of PIM, N=16, speedup=1.0                                                               | 43       |

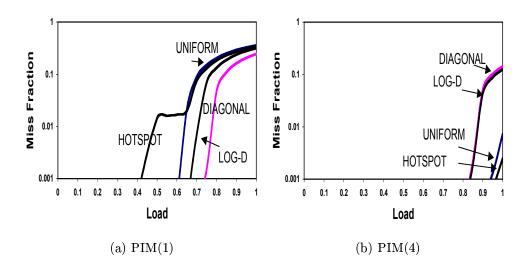

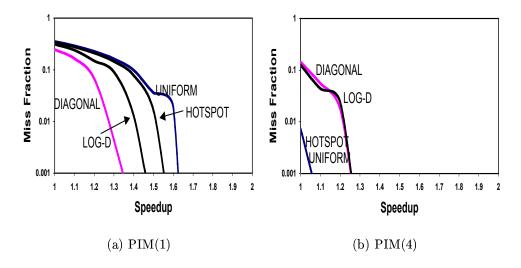

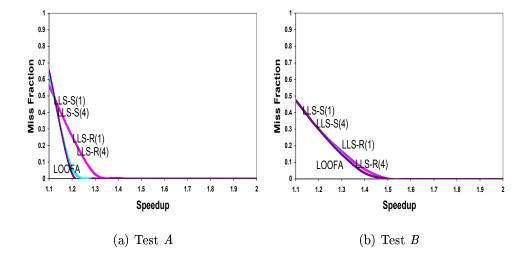

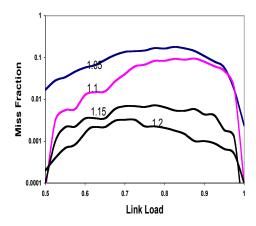

| 3.3               | Average delays and miss fractions for various iterations of PIM, N=16, speedup=1.0                                                               | 43<br>45 |

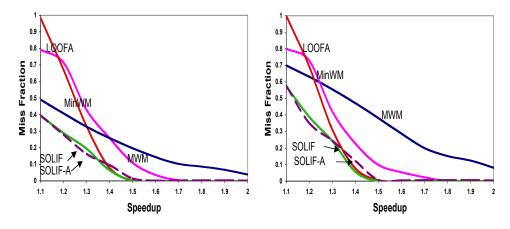

| 3.3<br>3.4<br>3.5 | Average delays and miss fractions for various iterations of PIM, N=16, speedup=1.0                                                               | 43<br>45 |

| 3.3<br>3.4<br>3.5 | Average delays and miss fractions for various iterations of PIM, N=16, speedup=1.0                                                               | 45<br>45 |

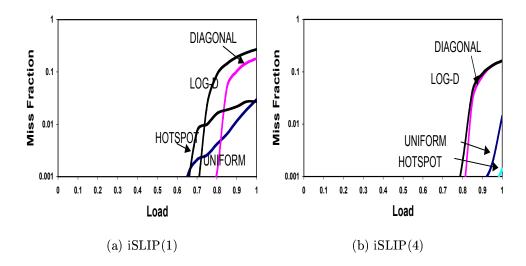

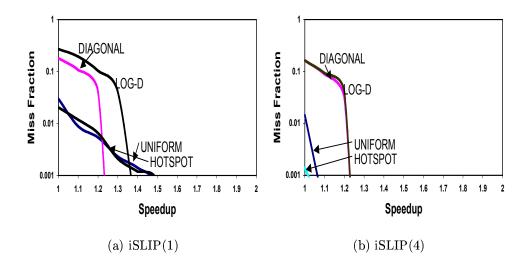

| 3.8  | Miss fractions for various iterations of $iSLIP$ (N=16, load=1.0), with  |    |

|------|--------------------------------------------------------------------------|----|

|      | varying speedup, under various admissible traffic patterns               | 47 |

| 3.9  | Performance of APSARA (with $d = 20$ ) under varying loads (N=16,        |    |

|      | speedup = 1.0), under various $admissible$ traffic patterns              | 47 |

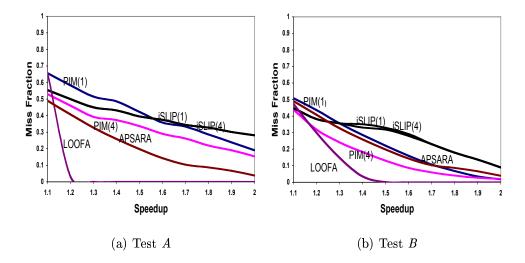

| 3.10 | Miss fractions for PIM, $i$ SLIP and LOOFA under stress test with 5      |    |

|      | participating inputs and 12 phases                                       | 48 |

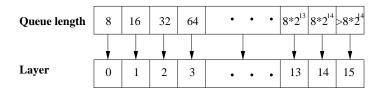

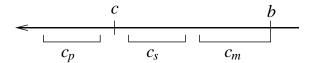

| 3.11 | Exponentially graded scale used in assigning outputs to layers based     |    |

|      | on their queue length.                                                   | 51 |

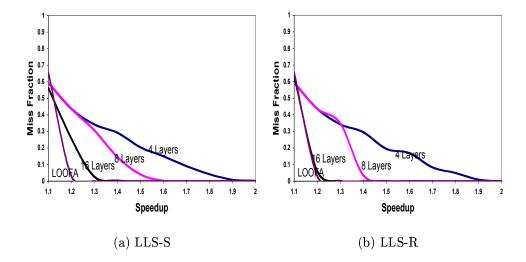

| 3.12 | Miss fractions for various iterations of LLSR (N=16, load=1.0), with     |    |

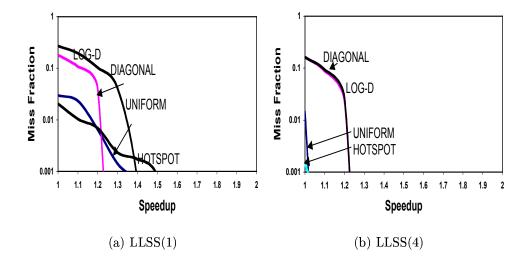

|      | varying speedup, under various $admissible$ traffic patterns             | 53 |

| 3.13 | Miss fractions for various iterations of LLSS (N=16, load=1.0), with     |    |

|      | varying speedup, under various $admissible$ traffic patterns             | 54 |

| 3.14 | Miss fractions for LLS-R, LLS-S (using 16 layers) and LOOFA under        |    |

|      | stress test with 5 participating inputs and 12 phases                    | 54 |

| 3.15 | Miss fractions for LLS-R and LLS-S (single iteration) with varying       |    |

|      | layers under stress test with 5 participating inputs and 12 phases (Test |    |

|      | A)                                                                       | 55 |

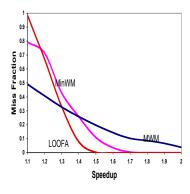

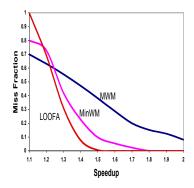

| 3.16 | Miss fractions for MWM, MinWM and LOOFA, with varying speedup,           |    |

|      | under two stress tests                                                   | 56 |

| 3.17 | Miss fractions for SOLIF, MWM, MinWM and LOOFA, with varying             |    |

|      | speedup, under two stress tests                                          | 57 |

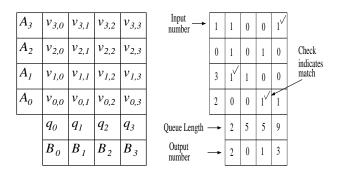

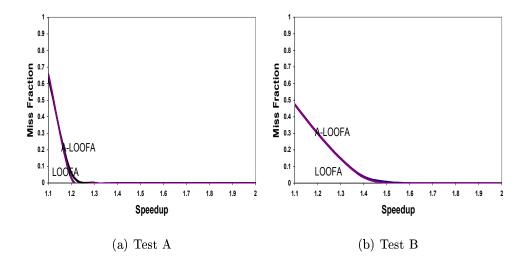

| 3.18 | Principal hardware components and example operation of A-LOOFA           | 59 |

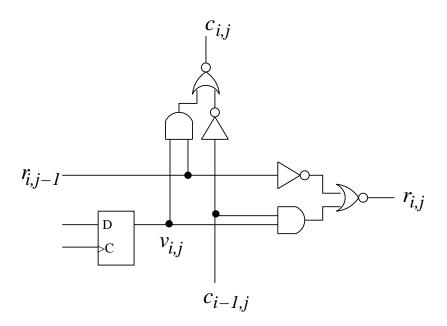

| 3.19 | Match Logic                                                              | 60 |

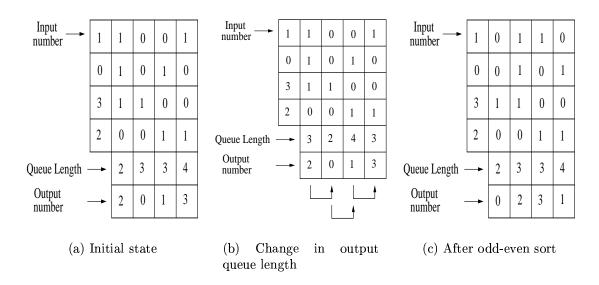

| 3.20 | Example demonstrating the use of the odd-even sorting technique          | 61 |

| 3.21 | Example showing the permutation of inputs                                | 62 |

| 3.22 | Miss fractions for A-LOOFA and LOOFA under stress test with 5 par-       |    |

|      | ticipating inputs and 12 phases                                          | 64 |

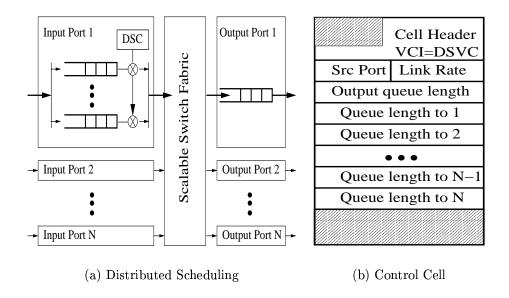

| 4.1  | Router with distributed scheduling.                                      | 66 |

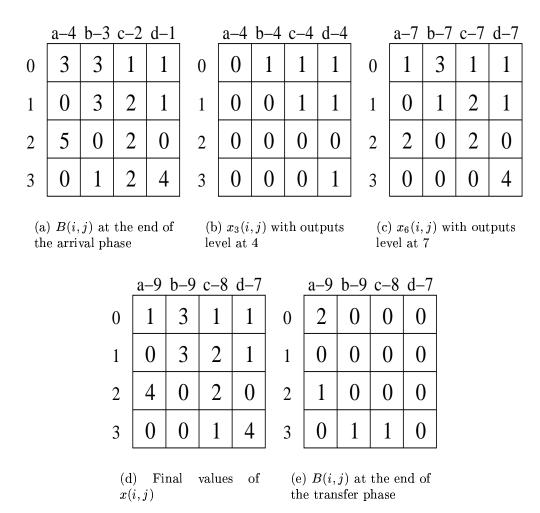

| 4.2  | Example operation of the BCCF algorithm                                  | 72 |

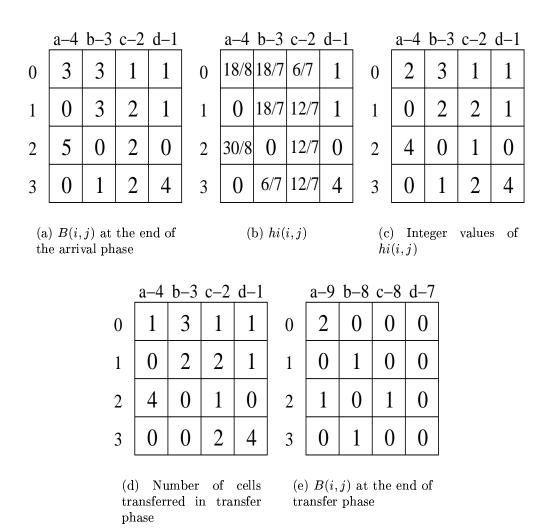

| 4.3  | Example operation of the BLOOFA algorithm                                | 77 |

| 4.4  | Precedence list.                                                         | 79 |

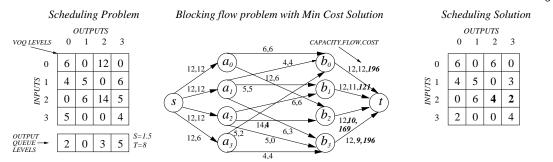

| 4.5  | Example of a maximal ordered schedule constructed from a blocking        |    |

|      | flow                                                                     | 82 |

| 4.6  | Example operation of the DBL algorithm                                   | 86 |

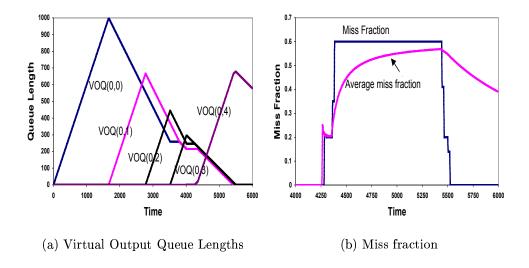

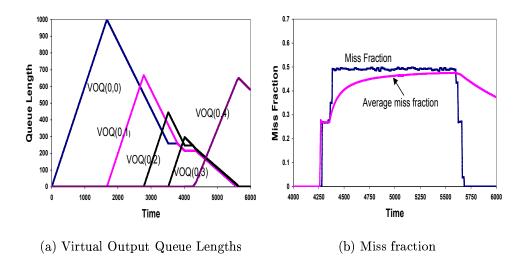

| 4.7  | Example stress test (3 inputs, 5 phases, speedup=1.2) on BLOOFA                 | 87  |

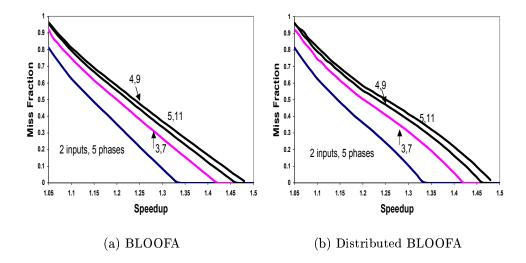

|------|---------------------------------------------------------------------------------|-----|

| 4.8  | Miss fractions for DBL and BLOOFA on a variety of stress tests (with            |     |

|      | varying inputs and phases)                                                      | 88  |

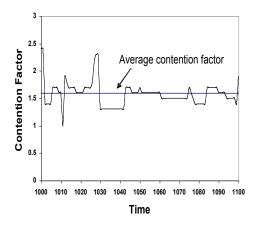

| 4.9  | Results from a sample simulation of DBL under bursty traffic (speedup=1 $^{-1}$ | .1, |

|      | load=0.9, mean dwell time = 10)                                                 | 89  |

| 4.10 | Performance of DBL under bursty traffic patterns with varying speedups          |     |

|      | and subject, target dwell times.                                                | 89  |

| 4.11 | Contention factor for the sample bursty traffic test on DBL shown in            |     |

|      | Fig. 4.9                                                                        | 91  |

| 4.12 | Implementing OLA using minimum-cost blocking flow with convex cost              |     |

|      | function. Differences from earlier solution highlighted in <b>bold</b>          | 96  |

| 4.13 | Example operation of the $\Delta$ -OLA algorithm (with $\Delta = 1$ )           | 99  |

| 4.14 | Sample stress test (3 inputs, 5 phases) on DOLA with speedup= $1.2$ .           | 100 |

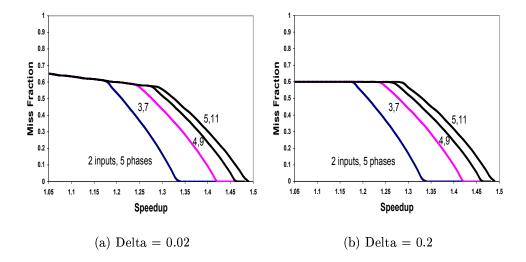

| 4.15 | Miss fractions for Distributed OLA and under a variety of stress tests          |     |

|      | with varying delta                                                              | 101 |

## Acknowledgments

To these, I owe a debt past telling.

First, my advisor Dr. Jon Turner for all his guidance and wisdom. Also, all the committee members for their support and feedback.

My colleagues at the Applied Research Laboratory for all their help and company.

And finally, my parents and family for their infinite patience and unconditional love and support.

Prashanth Pappu

Washington University in Saint Louis August 2004

## Chapter 1

### Introduction

#### 1.1 The Scheduling Problem

#### 1.1.1 Anatomy of a Router

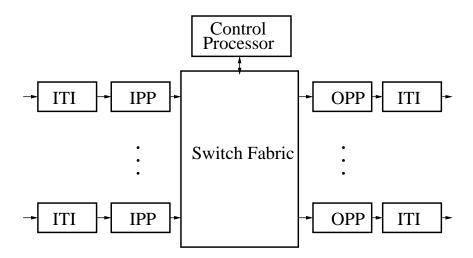

The main function of a router<sup>1</sup> is to forward packets from its input ports to its output ports. Fig. 1.1 shows the various components of a router. A switching fabric connects the input side Port Procesors (PPs) to the output side PPs. The port processors queue packets and perform all packet processing functions like packet classification, route lookup and packet scheduling. The input and output transmission interfaces (ITI and OTI) terminate the physical links and provide the requisite conversion and encoding functions for transmitting/receiving packets on the target physical layer. The control processor implements the routing and other network management protocols.

#### 1.1.2 Output Queuing (OQ)

Ideally, we would like all packets in the router to be buffered only at the output ports. In such a router (called Output Queued (OQ) router), when two or more packets destined to the same output arrive simultaneously at different input ports, they are immediately transferred to the output queue to avoid any packet loss. This architecture not only simplifies the design of the router but also

1. Maximizes the throughput of the router.

$<sup>^{1}\</sup>mathrm{We}$  use the terms router and switch and packet and cell interchangeably, unless explicitly specified.

Figure 1.1: Router Architecture

2. Enables the ready use of packet scheduling algorithms [67] for providing Quality of Service (QoS) guarantees to individual flows.

Since there is no queuing at the inputs, the output queues of an OQ router with N line cards each connected to a line operating at a rate R should have a bandwidth of  $(N+1)\times R$  (to support N writes for each read). Unfortunately, although router capacities  $(N\times R)$  have increased by about 2.2 times every 18 months (slightly faster than Moore's law), router buffer (DRAM) speeds have only increased by about 1.1 times every 18 months (slower than Moore's law) [57]. This mismatch makes the use of output queuing infeasible in scalable routers.

#### 1.1.3 Combined Input and Output Queuing (CIOQ)

To overcome the mismatch between the capacities of routers and the speed of memories, most switches queue packets at both input and output ports of the switch. This Combined Input and Output Queuing (CIOQ) lets us use lower speed memories for buffering packets. When two or more packets at different inputs, contend to go to the same output some of them are temporarily held in the input queues before being transferred to the outputs.

The switching fabric of a CIOQ switch is itself operated at a speed S (called speedup) times the link rate R. Though, the speedup of a CIOQ switch can be any value between 1 and N, in practice, it is usually a small constant (typically,  $\leq 2$ ). Hence, a CIOQ switch with a speedup of S needs memories with a bandwidth of just

$(1+S) \times R$ . A switch with a speedup of 1 effectively queues all packets only at inputs and is called an Input Queued (IQ) switch.

While a CIOQ switch requires lower speed switching fabrics and memories, it also introduces a scheduling problem. A decision needs to be made every time slot to determine which inputs are allowed to transfer cells to which outputs. The design of scheduling algorithms to perform this function is the focus of this dissertation. The objective in the design of these schedulers is to approximate the throughput and delay properties of a pure output queued switch.

#### 1.2 CIOQ Switches

#### 1.2.1 Crossbar based CIOQ Switches

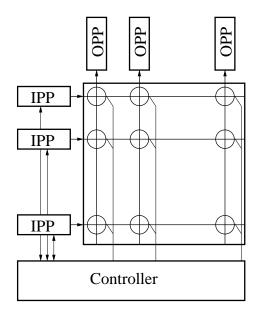

Commercial CIOQ switches with small port counts often use a non-blocking crossbar as the switching fabric. An  $N \times N$  crossbar is organized as an  $N \times N$  matrix to connect input ports to output ports as shown in Fig. 1.2. A crossbar allows multiple cells to pass in parallel to distinct outputs. Though a crossbar has quadratic complexity  $(O(N^2))$ , it concentrates this complexity within a single chip or a chipset for moderate scale switches, reducing impact on the system cost. The scheduling problem in crossbar based CIOQ switches is reduced to configuring the non-blocking crossbar using a centralized controller every time slot to determine which inputs are allowed to transmit to which outputs.

Though the throughput and delay properties of a scheduler determine its performance, it is the implementation simplicity which is the primary factor in determining which scheduling algorithms are used in high speed switches. For instance, in a switch with external link rates of 10 Gb/s, the scheduler has less than 40 ns to make a scheduling decision.<sup>2</sup>. Hence, though a number of scheduling algorithms have been proposed and studied in the literature (see Chapter 2), very few of them can be implemented and used in practice.

This has created a situation where algorithms with proven performance under a variety of traffic conditions are often not implementable, and implementable algorithms (which do not lend themselves to theoretical analysis) are evaluated only according to their packet delays under admissible and/or random uniform traffic. Hence,

<sup>&</sup>lt;sup>2</sup>Assuming a minimum packet size of 50 bytes.

Figure 1.2: Crossbar based switch.

it is unclear how most commercially used algorithms perform under extreme traffic conditions frequently encountered in unregulated IP networks.

#### 1.2.2 Buffered, Multi-stage CIOQ Switches

In crossbar based switches, all the line cards and the crossbars in the switching fabric must be synchronized to the centralized scheduler. The frequency (once in less than 40 ns for a switch with 10 Gb/s links) and the complexity ( $O(\log N)$  iterations for even simple algorithms) of the scheduling algorithms, makes it infeasible to use crossbars for large switching systems.

One approach to alleviate the centralized scheduling problem is the introduction of buffers at the crosspoints of a crossbar. Such a switching element is called a buffered crossbar. With these buffers, cells are sent from inputs into the crossbar only if the corresponding crosspoint has empty buffers. Thus, the ingress scheduling problem is reduced to a simple flow control mechanism. A backpressure signal is used to indicate if the input can forward cells to the crosspoint. On the egress side, the outputs schedule cells from one of the N cross-points destined to them. Unfortunately, the discrete nature of buffering makes this architecture memory intensive. A  $16 \times 16$  crossbar needs 256 buffers, each with a space for at least a few cells.

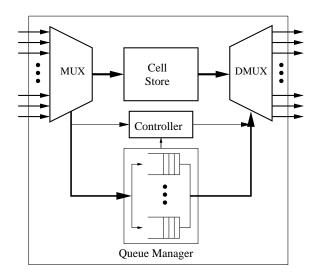

The buffered crossbar architecture can be further simplified by using shared memory within the crossbar as shown in Fig. 1.3. The switching element has an

Figure 1.3: Buffered crossbar switch element.

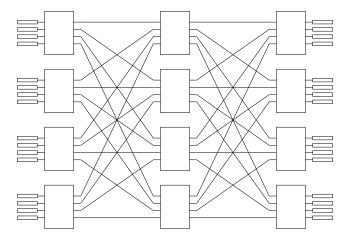

Figure 1.4: Multi-stage switch.

internal shared buffer (*cell store*) for up to a few thousand cells with current technology. The cells are multiplexed from the inputs of the switching element to free slots in the cell store. These cells are then forwarded to the outputs as and when they become idle. A controller uses per output queue information to configure the input side multiplexer and the output side demultiplexer.

Such switching elements can be used in multi-stage switching fabrics with inter stage flow control to build large switching systems as shown in Fig. 1.4. The simple flow control mechanism along with a modest speedup can alleviate the need for a centralized scheduler and maintain throughput even under temporary overloads.

The performance of such switching systems can degrade drastically in the presence of sustained overloads. In extreme traffic conditions, when a single output port

of a switch is under sustained overload, the shared memory buffers in the switching fabric can be congested with cells attempting to reach the overloaded output, interfering with other traffic directed to non-overloaded outputs. The unregulated nature of IP traffic makes such overloads a normal fact of life, which router designers must address if their systems are to be robust enough to perform under the most demanding of traffic conditions.