#### Washington University in St. Louis

# Washington University Open Scholarship

All Computer Science and Engineering Research

Computer Science and Engineering

Report Number: WUCSE-2005-18

2005-05-01

# Architectures for Rule Processing Intrusion Detection and **Prevention Systems**

Michael E. Attig

High-performance intrusion detection and prevention systems are needed by network administrators in order to protect Internet systems from attack. Researchers have been working to implement components of intrusion detection and prevention systems for the highly popular Snort system in reconfigurable hardware. While considerable progress has been made in the areas of string matching and header processing, complete systems have not yet been demonstrated that effectively combine all of the functionality necessary to perform intrusion detection and prevention for real network systems. In this thesis, three architectures to perform rule processing, the heart of intrusion detection and prevention, are presented.... Read complete abstract on page 2.

Follow this and additional works at: https://openscholarship.wustl.edu/cse\_research

Part of the Computer Engineering Commons, and the Computer Sciences Commons

#### **Recommended Citation**

Attig, Michael E., "Architectures for Rule Processing Intrusion Detection and Prevention Systems" Report Number: WUCSE-2005-18 (2005). All Computer Science and Engineering Research. https://openscholarship.wustl.edu/cse\_research/935

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160.

This technical report is available at Washington University Open Scholarship: https://openscholarship.wustl.edu/ cse\_research/935

### Architectures for Rule Processing Intrusion Detection and Prevention Systems

Michael E. Attig

#### **Complete Abstract:**

High-performance intrusion detection and prevention systems are needed by network administrators in order to protect Internet systems from attack. Researchers have been working to implement components of intrusion detection and prevention systems for the highly popular Snort system in reconfigurable hardware. While considerable progress has been made in the areas of string matching and header processing, complete systems have not yet been demonstrated that effectively combine all of the functionality necessary to perform intrusion detection and prevention for real network systems. In this thesis, three architectures to perform rule processing, the heart of intrusion detection and prevention, are presented. The first system, called Snort Lite, implements a subset of the features necessary for rule processing in a single Xilinx Virtex XCV2000E \_eld programmable gate array. The second system, called Snort Intrusion Filter for TCP (SIFT), limits the amount of traffic an intrusion detection PC needs to examine by searching for rule criteria. The final architecture presents a framework for implementing the entire rule processing system in reconfigurable hardware. The framework integrates the functionality to scan data flows for regular expressions, \_xed strings, and header values. Additional processing modules can be added to the system to perform specific functionality required for some Snort rules. Reconfigurability and flexibility are key features of the system that enable it to adapt to protect Internet systems from threats including malicious worms, computer viruses, and network intruders. The framework allows experimentation with new techniques to perform the functionality required for intrusion systems. Each architecture uses the Field-programmable Port eXtender (FPX) platform to scan all bytes of Transmission Control Protocol/Internet Protocol (TCP/IP) traffic entering and leaving a network's gateway at multi-gigabit rates. The combined circuits perform deep-packet inspection to search for thousands of signatures. The rule processing framework supports up to 32,768 complex rules at data rates of 2.5 Gbps on the FPX platform.

# SEVER INSTITUTE OF TECHNOLOGY MASTER OF SCIENCE DEGREE

#### THESIS ACCEPTANCE

(To be the first page of each copy of the thesis)

DATE: April 28, 2005

STUDENT'S NAME: Michael E. Attig

This student's thesis, entitled <u>Architectures for Rule Processing Intrusion Detection and Prevention Systems</u> has been examined by the undersigned committee of three faculty members and has received full approval for acceptance in partial fulfillment of the requirements for the degree Master of Science.

| APPROVAL: | Chairman |

|-----------|----------|

|           |          |

|           |          |

|           |          |

Short Title: Rule Processing IDPS Attig, M.Sc. 2005

# WASHINGTON UNIVERSITY SEVER INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

# ARCHITECTURES FOR RULE PROCESSING INTRUSION DETECTION AND PREVENTION SYSTEMS

by

Michael E. Attig

B.S. Computer Engineering, B.S. Electrical Engineering

Prepared under the direction of Professor John W. Lockwood

A thesis presented to the Sever Institute of Washington University in partial fulfillment of the requirements for the degree of

Master of Science

May, 2005

Saint Louis, Missouri

# WASHINGTON UNIVERSITY SEVER INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

| ABSTRACT                                                                     |

|------------------------------------------------------------------------------|

| ARCHITECTURES FOR RULE PROCESSING INTRUSION DETECTION AND PREVENTION SYSTEMS |

| by Michael E. Attig                                                          |

| ADVISOR: Professor John W. Lockwood                                          |

| May, 2005<br>Saint Louis, Missouri                                           |

High-performance intrusion detection and prevention systems are needed by network administrators in order to protect Internet systems from attack. Researchers have been working to implement components of intrusion detection and prevention systems for the highly popular Snort system in reconfigurable hardware. While considerable progress has been made in the areas of string matching and header processing, complete systems have not yet been demonstrated that effectively combine all of the functionality necessary to perform intrusion detection and prevention for real network systems.

In this thesis, three architectures to perform rule processing, the heart of intrusion detection and prevention, are presented. The first system, called Snort Lite, implements a subset of the features necessary for rule processing in a single Xilinx Virtex XCV2000E field programmable gate array. The second system, called Snort Intrusion Filter for TCP (SIFT), limits the amount of traffic an intrusion detection PC needs to examine by searching for rule criteria. The final architecture presents a framework for implementing the entire rule processing system in reconfigurable hardware. The framework integrates the functionality to scan data flows for regular expressions, fixed strings, and header values. Additional processing modules can be added to the system to perform specific functionality required for some Snort rules. Reconfigurability and flexibility are key features of the system that enable it to adapt to protect Internet systems from threats including malicious worms, computer viruses, and network intruders. The framework allows experimentation with new techniques to perform the functionality required for intrusion systems.

Each architecture uses the Field-programmable Port eXtender (FPX) platform to scan all bytes of Transmission Control Protocol/Internet Protocol (TCP/IP) traffic entering and leaving a network's gateway at multi-gigabit rates. The combined circuits perform deep-packet inspection to search for thousands of signatures. The rule processing framework supports up to 32,768 complex rules at data rates of 2.5 Gbps on the FPX platform.

To my family and friends, who have always supported me.

# Contents

| Li           | List of Tables |            |                                         |    |  |  |  |

|--------------|----------------|------------|-----------------------------------------|----|--|--|--|

| Li           | st of          | Figure     | es                                      | xi |  |  |  |

| $\mathbf{A}$ | ckno           | wledgn     | nents                                   | xv |  |  |  |

| 1            | Intr           | oducti     | ion                                     | 1  |  |  |  |

|              | 1.1            | Motiva     | ation                                   | 2  |  |  |  |

|              |                | 1.1.1      | Economic Impact of Intrusions and Spam  | 2  |  |  |  |

|              |                | 1.1.2      | Scalability                             | 3  |  |  |  |

|              | 1.2            | Intrusi    | ion Detection                           | 4  |  |  |  |

|              |                | 1.2.1      | Types of Intrusions                     | 5  |  |  |  |

|              |                | 1.2.2      | Methods of the Detection                | 7  |  |  |  |

|              |                | 1.2.3      | Responses                               | 8  |  |  |  |

|              |                | 1.2.4      | Who is the Authority?                   | 9  |  |  |  |

|              | 1.3            | Rule F     | Processing for Intrusion Detection      | 9  |  |  |  |

|              |                | 1.3.1      | Necessary Characteristics               | 10 |  |  |  |

|              | 1.4            | Thesis     | Objectives                              | 10 |  |  |  |

|              | 1.5            |            | ibutions                                | 11 |  |  |  |

|              | 1.6            | Thesis     | Outline                                 | 11 |  |  |  |

| 2            | Bac            | Background |                                         |    |  |  |  |

|              | 2.1            | Impler     | mentation Medium                        | 13 |  |  |  |

|              |                | 2.1.1      | General Purpose Processors              | 13 |  |  |  |

|              |                | 2.1.2      | Network Processors                      | 14 |  |  |  |

|              |                | 2.1.3      | Field Programmable Gate Array           | 14 |  |  |  |

|              |                | 2.1.4      | Application Specific Integrated Circuit | 14 |  |  |  |

|              | 2.2            | Netwo      | rking Protocols                         | 15 |  |  |  |

|   |     | 2.2.1   | Asynchronous Transfer Mode    | 5  |

|---|-----|---------|-------------------------------|----|

|   |     | 2.2.2   | Internet Protocol             | 5  |

|   |     | 2.2.3   | User Datagram Protocol        | 6  |

|   |     | 2.2.4   | Transmission Control Protocol | 6  |

|   | 2.3 | Curren  | nt Rule Processing Systems    | 8  |

|   |     | 2.3.1   | Components of Rule Processing | 8  |

|   |     | 2.3.2   | Firewalls                     | 8  |

|   |     | 2.3.3   | Policy Engines                | 9  |

|   | 2.4 | Snort:  | A Detailed Look               | 9  |

|   |     | 2.4.1   | Setup                         | 20 |

|   |     | 2.4.2   | Snort Rule Set                | 20 |

|   |     | 2.4.3   | Rule Features                 | 22 |

|   |     | 2.4.4   | Algorithms                    | 24 |

|   |     | 2.4.5   | Performance                   | 26 |

|   |     | 2.4.6   | Portability Difficulties      | 27 |

|   | 2.5 | Flow F  | Reconstruction                | 28 |

|   |     | 2.5.1   | Requirements                  | 28 |

|   |     | 2.5.2   | Techniques                    | 29 |

|   | 2.6 | Header  | Rule Matching                 | 29 |

|   |     | 2.6.1   | Requirements                  | 29 |

|   |     | 2.6.2   | Techniques                    | 30 |

|   | 2.7 | String  | Matching                      | 31 |

|   |     | 2.7.1   | Requirements                  | 31 |

|   |     | 2.7.2   | Techniques                    | 32 |

| 3 | Sno | rt Lite | $m{3}$                        | 8  |

|   | 3.1 | Design  | Objectives                    | 8  |

|   | 3.2 | Design  | Decisions                     | 39 |

|   |     | 3.2.1   | Rule Types                    | 39 |

|   |     | 3.2.2   | Architectural Components      | 39 |

|   | 3.3 | Featur  |                               | 10 |

|   | 3.4 | Archite | ecture                        | 11 |

|   |     | 3.4.1   | Overview                      | 11 |

|   |     | 3.4.2   | Content Scanner               | 12 |

|   |     | 3.4.3   | Header Processor              | 17 |

|   |     | 3.4.4 Control Packet Processor | 48 |

|---|-----|--------------------------------|----|

|   |     | 3.4.5 Statistics Module        | 49 |

|   |     | 3.4.6 Alert Generator          | 49 |

|   |     | 3.4.7 Hardware Infrastructure  | 49 |

|   | 3.5 | Implementation Results         | 50 |

|   | 3.6 | Memory Bandwidth Requirements  | 50 |

|   | 3.7 | Observations                   | 51 |

|   |     | 3.7.1 Security & Adaptability  | 51 |

|   |     | 3.7.2 Additions & Expansions   | 51 |

|   |     | 3.7.3 Lessons Learned          | 52 |

| 4 | Sno | rt Intrusion Filter for TCP    | 53 |

|   | 4.1 | Design Objectives              | 53 |

|   | 4.2 | Design Decisions               | 54 |

|   |     | 4.2.1 Characteristics          | 54 |

|   |     | 4.2.2 Architectural Needs      | 54 |

|   | 4.3 | Features                       | 55 |

|   | 4.4 | Context Switching              | 55 |

|   | 4.5 | Architecture                   | 56 |

|   |     | 4.5.1 Overview                 | 56 |

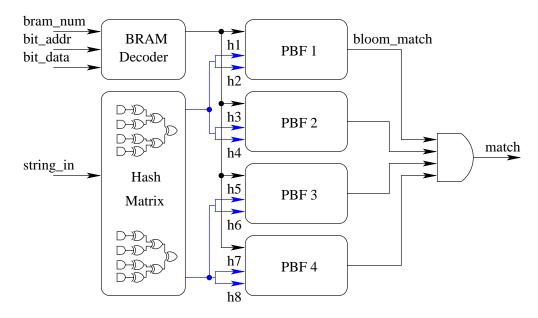

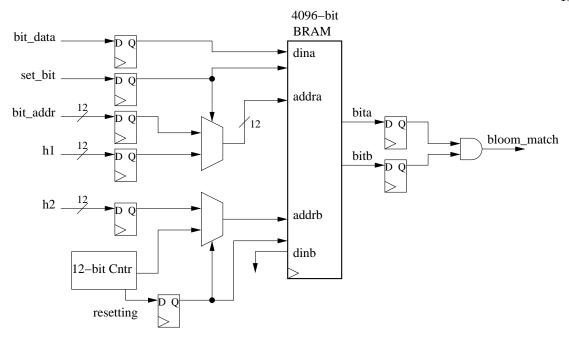

|   |     | 4.5.2 Quad Bloom Filters       | 57 |

|   |     | 4.5.3 Header Check             | 58 |

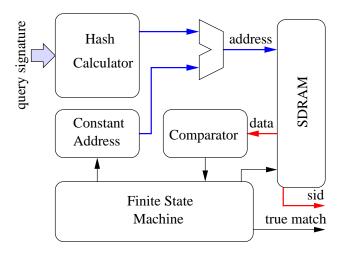

|   |     | 4.5.4 Action Retriever         | 58 |

|   |     | 4.5.5 SNMP Alerter             | 58 |

|   |     | 4.5.6 Alert Generator          | 59 |

|   |     | 4.5.7 Communication Wrapper    | 59 |

|   |     | 4.5.8 TCP Lite Wrapper         | 60 |

|   |     | 4.5.9 SDRAM Buffer             | 61 |

|   |     | 4.5.10 Input/Output Buffering  | 61 |

|   | 4.6 | Implementation Results         | 61 |

|   | 4.7 | Memory Bandwidth Requirements  | 61 |

|   | 4.8 | Observations                   | 63 |

|   |     | 4.8.1 String Matching          | 63 |

| 5 | Rul | e Proc  | essing Framework              |  |  |  |  |  |

|---|-----|---------|-------------------------------|--|--|--|--|--|

|   | 5.1 | Design  | n Objectives                  |  |  |  |  |  |

|   | 5.2 | Design  | n Decisions                   |  |  |  |  |  |

|   |     | 5.2.1   | System Layout                 |  |  |  |  |  |

|   | 5.3 | Featur  | res                           |  |  |  |  |  |

|   | 5.4 | System  | n Overview                    |  |  |  |  |  |

|   | 5.5 | Archit  | secture                       |  |  |  |  |  |

|   |     | 5.5.1   | Pipeline Stages               |  |  |  |  |  |

|   |     | 5.5.2   | Efficient Context Switching   |  |  |  |  |  |

|   |     | 5.5.3   | Buffering                     |  |  |  |  |  |

|   |     | 5.5.4   | Control                       |  |  |  |  |  |

|   | 5.6 | Imple   | mentation Results             |  |  |  |  |  |

|   | 5.7 | Discus  | ssion                         |  |  |  |  |  |

|   |     | 5.7.1   | Maintaining Throughput        |  |  |  |  |  |

|   |     | 5.7.2   | Effects of Context Switching  |  |  |  |  |  |

|   |     | 5.7.3   | Experimental Performance      |  |  |  |  |  |

|   |     | 5.7.4   | Memory Bandwidth Requirements |  |  |  |  |  |

|   | 5.8 | Obser   | vations                       |  |  |  |  |  |

|   |     | 5.8.1   | Memory                        |  |  |  |  |  |

| 6 | Res | Results |                               |  |  |  |  |  |

|   | 6.1 |         | g Environment                 |  |  |  |  |  |

|   |     | 6.1.1   | FPX                           |  |  |  |  |  |

|   |     | 6.1.2   | GVS-1500                      |  |  |  |  |  |

|   |     | 6.1.3   | WUGS-20                       |  |  |  |  |  |

|   | 6.2 | Snort   | Lite Results                  |  |  |  |  |  |

|   |     | 6.2.1   | Compatible Snort Rules        |  |  |  |  |  |

|   |     | 6.2.2   | Throughput                    |  |  |  |  |  |

|   |     | 6.2.3   | System Tests                  |  |  |  |  |  |

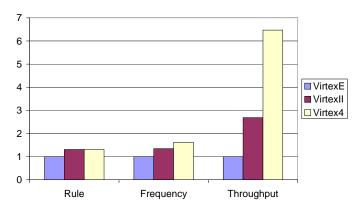

|   |     | 6.2.4   | Next Generation FPGAs         |  |  |  |  |  |

|   | 6.3 | SIFT    | Results                       |  |  |  |  |  |

|   |     | 6.3.1   | Compatible Snort Rules        |  |  |  |  |  |

|   |     | 6.3.2   | Throughput                    |  |  |  |  |  |

|   |     | 6.3.3   | SIFT Test Configuration       |  |  |  |  |  |

|   |     | 6.3.4   | Testing Results               |  |  |  |  |  |

|              | 6.4  | Rule I  | Processor Results                | 88        |

|--------------|------|---------|----------------------------------|-----------|

|              |      | 6.4.1   | Compatible Rules                 | 88        |

|              |      | 6.4.2   | Throughput                       | 88        |

|              |      | 6.4.3   | Next Generation FPGA Projections | 90        |

|              | 6.5  | Comp    | arisons                          | 91        |

|              |      | 6.5.1   | Hardware vs. Software            | 91        |

|              |      | 6.5.2   | Effects of Context Switching     | 91        |

|              |      | 6.5.3   | Comparison with Related Work     | 92        |

| 7            | Con  | clusio  | n                                | 93        |

|              | 7.1  | Summ    | nary of Approaches               | 93        |

|              | 7.2  | Contri  | ibutions                         | 94        |

|              |      | 7.2.1   | Conclusions Drawn                | 95        |

|              | 7.3  | Future  | e Work                           | 96        |

| $\mathbf{A}$ | ppen | dix A   | Control Software                 | 97        |

|              | A.1  |         |                                  | 97        |

|              | A.2  |         |                                  | )4        |

|              |      | A.2.1   |                                  | )(        |

|              |      | A.2.2   | Communication Wrapper            | )6        |

|              | A.3  | Rule I  | Processor                        | )8        |

|              | A.4  | Statist | tics Graphing                    | 11        |

| $\mathbf{A}$ | ppen | dix B   | Laboratory Configuration         | 13        |

|              | B.1  | Config  | guration of Snort Lite           | 13        |

|              | B.2  | Config  | guration of SIFT                 | 15        |

|              | В.3  | Config  | guration of Rule Processor       | 16        |

| $\mathbf{A}$ | ppen | dix C   | Source Files                     | <u> 1</u> |

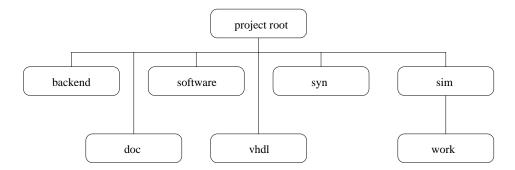

|              | C.1  | Comm    | non Directory Structure          | 19        |

|              | C.2  | Script  | s                                | 2(        |

|              | C.3  | Snort   | Lite                             | 20        |

|              | C.4  | SIFT    |                                  | 21        |

|              | C.5  | Rule I  | Processor                        | 21        |

|              | C.6  | Comm    | nunication Wrapper               | 21        |

| $\mathbf{A}$ | ppen | dix D   | Additional Figures               | 22        |

| Appendix E List of Acronyms | <br>132         |

|-----------------------------|-----------------|

| References                  | <br><b>13</b> 4 |

| Vita                        | <br>148         |

# List of Tables

| 1.1 | A summary of the cost of malicious code by incident [1, 123] | 3  |

|-----|--------------------------------------------------------------|----|

| 2.1 | Header and payload options                                   | 23 |

| 3.1 | Snort Lite resource usage                                    | 50 |

| 4.1 | SIFT resource usage                                          | 62 |

| 5.1 | Rule Processor resource usage                                | 73 |

| 6.1 | Xilinx FPGA resource summary                                 | 82 |

| 6.2 | SIFT Bloom engine loading summary                            | 85 |

| 6.3 | SIFT transmission reduction summary                          | 85 |

| 6.4 | Related work comparison                                      | 92 |

| 7 1 | Architecture resource requirements                           | 94 |

# List of Figures

| 1.1  | The cost of malicious code is increasing exponentially $[1, 2, 123]$ |

|------|----------------------------------------------------------------------|

| 1.2  | Intrusion detection system layout                                    |

| 2.1  | IP packet format                                                     |

| 2.2  | TCP packet format                                                    |

| 2.3  | Matching TCP/IP packet                                               |

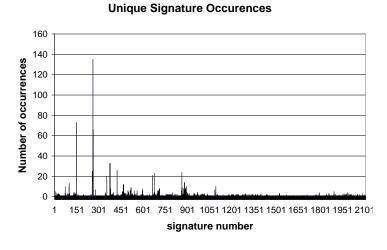

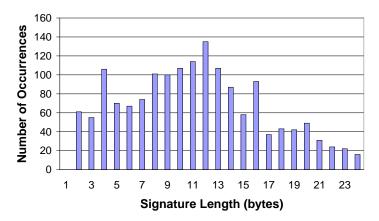

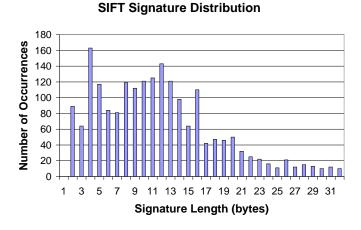

| 2.4  | Snort signature distribution                                         |

| 2.5  | Snort signature frequency                                            |

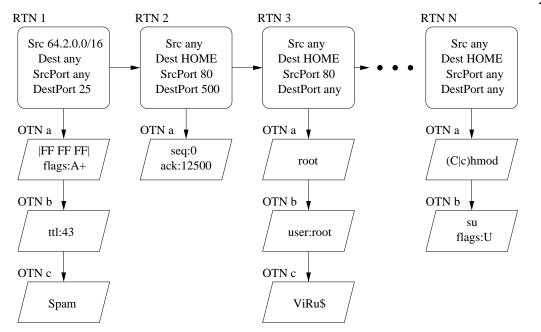

| 2.6  | Snort rule representation                                            |

| 2.7  | Boyer-Moore algorithm example                                        |

| 2.8  | Aho-Corasick algorithm example                                       |

| 2.9  | Example single bit trie                                              |

| 2.10 | Example NFA and DFA representation of a regular expression 3         |

| 2.11 | Overview of a Bloom filter                                           |

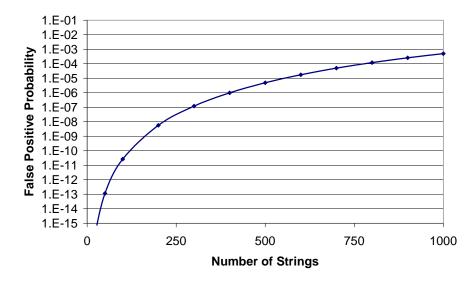

| 2.12 | Bloom filter false positive probabilities                            |

| 3.1  | Snort Lite block diagram                                             |

| 3.2  | Content scanner block diagram                                        |

| 3.3  | Bloom filter false positive probability                              |

| 3.4  | Bloom filter block diagram                                           |

| 3.5  | Partial Bloom filter circuit diagram                                 |

| 3.6  | Hash table block diagram                                             |

| 3.7  | Hash table record format                                             |

| 3.8  | Header record format                                                 |

| 4.1  | SIFT block diagram                                                   |

| 4.2  | Quad Bloom filter block diagram                                      |

| 4.3  | An example of bytes moving through the pipeline                      |

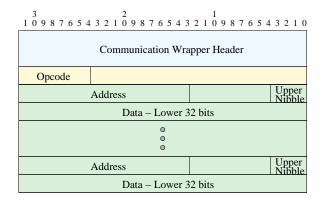

| 4.4  | Communication wrapper interface                                | 59  |

|------|----------------------------------------------------------------|-----|

| 4.5  | Communication wrapper interface timing                         | 60  |

| 5.1  | Data format for communicating matching rule criteria           | 66  |

| 5.2  | Rule processing framework overview                             | 67  |

| 5.3  | Rule Processor block diagram                                   | 69  |

| 5.4  | SRAM record summary                                            | 70  |

| 5.5  | Average- and worst-case performance                            | 75  |

| 5.6  | SDRAM storage format                                           | 76  |

| 6.1  | FPX platform                                                   | 78  |

| 6.2  | GVS-1500                                                       | 79  |

| 6.3  | Washington University Gigabit Switch                           | 79  |

| 6.4  | Snort Lite supported signature distribution                    | 80  |

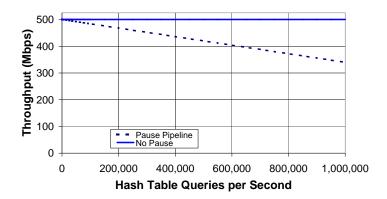

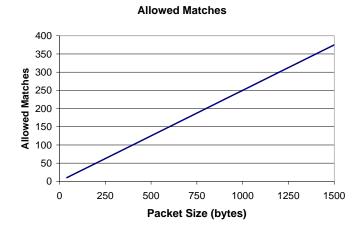

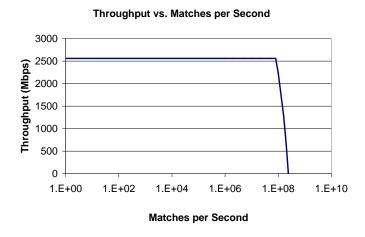

| 6.5  | Snort Lite throughput vs. matches/sec                          | 81  |

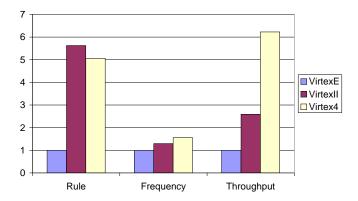

| 6.6  | The projected relative improvements of Snort Lite              | 83  |

| 6.7  | SIFT supported signature distribution                          | 83  |

| 6.8  | SIFT throughput vs. matches/pkt                                | 84  |

| 6.9  | SIFT throughput vs. matches/sec                                | 84  |

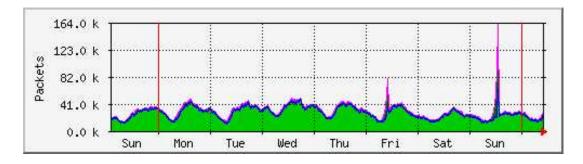

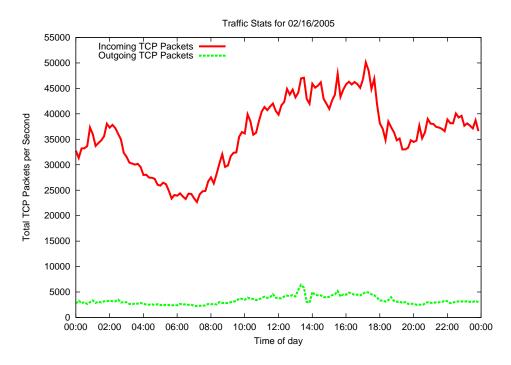

| 6.10 | The number of incoming TCP packets for Feb 13-20, 2005         | 86  |

| 6.11 | The number of outgoing TCP packets for Feb 13-20, 2005         | 87  |

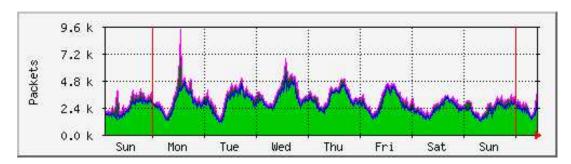

| 6.12 | Incoming and outgoing TCP packets per second                   | 87  |

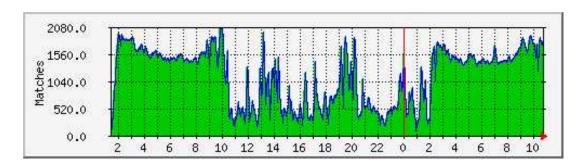

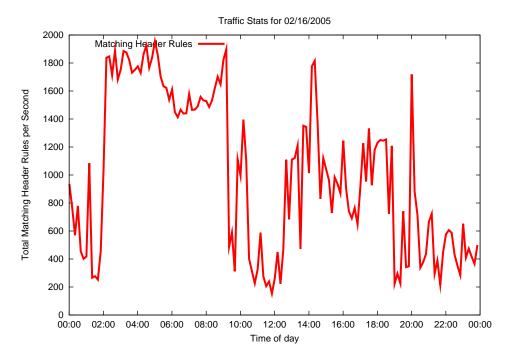

| 6.13 | Matching header-only rules per second                          | 87  |

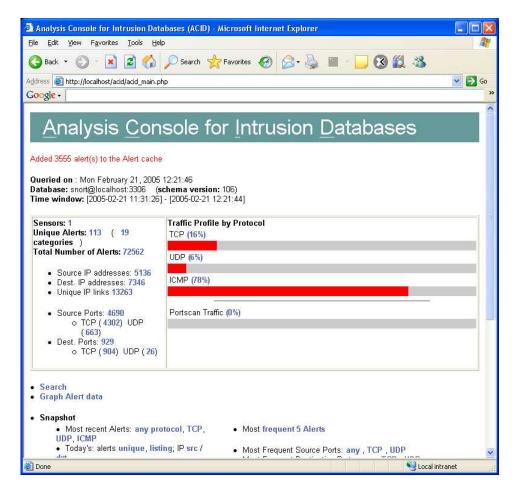

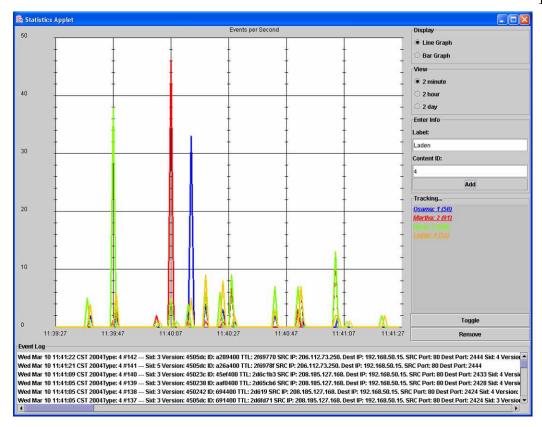

| 6.14 | Software analysis console                                      | 88  |

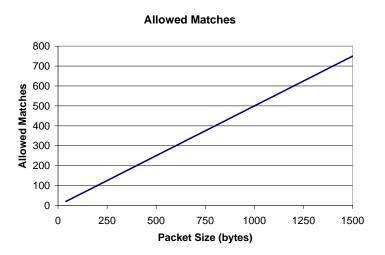

| 6.15 | Rule processor throughput vs. matches/pkt                      | 89  |

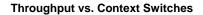

| 6.16 | Rule processor throughput vs. context switches/sec             | 90  |

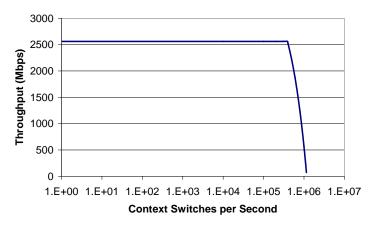

| 6.17 | Rule processor throughput vs. matches/sec                      | 90  |

| 6.18 | The projected relative improvements of the Rule Processor      | 91  |

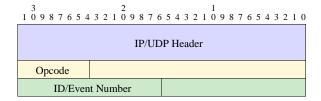

| A.1  | Analyzer control packet format (opcodes x70 and x72)           | 100 |

| A.2  | Bloom filter control packet format (opcode x74)                | 101 |

| A.3  | Header entry control packet format (opcode x76)                | 101 |

| A.4  | Change of alert destination control packet format (opcode x80) | 101 |

| A.5  | Read status/event control packet format (x78, x82 and x84)     | 101 |

| A.6  | Type 1 alerts acknowledge the receipt of a control opcode      | 102 |

| A.7  | Type 2 alerts contain the header entry that was read           | 102 |

| A.8  | Type 3 alerts are used to return a statistic                                      | 102 |

|------|-----------------------------------------------------------------------------------|-----|

| A.9  | Type 4 alerts return matching rule IDs and the packet header                      | 103 |

| A.10 | Type 8 alerts return matching rule IDs and the entire packet. $\ \ . \ \ . \ \ .$ | 103 |

| A.11 | SIFT opcode 1 is used to correlate signatures with actions                        | 106 |

| A.12 | SIFT opcode 2 is used to set/reset bits in a Bloom filter                         | 106 |

| A.13 | ATM cell example                                                                  | 107 |

| A.14 | SRAM write control packet format (opcodes 1 and 2)                                | 110 |

| A.15 | SRAM read control packet format (opcodes 3 and 4)                                 | 110 |

| A.16 | BRAM write control packet format (opcode 5)                                       | 110 |

| A.17 | Statistics graphing application window                                            | 111 |

| B.1  | Snort Lite system configuration                                                   | 114 |

| B.2  | Snort Lite FPX configuration                                                      | 114 |

| В.3  | SIFT laboratory configuration                                                     | 115 |

| B.4  | Rule Processor laboratory configuration                                           | 117 |

| C.1  | Common project directory structure                                                | 119 |

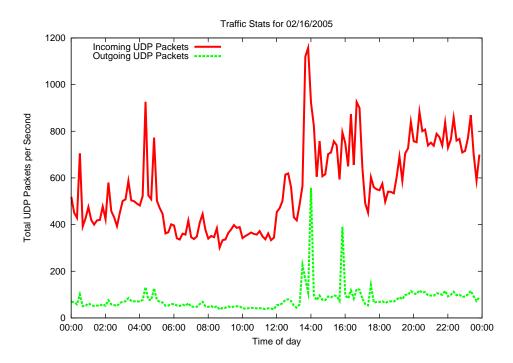

| D.1  | Incoming and outgoing UDP packets versus time on Feb 16, 2005                     | 122 |

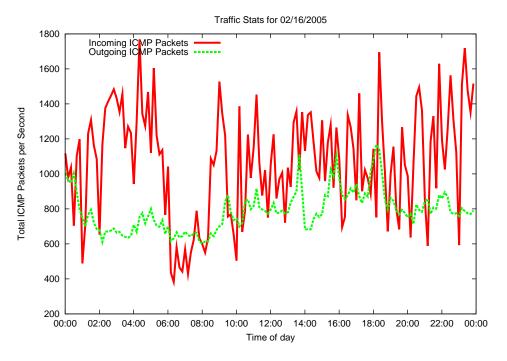

| D.2  | Incoming and outgoing ICMP packets versus time on Feb 16, 2005. $$ .              | 123 |

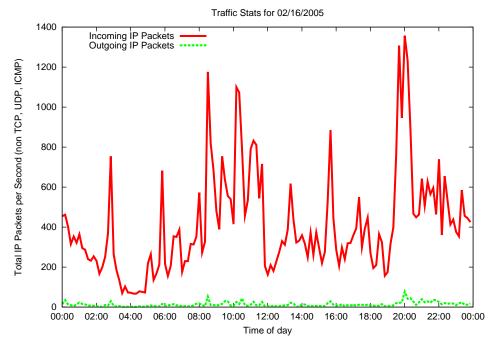

| D.3  | Incoming and outgoing IP packets (not TCP, UDP, nor ICMP) versus                  |     |

|      | time on Feb 16, 2005                                                              | 123 |

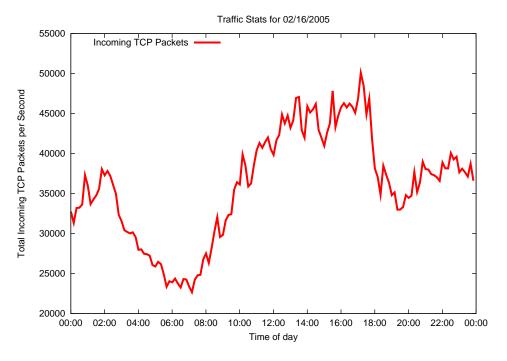

| D.4  | Incoming TCP packets per second versus time on Feb 16, 2005                       | 124 |

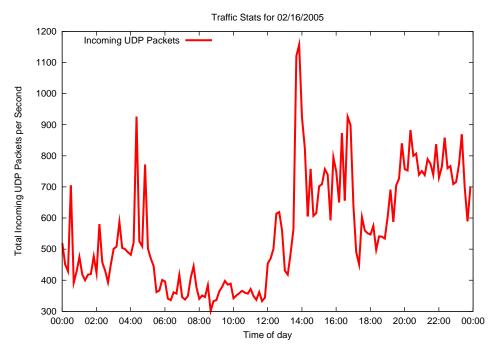

| D.5  | Incoming UDP packets per second versus time on Feb 16, 2005                       | 124 |

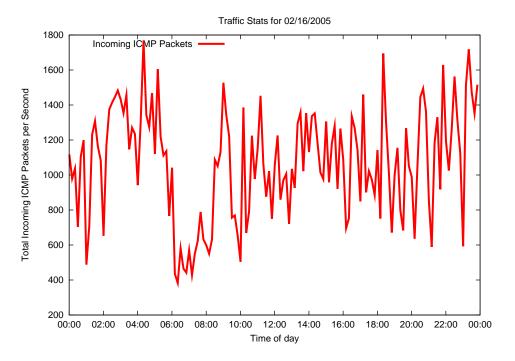

| D.6  | Incoming ICMP packets per second versus time on Feb 16, 2005                      | 125 |

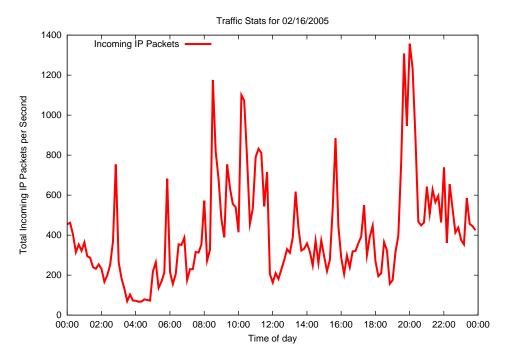

| D.7  | Incoming IP packets per second versus time on Feb 16, 2005                        | 125 |

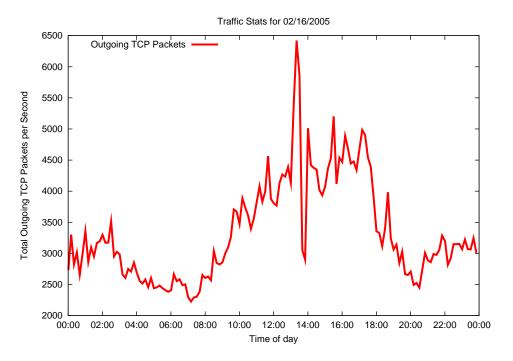

| D.8  | Outgoing TCP packets per second versus time on Feb 16, 2005                       | 126 |

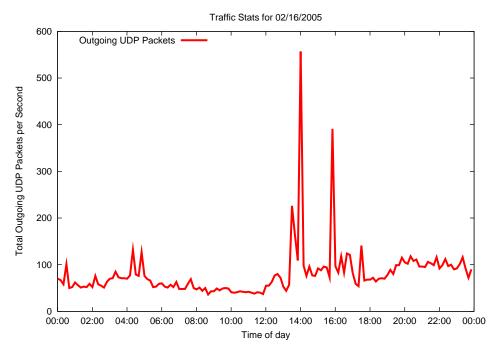

| D.9  | Outgoing UDP packets per second versus time on Feb 16, 2005                       | 126 |

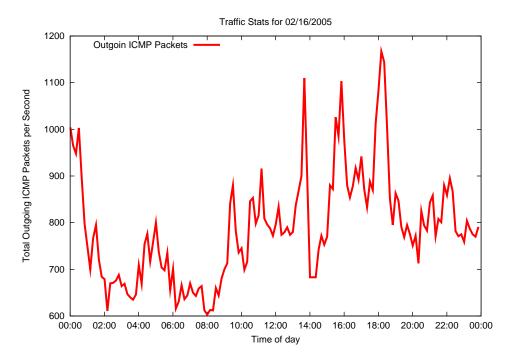

| D.10 | Outgoing ICMP packets per second versus time on Feb 16, 2005                      | 127 |

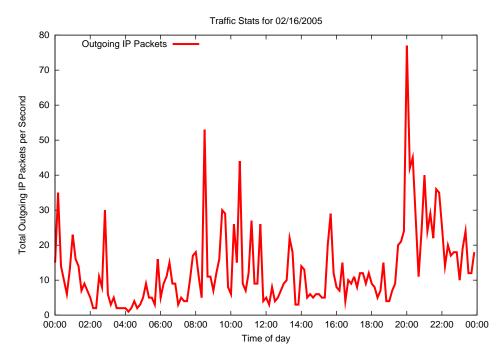

| D.11 | Outgoing IP packets per second versus time on Feb 16, 2005                        | 127 |

| D.12 | Matching headers per second versus time on Feb 16, 2005                           | 128 |

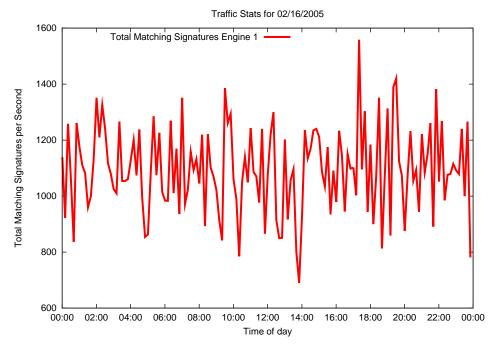

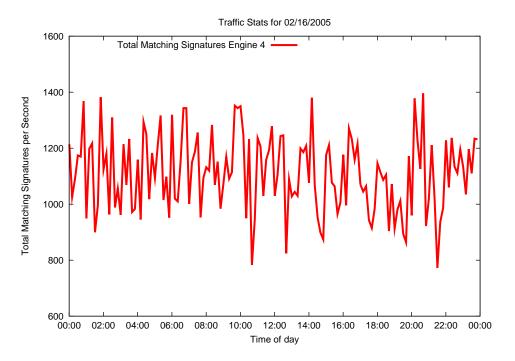

| D.13 | Matching 4-byte strings per second versus time on Feb 16, 2005                    | 128 |

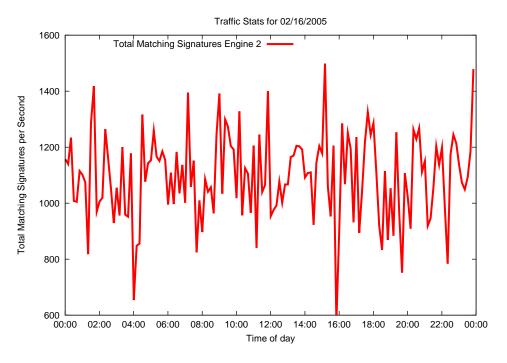

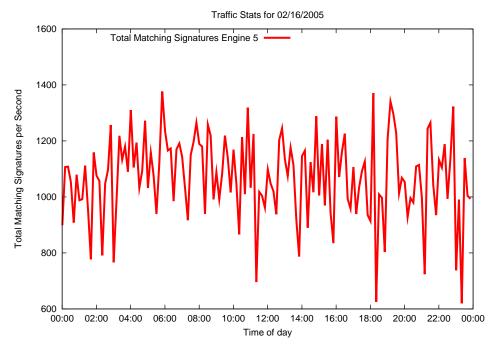

| D.14 | Matching 6-byte strings per second versus time on Feb 16, 2005                    | 129 |

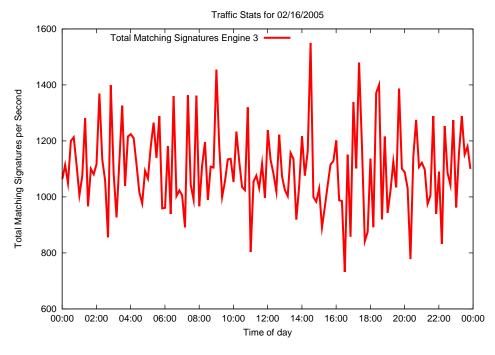

| D.15 | Matching 8-byte strings per second versus time on Feb 16, 2005                    | 129 |

| D.16 | Matching 10-byte strings per second versus time on Feb 16, 2005. $$               | 130 |

| D.17 | Matching 12-byte strings per second versus time on Feb 16, 2005                   | 130 |

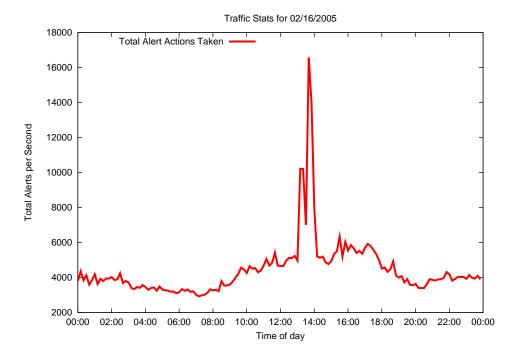

| D.18 Alert a  | ctions tal | ken per | second | versus | time o | n Feb  | 16, | 2005  | <br>131 |

|---------------|------------|---------|--------|--------|--------|--------|-----|-------|---------|

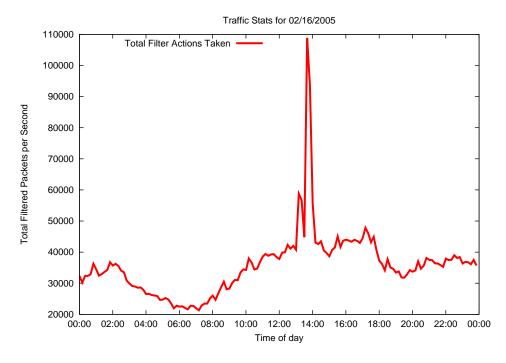

| D.19 Filter a | actions ta | ken pei | second | versus | time o | on Feb | 16, | 2005. | <br>131 |

# Acknowledgments

I would like to thank my advisor, Dr. Lockwood, for guiding me through the graduate school process. First, he supported my research. Second, his comments and suggestions helped me to fully develop ideas.

Additionally, I would like to thank the research sponsors Global Velocity and Boeing for not only the financial backing but also for the experience working with them has given me.

This work could not have been completed without the help, support, and patience of the members of the Reconfigurable Network Group in the Applied Research Laboratory.

Thanks are due to Todd Sproull for his numerous explanations about how to configure the lab; Sarang Dharmapurikar for explaining how to use a Bloom filter; Dave Lim for his work on the NID and tireless efforts to show me the problem is in my circuit; Dave Schuehler for tools to collect statistics and generate graphs as well as for the TCP wrapper; Haoyu Song for his help in configuring the Gigabit Ethernet line card; James Moscola for explaining how to use the IP wrappers; Phillip Jones for his numerous discussions and putting up with my ramblings; and finally to the remainder of the graduate students in the group (past and present) whose discussions and suggestions have been very helpful: Adam Covington, Chip Kastner, Andrew Levine, Jing Lu, Bharath Madhusudan, Jack Meier, Jeff Mitchell, Chris Neely, Shobana Padmanabhan, Abdel Rigumye, Dave Taylor, Qian Wan, and Chris Zuver.

Michael E. Attig

Washington University in Saint Louis May 2005

# Chapter 1

# Introduction

The world is now networked together. People, businesses, and governments share information and communicate nearly instantaneously. Individuals use the network for today's everyday tasks, such as banking, shopping, investing, or transferring pictures to friends. With sensitive information now available on-line, measures must be taken to ensure security and privacy. The electronic database of customer's credit card numbers, addresses, and phone numbers must be secured against identity theft. Similarly, medical institutions must secure patient information to protect medical information and maintain privacy.

High-speed network connections have dramatically increased the amount of information that can be communicated. However, these same high speed links have also aided the spread of malicious software. This 'malware' has been used to cripple businesses and bring servers to a standstill. Worm attacks by Nimda, Code Red, Slammer, SoBigF, and MSBlast have infected computers globally, clogged large computer networks, and degraded productivity, costing *billions* of dollars.

In order to protect networked systems, intrusion detection and prevention is necessary. Intrusion detection determines when harmful activities are being attempted. Intrusion prevention systems stop malware from infecting additional machines over the network. In the remainder of this chapter, the need for high speed rule processing systems is motivated, intrusion detection is defined, and the notion of rule processing for intrusion detection is explored. Finally, the contributions of the work are presented.

## 1.1 Motivation

Intrusions are unlikely to stop anytime soon. As more people, institutions, governments, and companies are networked together, the threat of intrusions increases. It is exceedingly difficult to build and maintain systems that are totally foolproof and have no security holes. Due to time-to-market constraints and because it takes too long to test all possible permutations of events that can produce an intrusion, it is unlikely that systems will ever be built that are totally secure. Network systems that can detect intrusions and prevent future intrusions are critical for security.

The work that was performed for this thesis had two main motivating factors. First, the monetary costs of intrusions, such as from spam, worms, and viruses is exponentially increasing. Solutions are needed now to combat this growing trend. Second, current rule processing systems are almost entirely implemented using software that runs on processors that cannot scale to process data on fast links. Hardware implementations allow for higher throughput, increase rule capacity, and take advantage of the parallelism that is inherent in rule processing.

## 1.1.1 Economic Impact of Intrusions and Spam

The proliferation of spam and malicious software circulating on the public network is extraordinary. First, the lost productivity costs institutions billions of dollars per year. Spam messages (that get by filters) require time to be deleted by the human recipients. The emergence of the billion-dollar security and spam industry is proof that this is a wide-scale problem, as evidenced by the emergence of companies like Symantec and McAfee and projects like SpamAssassin.

Second, the severity of malware forces companies to devote entire departments of full-time staff members to ensure that computing systems are patched with the latest software. Consider the MSBlast worm, a particularly annoying worm that affected more than eight million vulnerable Windows-based machines [63]. This worm rebooted computers after a minute of being operational, which was too little time to recognize the problem and install the patch. Future worms are expected to be more dangerous and could modify or delete data on infected computers. The estimated costs of certain worm and virus instances are summarized in Table 1.1. Nearly all major worm or virus outbreaks have cost billions of dollars [1, 123].

| Year | Incident | Worldwide Impact (US Dollars) |  |  |  |  |

|------|----------|-------------------------------|--|--|--|--|

| 2004 | Netsky   | \$11 Billion                  |  |  |  |  |

|      | Sasser   | \$6.25 Billion                |  |  |  |  |

|      | Mydoom.F | \$22.6 Billion                |  |  |  |  |

| 2003 | Sobig.F  | \$2 Billion                   |  |  |  |  |

|      | Blaster  | \$1.3 Billion                 |  |  |  |  |

|      | Slammer  | \$1.2 Billion                 |  |  |  |  |

| 2002 | KLEZ     | \$9 Billion                   |  |  |  |  |

| 2001 | Nimda    | \$635 Million                 |  |  |  |  |

|      | Code Red | \$2.62 Billion                |  |  |  |  |

|      | SirCam   | \$1.15 Billion                |  |  |  |  |

| 2000 | Love Bug | \$8.75 Billion                |  |  |  |  |

| 1999 | Melissa  | \$1.1 Billion                 |  |  |  |  |

|      | Explorer | \$1.02 Billion                |  |  |  |  |

Table 1.1: A summary of the cost of malicious code by incident [1, 123].

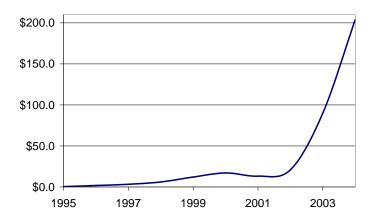

Finally, recent scams seek information from recipients. This tactic, known as phishing, has become very sophisticated and is difficult to prevent. In such cases, people unknowingly give sensitive information directly to the phishers who fraudulently pose as a reputable institution such as *PayPal*, *Citibank*, or *Washington Mutual*. In some cases, entire bank accounts are emptied and people are left wondering what happened. This scheme has become a major issue for law enforcement agencies. Many of the sources of such malware and phishing scams originate in countries with few laws to prevent such actions. The estimated worldwide impact of malware has grown exponentially, as shown in Figure 1.1.

# 1.1.2 Scalability

Databases of rules have been developed to identify malware. As new threats emerge, these rules increase in complexity. It was shown in [94] that the current volume of rules cannot be processed completely in software using today's PCs even at 100 Mbps rates. As link speeds increase to 1 Gbps, OC-48 (2.5 Gbps), OC-192 (10 Gbps), and beyond, systems are needed that accelerate the processing functions in hardware.

A hardware circuit can scale to process the increasingly complex rules at higher data rates. Hardware affords a higher degree of parallelism, which allows higher throughput to be maintained. A hardware device can be placed in line with a near zero increase in end-to-end latency. All network communication traverses through the

Figure 1.1: The cost of malicious code is increasing exponentially [1, 2, 123].

intrusion detection and prevention device so that as long as a rule for an intrusion has been written, the intrusion system discovers it. Only recently have components of intrusion systems been moved over to hardware to take advantage of parallelism, as discussed in detail in Chapter 2.

## 1.2 Intrusion Detection

Intrusion detection, in the general sense, identifies anomalous, inappropriate, or incorrect access to a system. There has been much work on defining the types of intrusions [9, 32, 34, 40, 80], distinguishing an intrusion from normal activity [16, 17, 57], and prototyping various intrusion systems [8, 31, 62, 70, 101, 105].

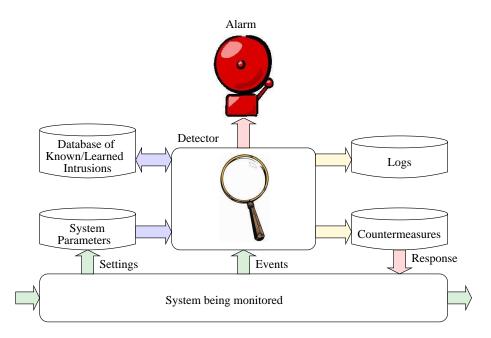

A high-level view of the components necessary to assemble an intrusion system is shown in Figure 1.2. At the center of the system is a component that detects intrusions. Four elements surround the detector that send and receive information. First, the detector has to know what events are classified as intrusions. When a new event occurs, the detector uses information about the current settings of the system as well as information about known intrusions to determine if this event is suspect. If the detector determines that the event is an intrusion, the event can be logged, a countermeasure can be taken, and an alarm can be raised. The potential countermeasures are represented as a database because multiple types of responses are available. An alarm could be signaled or the system could be modified to prevent similar events. When an alarm is triggered, an authority decides what further steps to take.

Figure 1.2: An intrusion system consists of a detector that recognizes known intrusions, learns new types of intrusions, and takes actions based on events that occur, raising an alarm if necessary. A similar diagram is given in [32].

Feedback from the detector to the database of known intrusions indicates that the ideal detector can discover new intrusions. The event may be an abnormal event or it may be patterned after a similar known intrusion. An authority can be consulted to determine whether the event is deemed an intrusion or not.

In the case of data networks, intrusion detection refers to the transfer of unwanted, malicious, or dangerous content over a network, and the system being monitored can be a web server, a database, or a cluster of computers. The intrusion may be as benign as spam or as harmful as a trojan horse [34] that infects a computer system by reading, writing, or even deleting files.

# 1.2.1 Types of Intrusions

Intrusions can take several forms. They can occur as abnormal, unauthorized, or unwanted system usage. Examples related to networking follow.

#### Unauthorized Access

Unauthorized access occurs when an individual gains access to a system they have no right to use. For example, a user may view web pages containing proprietary information that they have not been authorized to view.

#### Authorized Access

An intrusion can occur even if the credentials of the individual accessing the system are correct. For example, an intruder can fraudulently obtain account information such as login names and passwords. This is known as masquerading [16, 34, 40]. The system believes the intruder is authorized. This is the most difficult type of intrusion to detect since the detector must consider what is being accessed and what operations are being performed.

#### Spam

Spam is an unwanted electronic message from individuals or companies who send the message to people that may not desire to receive the message. These messages generally try to sell items, such as medication, loan applications, or pornography.

Phishing is a heinous form of spam where a message supposedly from an authoritative institution, such as a bank, e-commerce site, or government agency, directs the recipient to reply to the message or go to a web page and enter sensitive information. These messages can be quite persuasive, claiming accounts will be deactivated unless information is verified. Institutions have been formed in order to combat this problem [4], and tools are needed to protect network users.

#### Virus

A virus is a piece of malware hidden in files or emails. Once activated by the host, the virus replicates itself and spreads to additional hosts. Viruses generally spread via email, requesting that the recipient view an attachment. Clever virus writers writer code to search an infected host's address book to find additional recipients. The virus assumes the host identity when sending new email messages, increasing the likelihood that the target becomes infected.

#### Worm

A worm exploits a vulnerability in a system to execute code without the user actively starting it. The most common form of worm exploits buffer overflows, whereby the processor stack is subverted. Malicious code extends beyond the allocated buffer and is executed.

Worms take advantage of software flaws that may be difficult to find but are quick to exploit. The authors of [85] predicted that a worm could be written that infects all vulnerable hosts in less than 15 minutes. The prediction became reality in January 2003 when the Slammer worm infected over 90% of the vulnerable hosts within the first ten minutes [74, 75].

Internet users have been lucky so far in that the worms released have not appeared to be exceedingly malicious. However, even a fast propagating benign worm has the consequence of clogging networks with a flood of traffic. The authors of [76] developed guidelines to help stop the spread of such malicious code.

#### Denial of Service

Denial of Service (DoS) prevents legitimate users from accessing a system. DoS is accomplished by flooding a system with data that takes time to process. This inundation of events grinds services provided by the system to a standstill as each request is processed sequentially.

Web servers and email servers are frequent targets of such attacks, and the effects of a DoS attack can be very detrimental to those providing the service. E-commerce is especially sensitive to such attacks, since any loss of service can mean the loss of a customer's business.

#### 1.2.2 Methods of the Detection

There are three basic ways to detect an intrusion: anomaly detection, signature detection, and learning. The detector should signal an alarm when a breach of security is attempted.

#### **Anomaly Detection**

In anomaly detection, the detector recognizes deviations from standard behavior. Abnormal behavior is considered suspect. For example, a flood of traffic to a particular

TCP port could signal the beginning of a worm/virus outbreak or a DoS attack. However, anomaly detection can result in false alarms. The event in question may be a previously unseen event that is perfectly legitimate, such as the distribution of a software update. The use of thresholds and statistical analysis is used heavily to prevent false alarms [43, 55, 71, 72, 116].

#### Signature Detection

The second method of detection is to search packets or flows for known signatures. This requires that the detector know what to search for in advance. This could involve searching packet headers for suspect port numbers or IP addresses, or it could trigger searching payload for worm or virus signatures.

#### Learning

Finally, an effective detector should be able to learn about and react to new intrusion attempts. Learning requires training time for the system to determine what constitutes normal behavior and who are legitimate users [59]. Once trained, the system reacts to abnormal behavior and makes decisions on what actions to take.

One technique to learn about new signatures is to use thresholds to determine if a signature appears to be occurring too frequently. The authors of [71] used thresholds in conjunction with a timeout period to detect suspect occurrences of signatures.

# 1.2.3 Responses

Once an intrusion is detected, a response should be taken. The response could be to write to a log file or to email an administrator. The type of response depends on the way the system is configured. An intrusion detection and prevention system (IDPS) can be configured as either passive or active.

If the system is configured to be passive, as intrusion detection systems are, countermeasures cannot be performed to stop the intrusion because the system is only being monitored. Passive systems just inform an authority of security breaches. It is left to that authority to determine what to do about the problem.

Intrusion prevention systems can take countermeasures. In-line, active systems stop the flood of worms, which otherwise infect all vulnerable hosts in a matter of minutes. Countermeasures may include dropping an offending packet, terminating a user's connection, or blacklisting an IP or email address.

#### Effects of False Alarms

False alarms in intrusion detection systems are a serious problem. A false alarm occurs when an event or sequence of events causes an alarm to trigger even though the event was legitimate. For example, a false alarm may be raised at a web server if a certain web page becomes popular. A flash crowd, for example, occurs when there is a sudden surge of interest in a particular page. A term called "slashdotted" has been coined to describe the effect of large scale access to a web page when the URL is posted in an article on the www.slashdot.org website. An intrusion detection system (IDS) may determine this is a distributed DoS attack when, in fact, the web server cannot meet the demand of all the legitimate users who want to access the content.

When an alarm is raised, the reason for the alarm should be genuine. A system that generates many false alarms results in real alarms being overlooked. Additionally, when events occur too often, the logging and alarming mechanisms become overloaded. The authors of [12] and [90] discussed methodologies for benchmarking intrusion detection systems.

# 1.2.4 Who is the Authority?

Intrusion detection systems are used by many different types of people, ranging from individuals on home computers to the staff at large corporations. The focus of this work is for systems operating on large data networks, including local area networks (LANs) and wide are networks (WANs).

Members of an Information Technology (IT) department are generally granted authority to access networked systems, enforce networking policies, ensure the network is properly maintained, install new system software, and ensure the data within the network is only accessible by those with proper credentials. When an intrusion is detected, they respond and make the decisions about how to combat the intrusion.

# 1.3 Rule Processing for Intrusion Detection

Rule processing enables an authority to describe what constitutes an intrusion in his or her network. Rules can be written to perform header processing and/or payload signature detection. The rules are then used by the detector to scan events as they occur in the system being monitored.

Rule processing requires many resources and much computing power. Anomaly detection and learning algorithms could be used in tandem with rule processing systems by defining new intrusion rules.

Writing useful intrusion rules requires care. A poorly written rule can result in the generation of a large number of false alarms. New rules should be created so they uniquely define an intrusion. The architectures to be described report rule matches when the criteria specified in the rule is detected. Whether the circumstances surrounding the match actually represent an intrusion is left as future work.

### 1.3.1 Necessary Characteristics

To be an effective intrusion detection and prevention system, several key characteristics must be present. The system must operate in real-time, rather than using off-line processing that could occur hours after the malicious content has infected the network. This point implies that the IDPS must operate at network link rates.

The system must be highly adaptable in order to create a defense against malware [130]. Rule updates must occur quickly and be put into effect with minimal overhead. Taking the system down to change the rules is not an option. Forms of intrusion are continually changing, and systems must be flexible to counteract new security issues.

The system must also be efficient. It must concisely inform network administrators of what is occurring in the network. Ideally, the system reports enough information so future intrusions are blocked. For instance, future traffic from the same source could be dropped or given a lower priority. Additionally, a full record of the events leading up to the intrusion and the occurrence of the intrusion should be logged so that an authority can examine the circumstances surrounding the breach.

# 1.4 Thesis Objectives

This thesis set out to explore rule processing architectures to perform intrusion detection and prevention for networked systems with the following goals in mind:

- Provide a scalable architecture that supports processing of databases that contain a complete set of IDPS rules

- Provide mechanisms that do not disrupt normal traffic but block malicious attacks

- Provide an intuitive interface for modifying rules and processing alerts

- Provide an useful tool for network administrators

- Be implementable in a form factor that is cost-effective and space-efficient

If this system is to be placed between systems, it should operate in a non-intrusive way so as not to damage communication between the end systems.

If a tool is to be adopted, it should be intuitive, well documented, and serve an useful purpose. It should provide easy mechanisms to add or remove rules to the system and coherently report alarms to an authority.

Finally, the cost of the system should be considered. Current software-based intrusion systems can require racks of computers to monitor a connection [54]. If this functionality can be reduced to a single device, numerous benefits in terms of reducing power, space, and cooling can be achieved.

## 1.5 Contributions

This thesis presents three separate architectures to perform rule processing for network intrusion detection systems (NIDS) in reconfigurable hardware. The primary contributions of the work are:

- The development of a scalable rule processing framework for intrusion detection.

- The comparison of different approaches to rule processing.

- The development of reconfigurable modules that can be reused. Components that include Bloom filter hardware, a communication wrapper, and a statistics engine were developed that can be re-targeted for new projects.

- The analysis of real network traffic to determine the frequency of rule matches, benefiting architects in optimizing designs for actual network systems.

# 1.6 Thesis Outline

This thesis explores architectures to perform rule processing, laying a foundation for an efficient intrusion detection and prevention system in reconfigurable hardware. In Chapter 2, background information on processing technologies and networking protocols is provided. Snort, the most common IDS currently available, is discussed, with a focus on the algorithms used and the difficulties of directly porting Snort into hardware. Using Snort rules, the elements involved in rule processing are discussed: flow reconstruction, header processing, and pattern-matching. Related work is also provided.

Snort Lite is introduced in Chapter 3. This architecture implemented a subset of Snort rules on a single FPGA device. The complexity of the problem forced a number of simplifying assumptions. The design decisions are discussed, as well as some key observations that aid the design of the other two architectures. This architecture is considered the baseline implementation of an IDPS system.

In Chapter 4, the Snort Intrusion Filter for TCP (SIFT) architecture is presented. This architecture explored a hardware and software approach to rule processing. In SIFT, questionable data is sent to software for further processing. Questionable data is determined by a combination of header processing and content scanning. Only packets with a matching header or a keyword in the payload are forwarded to software. A key observation about rule match frequency was learned from this architecture.

In Chapter 5, the rule processing framework is described. This framework provided the most flexibility and the greatest amount of scalability. The architecture divided the header processing and content-scanning into separate modules and relied on an adjacent hardware processing circuit, called the rule processor, to determine whether intrusion rules matched.

In Chapter 6, system analysis and testing results are presented. Rather than present the individual testing results for each of the architectures in their respective chapters, these aspects are presented together here. All systems have their own unique benefits and excel in different ways.

In Chapter 7, the work is summarized. A discussion of potential future work in this area is provided.

The appendices are provided for reference. Appendix A discusses the control software for the three systems. Appendix B discusses the laboratory configuration to test each architecture. Appendix C explains the source code directory structure and how to use the provided scripts. The location of the source files is also given. Appendix D gives additional figures associated with system testing. Appendix E provides a list of acronyms used throughout this thesis.

# Chapter 2

# Background

In order to present rule processing architectures, a background on related work is needed. First, an overview of the technologies available to perform rule processing is given. Second, a brief description of the main networking protocols used by the system is given. Third, current rule processing systems are presented. Fourth, Snort is examined in detail, focusing on the underlying mechanics and its limitations. The rules currently found in Snort are analyzed, giving careful attention to rule characteristics. In the remaining three sections, details about the three main aspects of rule processing are given: TCP flow reconstruction, header processing, and string matching. Relevant related work is presented in the appropriate sections.

# 2.1 Implementation Medium

Techniques to perform rule processing can be implemented on a variety of mediums, from general purpose processors to custom hardware.

# 2.1.1 General Purpose Processors

The general purpose processor (GPP) offers the most flexibility to implement features for rule processing. Through the use of network interface cards (NICs), an ordinary PC can become a NIDS. Software exists today that can perform the tasks of rule processing. However, what advantage the PC gains in flexibility, it loses in raw computing power.

#### 2.1.2 Network Processors

Network processors, such as the Intel IXP 2800 [52], are built specifically for networking applications. A standard programming language allows the application designer to perform operations directly on network data at speeds much greater than a standard PC. This allows for relatively quick implementations.

The IXP 2800 has 16 parallel microengine processors, each of which can support up to eight processing threads. With large numbers of fast general purpose registers and multiple interfaces to external memory, a network processor can sustain high processing rates.

## 2.1.3 Field Programmable Gate Array

Field programmable gate array (FPGA) technology enables a fully-custom, high-speed, and flexible hardware implementation of data processing circuits. FPGAs use configurable logic blocks (CLBs) that contain look-up tables (LUTs) and flip-flops. Boolean logic functions are implemented using the CLBs. The speed of a design is determined by the location of the CLBs used and the routing delays incurred by connecting them. Fast, on-chip memories are also spread throughout current FPGAs.

By allowing soft modification of the hardware, the non recurring expense (NRE) of FPGA designs is lower than for ASIC designs. For low-volume applications or prototyping, FPGAs are the most cost-effective solution. The design cycle for a FPGA is considerably shorter than a fully-custom hardware solution. A developer writes VHDL [11, 126] or Verilog descriptions of hardware circuits, compiles the design for simulation, synthesizes the design, and finally maps the design into the appropriate part.

The architectures to be described use FPGA technology. Low-cost prototyping and reconfigurability are key factors for this decision.

# 2.1.4 Application Specific Integrated Circuit

An application specific integrated circuit (ASIC) is a fully-custom circuit that provides a low-power, high-speed solution to perform rule processing. However, due to the rigidity of the medium's fabrication method, once the design has returned from a fabrication plant, changes cannot be made without re-fabricating another circuit. This is not desirable for rule processing IDS since system requirements frequently

change. The NRE associated with an ASIC design is prohibitive for an application that needs to adapt continually. ASIC designs are generally only profitable for applications that produce hundreds of thousands of units.

# 2.2 Networking Protocols

The Internet can be described using a seven-layer model [86]. Starting at the lowest level, the layers are physical, data link, network, transport, session, presentation, and application. The physical layer is concerned with how bits of information are transferred from one location to another. The data link layer defines frame formats to specify where information begins and ends. The network layer defines how data is forwarded between hosts. The transport layer defines how data is transferred reliably. The session layer determines how communication sessions are created and authenticated. The presentation layer defines how data is internally represented for transmission. Finally, the application layer generates and/or interprets the data that has been transferred [56, 86, 117]. Rule processing resides in layers three and above.

## 2.2.1 Asynchronous Transfer Mode

The asynchronous transfer mode (ATM) protocol consists of 53-byte cells containing a virtual path identifier (VPI), virtual circuit identifier (VCI), header error correct code (HEC), and 48 bytes of payload data. The VPI and VCI are used to forward cells between destinations. An ATM network requires connections to be pre-allocated before data can be transferred. An allocation consists of configuring all VPI/VCI routing tables between the source and destination. The VPI field is used to route groups of VCIs together [86]. IP packets are transferred over ATM using specific protocols [48, 60].

#### 2.2.2 Internet Protocol

The Internet Protocol (IP) is used extensively today in the global network, providing a best-effort delivery of IP packets [87]. A typical IP packet header consists of 20 bytes, as shown in Figure 2.1. The main fields of the header are:

• ToS - type of service, used for applications requiring certain quality of service (QoS) guarantees

| $\begin{smallmatrix} 3 \\ 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 & 1 & 0 & 9 & 8 & 7 & 6 & 5 & 4 & 3 & 2 $ |        |          |                 |                 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|-----------------|-----------------|--|

| Ver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IHL    | ToS      | Total Length    |                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Identi | fication | Flags           | Fragment Offset |  |

| T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ΓL     | Protocol | Header Checksum |                 |  |

| Source Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |          |                 |                 |  |

| Destination Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |          |                 |                 |  |

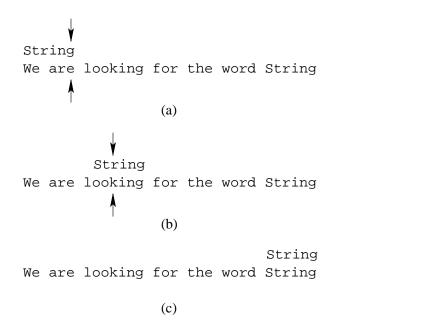

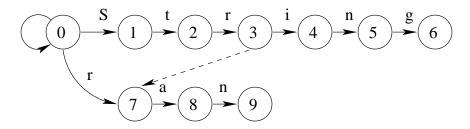

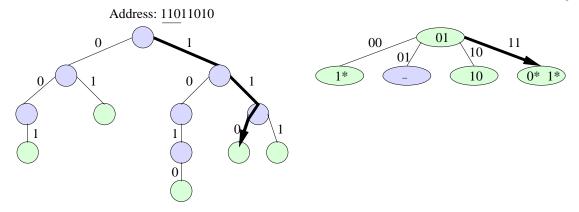

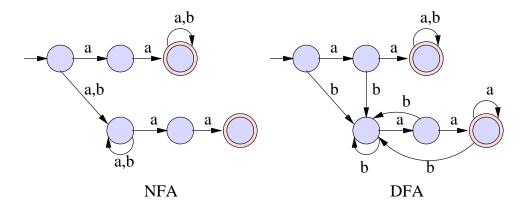

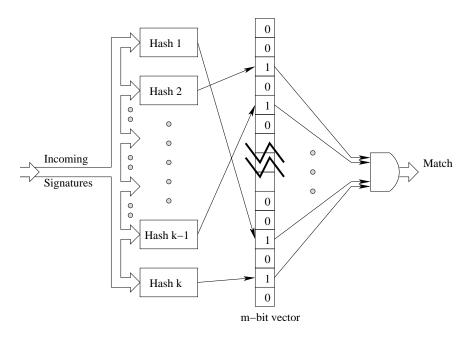

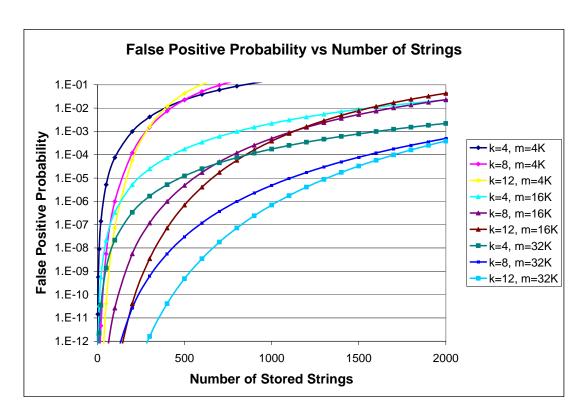

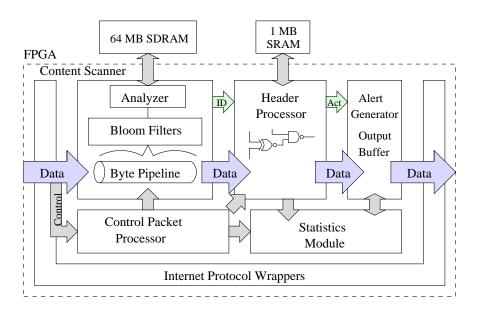

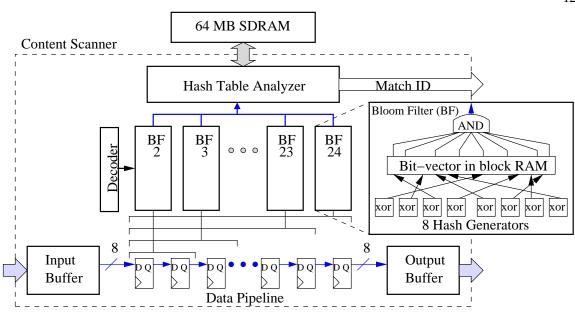

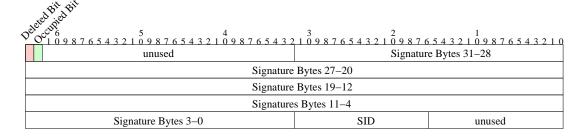

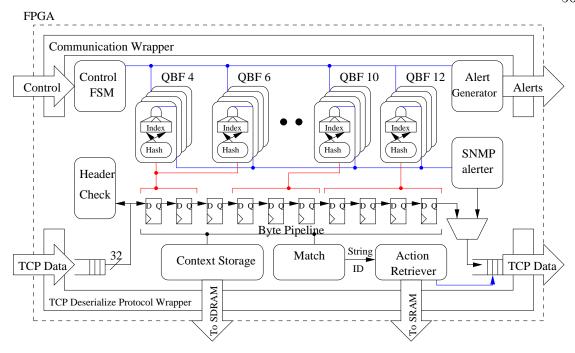

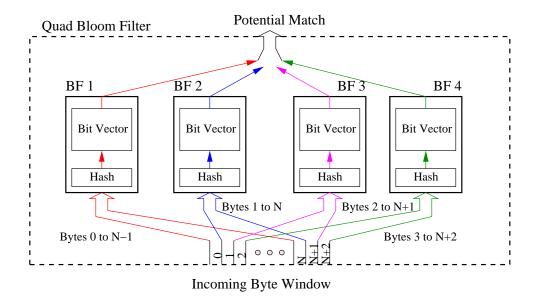

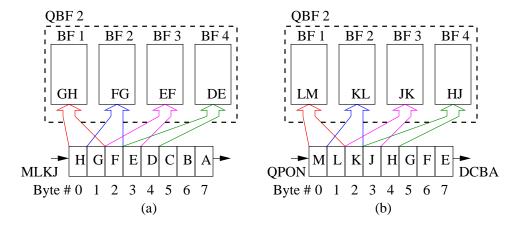

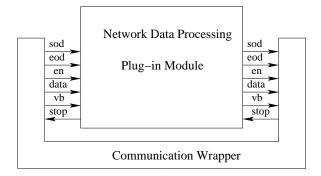

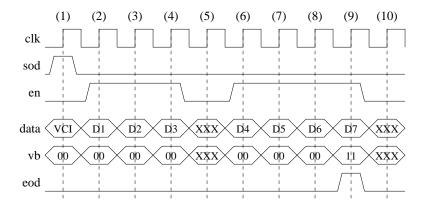

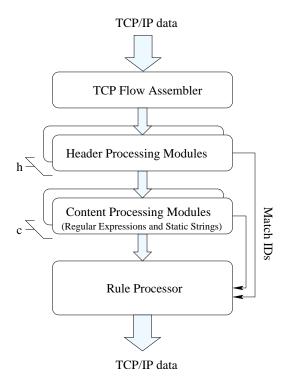

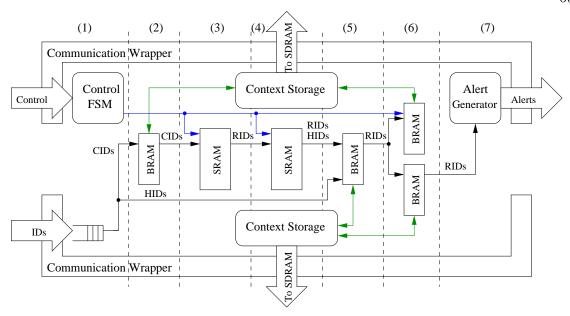

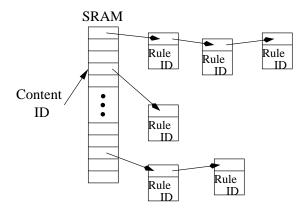

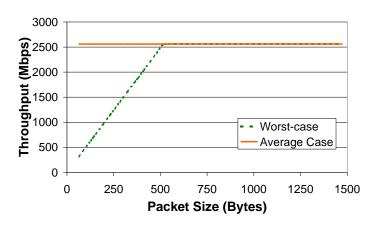

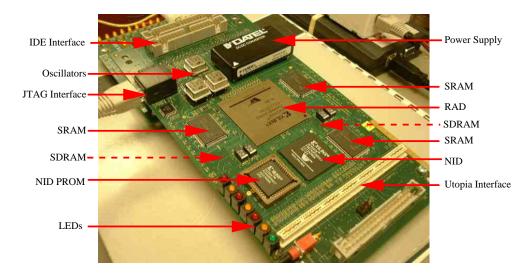

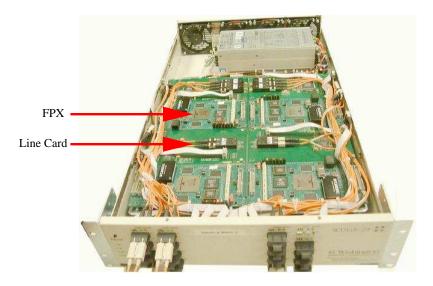

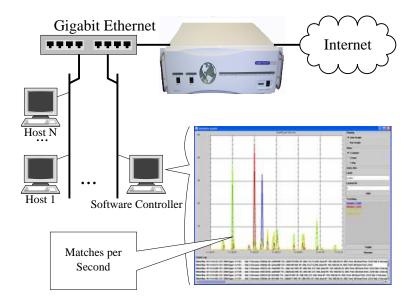

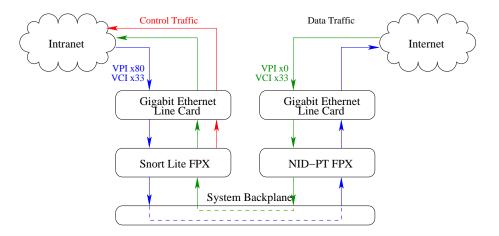

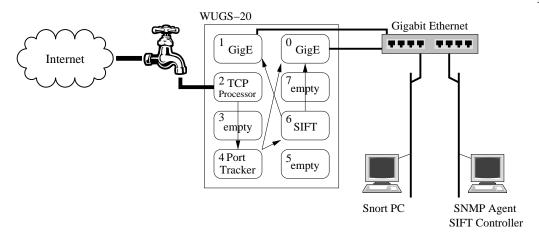

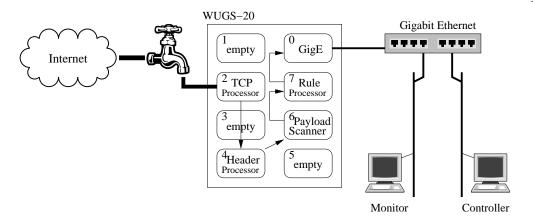

| Payload Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |          |                 |                 |  |