### Washington University in St. Louis Washington University Open Scholarship

All Computer Science and Engineering Research

**Computer Science and Engineering**

Report Number: WUCS-2006-43

2006-08-01

### Algorithms and Architectures for Network Search Processors

Sarang Dharmapurikar

The continuous growth in the Internet's size, the amount of data traffic, and the complexity of processing this traffic gives rise to new challenges in building high-performance network devices. One of the most fundamental tasks performed by these devices is searching the network data for predefined keys. Address lookup, packet classification, and deep packet inspection are some of the operations which involve table lookups and searching. These operations are typically part of the packet forwarding mechanism, and can create a performance bottleneck. Therefore, fast and resource efficient algorithms are required. One of the most commonly used techniques for such... **Read complete abstract on page 2**.

Follow this and additional works at: https://openscholarship.wustl.edu/cse\_research

#### **Recommended Citation**

Dharmapurikar, Sarang, "Algorithms and Architectures for Network Search Processors" Report Number: WUCS-2006-43 (2006). *All Computer Science and Engineering Research*. https://openscholarship.wustl.edu/cse\_research/917

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160.

This technical report is available at Washington University Open Scholarship: https://openscholarship.wustl.edu/ cse\_research/917

### Algorithms and Architectures for Network Search Processors

Sarang Dharmapurikar

#### Complete Abstract:

The continuous growth in the Internet's size, the amount of data traffic, and the complexity of processing this traffic gives rise to new challenges in building high-performance network devices. One of the most fundamental tasks performed by these devices is searching the network data for predefined keys. Address lookup, packet classification, and deep packet inspection are some of the operations which involve table lookups and searching. These operations are typically part of the packet forwarding mechanism, and can create a performance bottleneck. Therefore, fast and resource efficient algorithms are required. One of the most commonly used techniques for such searching operations is the Ternary Content Addressable Memory (TCAM). While TCAM can offer very fast search speeds, it is costly and consumes a large amount of power. Hence, designing cost-effective, power-efficient, and high-speed search techniques has received a great deal of attention in the research and industrial community. In this thesis, we propose a generic search technique based on Bloom filters. A Bloom filter is a randomized data structure used to represent a set of bit-strings compactly and support set membership queries. We demonstrate techniques to convert the search process into table lookups. The resulting table data structures are kept in the off-chip memory and their Bloom filter representations are kept in the on-chip memory. An item needs to be looked up in the off-chip table only when it is found in the on-chip Bloom filters. By filtering the off-chip memory accesses in this fashion, the search operations can be significantly accelerated. Our approach involves a unique combination of algorithmic and architectural techniques that outperform some of the current techniques in terms of cost-effectiveness, speed, and power-efficiency.

Department of Computer Science & Engineering

2006-43

# Algorithms and Architectures for Network Search Processors, Doctoral Dissertation, August 2006

Authors: Sarang Dharmapurikar

Corresponding Author: sarang@arl.wustl.edu

Web Page: http://www.arl.wustl.edu/projects/fpx/reconfig.htm

Abstract: The continuous growth in the Internet's size, the amount of data traffic, and the complexity of processing this traffic gives rise to new challenges in building highperformance network devices. One of the most fundamental tasks performed by these devices is searching the network data for predefined keys. Address lookup, packet classification, and deep packet inspection are some of the operations which involve table lookups and searching. These operations are typically part of the packet forwarding mechanism, and can create a performance bottleneck. Therefore, fast and resource efficient algorithms are required. One of the most commonly used techniques for such searching operations is the Ternary Content Addressable Memory (TCAM). While TCAM can offer very fast search speeds, it is costly and consumes a large amount of power. Hence, designing cost-effective, power-efficient, and high-speed search techniques has received a great deal of attention in the research and industrial community.

In this thesis, we propose a generic search technique based on Bloom filters. A Bloom filter is a randomized data structure used to represent a set of bit-strings compactly and support set membership queries. We demonstrate techniques to convert the search process into table lookups. The resulting table data structures are

Type of Report: Other

### WASHINGTON UNIVERSITY THE HENRY EDWIN SEVER GRADUATE SCHOOL DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

#### ALGORITHMS AND ARCHITECTURES FOR

#### NETWORK SEARCH PROCESSORS

by

Sarang Dharmapurikar, B.E.

Prepared under the direction of Professor John W. Lockwood

A dissertation presented to the Henry Edwin Sever Graduate School of Washington University in partial fulfillment of the requirements for the degree of

DOCTOR OF SCIENCE

August 2006

Saint Louis, Missouri

### WASHINGTON UNIVERSITY THE HENRY EDWIN SEVER GRADUATE SCHOOL DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

#### ABSTRACT

### ALGORITHMS AND ARCHITECTURES FOR NETWORK SEARCH PROCESSORS

by

Sarang Dharmapurikar

ADVISOR: Professor John W. Lockwood

August 2006 Saint Louis, Missouri

The continuous growth in the Internet's size, the amount of data traffic, and the complexity of processing this traffic gives rise to new challenges in building high-performance network devices. One of the most fundamental tasks performed by these devices is searching the network data for predefined keys. Address lookup, packet classification, and deep packet inspection are some of the operations which involve table lookups and searching. These operations are typically part of the packet forwarding mechanism, and can create a performance bottleneck. Therefore, fast and resource efficient algorithms are required. One of the most commonly used techniques for such searching operations is the Ternary Content Addressable Memory (TCAM). While TCAM can offer very fast search speeds, it is costly and consumes a large amount of power. Hence, designing cost-effective, power-efficient, and high-speed search techniques has received a great deal of attention in the research and industrial community.

In this thesis, we propose a generic search technique based on Bloom filters. A Bloom filter is a randomized data structure used to represent a set of bit-strings compactly and support set membership queries. We demonstrate techniques to convert the search process into table lookups. The resulting table data structures are kept in the off-chip memory and their Bloom filter representations are kept in the on-chip memory. An item needs to be looked up in the off-chip table only when it is found in the on-chip Bloom filters. By filtering the off-chip memory accesses in this fashion, the search operations can be significantly accelerated. Our approach involves a unique combination of algorithmic and architectural techniques that outperform some of the current techniques in terms of cost-effectiveness, speed, and power-efficiency.

copyright by Sarang Dharmapurikar 2006 To Aai, Baba, and Ajji

# Contents

| Li       | st of | Tables                               | vii  |

|----------|-------|--------------------------------------|------|

| Li       | st of | Figures                              | ix   |

| A        | ckno  | wledgments                           | xiii |

| 1        | Intr  | roduction                            | 1    |

|          | 1.1   | Searching in the Context of Networks | 2    |

|          | 1.2   | Common Search Techniques             | 6    |

|          | 1.3   | Thesis Organization                  | 10   |

| <b>2</b> | Blo   | om Filters and Variants              | 12   |

|          | 2.1   | Bloom Filters                        | 12   |

|          |       | 2.1.1 False Positive Probability     | 14   |

|          | 2.2   | Counting Bloom Filters               | 15   |

|          | 2.3   | Extended Bloom Filters               | 16   |

|          | 2.4   | Spectral Bloom Filters               | 17   |

|          | 2.5   | Bloomier Filters                     | 18   |

|          | 2.6   | Compressed Bloom Filters             | 21   |

| 3        | Lo    | ngest Prefix Matching                | 23   |

|          | 3.1   | Introduction                         | 23   |

|          | 3.2   | Related Work                         | 24   |

|          | 3.3   | Our Approach                         | 26   |

|          |       | 3.3.1 Supporting Incremental Updates | 28   |

|          |       | 3.3.2 Analysis                       | 29   |

|          | 3.4   | Optimizations                        | 34   |

|          |       | 3.4.1 Direct Indexing                | 35   |

|          |       | 3.4.2 Controlled Prefix Expansion    | 37   |

|          | 3.5 | Performance Simulations                   |

|----------|-----|-------------------------------------------|

|          | 3.6 | Implementation Considerations             |

|          |     | 3.6.1 Hash Functions                      |

|          | 3.7 | Summary 48                                |

| 4        | Pac | ket Classification                        |

|          | 4.1 | Introduction                              |

|          | 4.2 | Related Work                              |

|          | 4.3 | Naive Crossproducting Algorithm           |

|          | 4.4 | Multi-Subset Crossproducting Algorithm    |

|          | 4.5 | Intelligent Grouping                      |

|          |     | 4.5.1 A Problem Formulation               |

|          |     | 4.5.2 Overlap-Free Grouping               |

|          |     | 4.5.3 Limiting the Number of Subsets      |

|          | 4.6 | Architecture                              |

|          |     | 4.6.1 Hash Table Architecture             |

|          |     | 4.6.2 Memory Requirement                  |

|          |     | 4.6.3 Classification Throughput           |

|          | 4.7 | Summary                                   |

| <b>5</b> | A S | imple Multi-String Matching Algorithm     |

|          | 5.1 | Introduction                              |

|          | 5.2 | Related Work                              |

|          | 5.3 | A Simple Multi-Pattern Matching Algorithm |

|          | 5.4 | Analysis                                  |

|          | 5.5 | Evaluation with Snort                     |

|          | 5.6 | Summary 103                               |

| 6        | Acc | elerated Aho-Corasick Algorithm           |

|          | 6.1 | Aho-Corasick Algorithm                    |

|          | 6.2 | A Scalable and High-Speed Algorithm       |

|          |     | 6.2.1 Basic Ideas                         |

|          |     | 6.2.2 Data Structures and Algorithm       |

|          | 6.3 | Analysis                                  |

|          |     | $6.3.1$ Worst Case Text $\ldots$ $118$    |

|    |        | 6.3.2  | Ran   | dom   | Te   | xt  | <br>• |  | <br> | • | <br>• | • | <br>• |  | • | <br>• | • | 120 |

|----|--------|--------|-------|-------|------|-----|-------|--|------|---|-------|---|-------|--|---|-------|---|-----|

|    |        | 6.3.3  | Synt  | theti | сТ   | ext |       |  | <br> |   | <br>• | • |       |  | • |       |   | 121 |

|    | 6.4    | Evalua | ation | with  | n Sn | ort | •     |  | <br> |   | <br>  | • | <br>• |  | • |       | • | 122 |

|    | 6.5    | Summ   | ary   | •••   |      |     | <br>  |  | <br> |   | <br>  | • |       |  | • |       |   | 125 |

| 7  | Con    | clusio | ns.   |       |      |     | <br>• |  | <br> | • | <br>• | • |       |  | • | <br>• |   | 127 |

| Re | eferei | nces . |       | •••   |      |     | <br>• |  | <br> | • | <br>• | • | <br>• |  |   |       | • | 132 |

| Vi | ta .   |        |       |       |      |     | <br>  |  | <br> |   | <br>  |   |       |  |   |       | • | 136 |

# List of Tables

| 3.1 | Observed average number of hash probes per lookup for 15 IPv4                                                               |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------|-----|

|     | BGP tables on various system configurations dimensioned with M                                                              |     |

|     | $= 2 Mb. \dots \dots$ | 41  |

| 4.1 | Results with different rule sets. $\delta$ denotes the expansion factor on                                                  |     |

|     | the original rule set after naïve crossproduct. $\alpha$ denotes the expan-                                                 |     |

|     | sion factor on the original rule set after Multi-subset Crossprod-                                                          |     |

|     | uct. $\beta$ denotes the <i>percentage</i> of the original rules which are treated                                          |     |

|     | as spoilers.                                                                                                                | 80  |

| 4.2 | The performance of different algorithms with different parame-                                                              |     |

|     | ters. $M_{on}$ and $M_{of}$ denote the average on-chip and off-chip memory                                                  |     |

|     | in bytes per rule. The throughput is in Million Packets per sec-                                                            |     |

|     | ond. Throughput was computed for different number of matching                                                               |     |

|     | rules per packets, $p \le 4$ , $p = 6$ , $p = 8$ . When $p \le 4$ , LPM is the                                              |     |

|     | bottleneck and throughput is decided by how wide the LPM entry                                                              |     |

|     | is                                                                                                                          | 86  |

| 5.1 | The evaluation of our algorithm with Snort string set. A syn-                                                               |     |

|     | thetic text was generated with a string concentration of one true                                                           |     |

|     | string in every 100 characters. The system operates at a speed of                                                           |     |

|     | F = 250 MHz. An off-chip QDRII-SRAM operating at the same                                                                   |     |

|     | frequency was assumed to be available for storing the hash tables.                                                          |     |

|     | The total number of strings considered was 1576.                                                                            | 102 |

| 6.1 | Transition table of JACK-FA. This table can be implemented in                                                               |     |

|     | the off-chip memory as a hash table                                                                                         | 113 |

| 6.2 | Results of Bloom filter construction.                                                                                       | 123 |

# List of Figures

| 2.1  | Illustration of a Bloom filter                                            | 13 |

|------|---------------------------------------------------------------------------|----|

| 2.2  | Illustration of an Extended Bloom filter                                  | 16 |

| 2.3  | Illustration of Bloomier filter                                           | 19 |

| 3.1  | Basic configuration of Longest Prefix Matching using Bloom filters.       | 26 |

| 3.2  | Pseudo-code for the LPM algorithm                                         | 27 |

| 3.3a | Pseudo-code for adding a prefix                                           | 28 |

| 3.3b | Pseudo-code for deleting a prefix                                         | 29 |

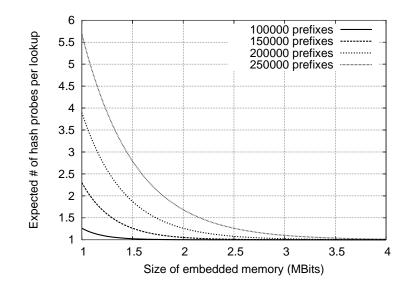

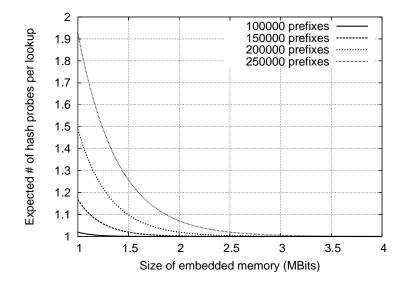

| 3.4  | The average number of hash probes per lookup, $	au_{avg1}$ , versus the   |    |

|      | total embedded memory size, $M$ , for various values of total pre-        |    |

|      | fixes, $N$ , using a basic configuration for IPv4 with 32 Bloom filters.  | 34 |

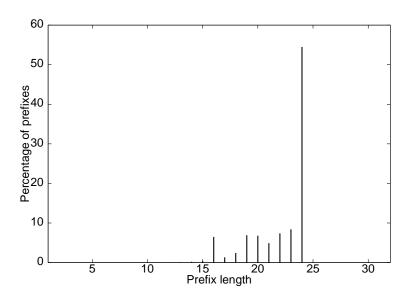

| 3.5  | Average prefix length distribution for IPv4 BGP table snapshots.          | 37 |

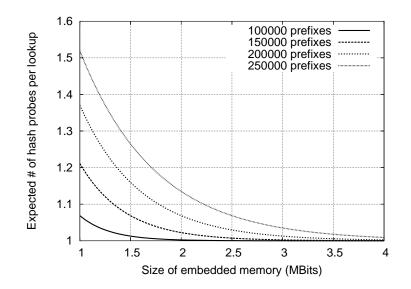

| 3.6  | Average number of hash probes per lookup, $	au_{avg2}$ , versus total     |    |

|      | embedded memory size, $M$ , for various values of total prefixes, $N$ ,   |    |

|      | using a direct lookup array for prefix lengths $1 \dots 20$ and 12 Bloom  |    |

|      | filters for prefix lengths 2132                                           | 37 |

| 3.7  | Average number of hash probes per lookup, $	au_{avg3}$ , versus total     |    |

|      | embedded memory size, $M$ , for various values of total prefixes,         |    |

|      | $N$ , using a direct lookup array for prefix lengths $1 \dots 20$ and two |    |

|      | Bloom filters for prefix lengths $21 \dots 24$ and $25 \dots 32$          | 39 |

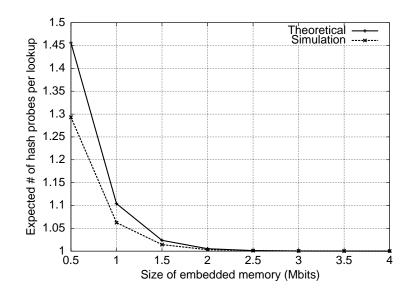

| 3.8  | Average number of hash probes per lookup for Configuration 3              |    |

|      | programmed with database 1, $N = 116,819$ , for three embedded            |    |

|      | memory sizes, $M$ .                                                       | 42 |

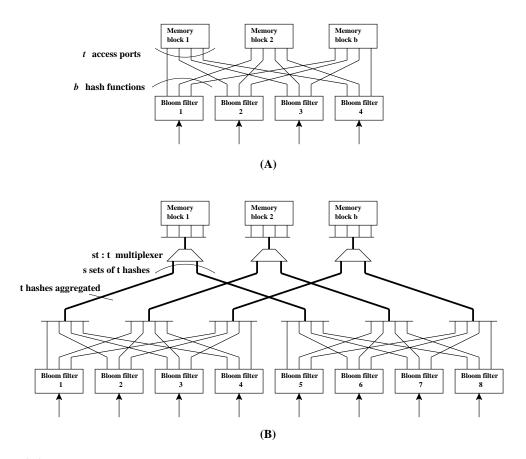

| 3.9  | Using fixed size memory blocks with fixed number of ports to              |    |

|      | construct multiple Bloom filters. (A) A group of $t$ Bloom filter         |    |

|      | can be constructed using $b$ memory blocks each with $t$ ports. (B)       |    |

|      | Multiple sets of $t$ Bloom filters can share the same set of $b$ memory   |    |

|      | blocks by using the multiplexers.                                         | 44 |

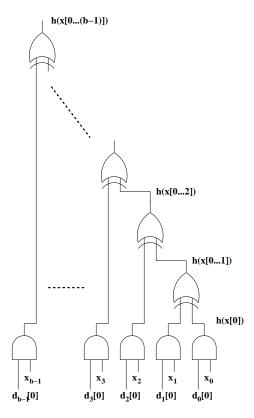

| 3.10 | Computation of a single bit in a hash function. If the hash value    |    |

|------|----------------------------------------------------------------------|----|

|      | is represented as $l$ bits then $l$ such circuits are required for a |    |

|      | complete hash function.                                              | 47 |

| 4.1  | The pseudo-code for building a crossproduct table.                   | 55 |

| 4.2  | The pseudo-code classifying a packet.                                | 56 |

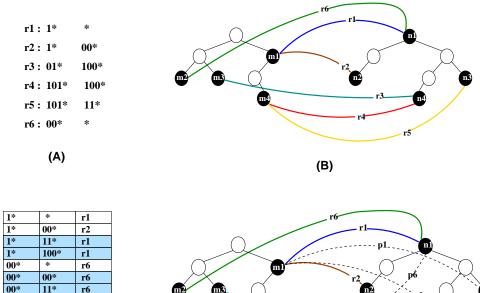

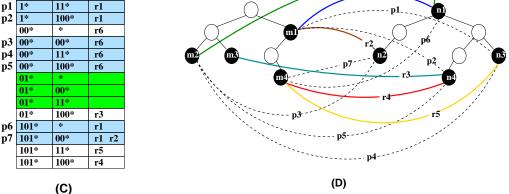

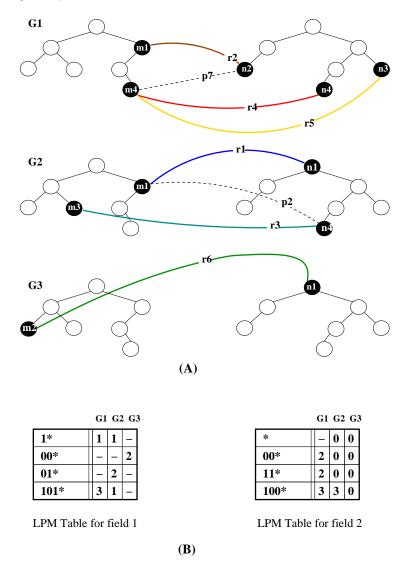

| 4.3  | Illustration of basic ideas. (A) Rule set (B) Rule representation    |    |

|      | using trie (C) Crossproduct table (D) Representation of original     |    |

|      | rules and pseudo-rules using trie                                    | 57 |

| 4.4  | Dividing rules in separate subsets to reduce overlap. The corre-     |    |

|      | sponding LPM tables                                                  | 59 |

| 4.5  | The pseudo-code classifying a packet using multiple crossproduct     |    |

|      | $	ext{tables.}$                                                      | 61 |

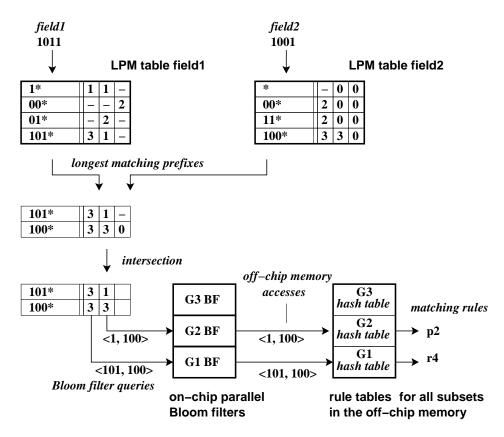

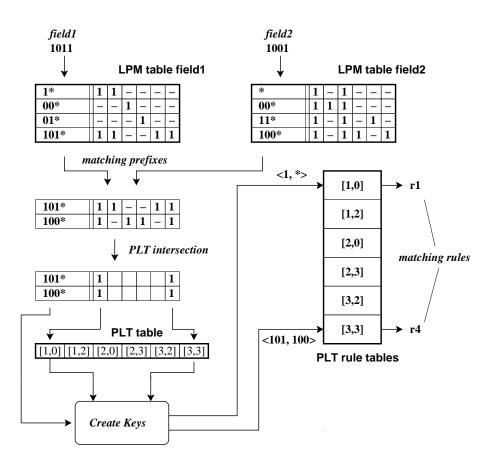

| 4.6  | Illustration of the flow of algorithm. First, LPM is performed on    |    |

|      | each field. The result is used to form a set of $g$ tuples, each of  |    |

|      | which indicates how many prefix bits to use for constructing keys    |    |

|      | corresponding to that subset. The keys are looked up in Bloom        |    |

|      | filters first. Only the keys matched in Bloom filters are used to    |    |

|      | query the corresponding rule subset hash table kept in the off-chip  |    |

|      | memory                                                               | 62 |

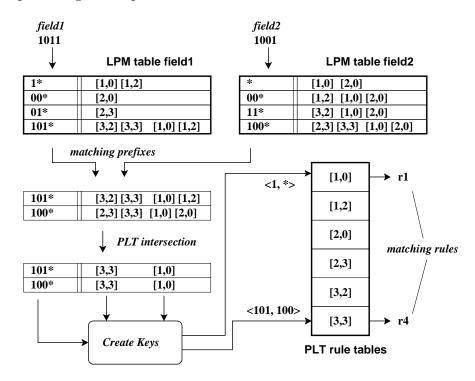

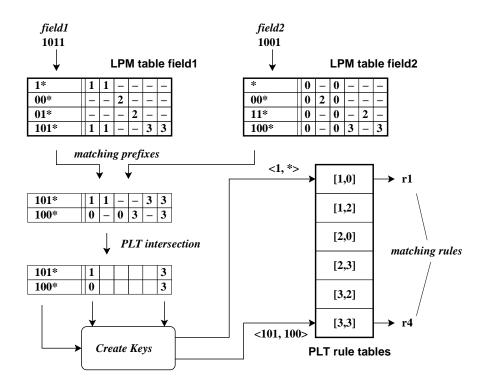

| 4.7  | Illustration of the Tuple Space Search algorithm                     | 68 |

| 4.8  | Illustration of the Tuple Space Search algorithm with an alterna-    |    |

|      | tive LPM table structure.                                            | 70 |

| 4.9  | The LPM table can be compressed further by using a bit map.          | 71 |

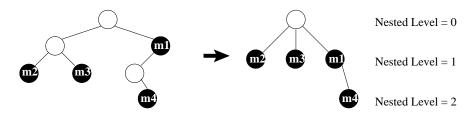

| 4.10 | Illustration of Nested Level Tree                                    | 73 |

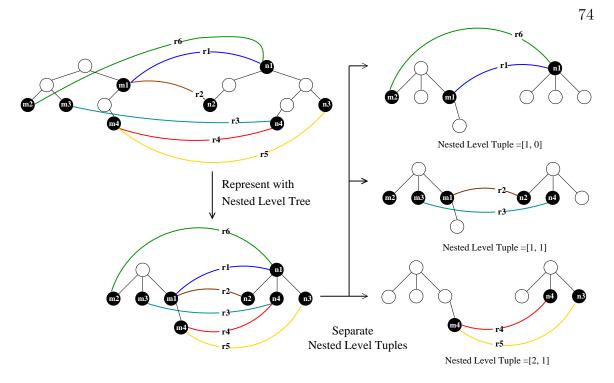

| 4.11 | Overlap free grouping of rules                                       | 74 |

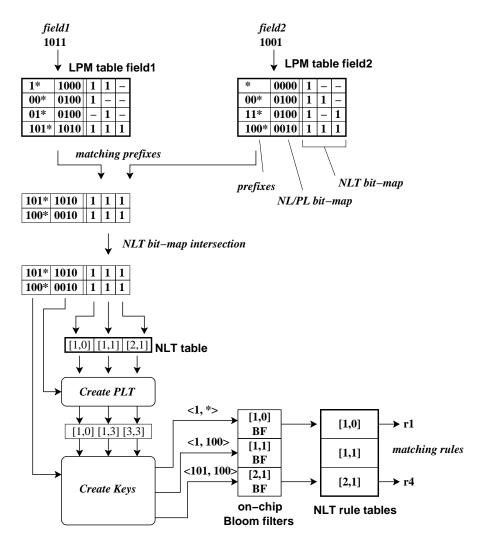

| 4.12 | Using NLT based grouping to form the subsets. Each prefix en-        |    |

|      | try in LPM table needs a NL/PL bitmap and another bitmap             |    |

|      | indicating the NLTs to which the prefix or its sub-prefixes belong.  | 76 |

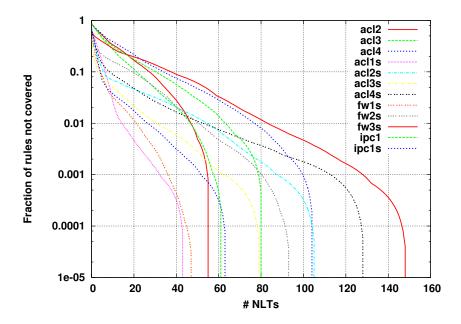

| 4.13 | The distribution of the left over rules across NLTs. A large num-    |    |

|      | ber of rules is covered by a few NLTs. Less than $10\%$ the rules    |    |

|      | are outside the first 40 NLTs. Only the rule sets with more than     |    |

|      | 40 NLTs are represented for the purpose of clarity.                  | 77 |

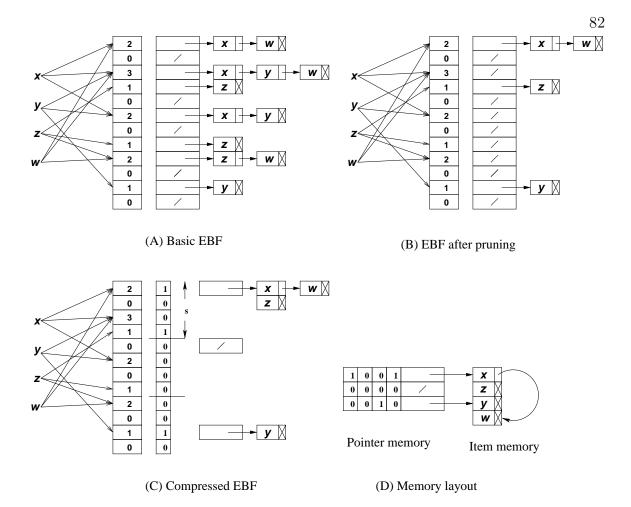

| 4.14 | Illustration of Fast Hash Table and its compression. The example        |

|------|-------------------------------------------------------------------------|

|      | is borrowed from [29]. (A) The basic FHT (B) FHT after prun-            |

|      | ing (C) Compressing pointer array (D) Arranging pointer array           |

|      | compactly in memory                                                     |

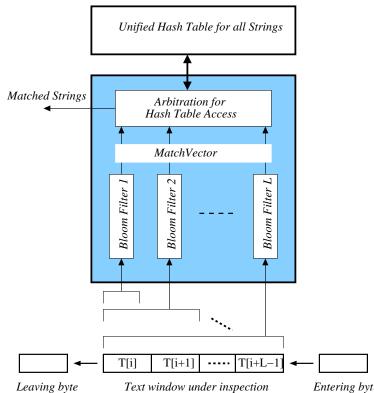

| 5.1  | A string matching machine consisting of multiple Bloom filters          |

|      | each of which detects strings of a unique length. The longest           |

|      | string is of length $L$ . Upon a Bloom filter match, the string is      |

|      | looked up in the corresponding hash table. After inspecting a           |

|      | window it is moved by a byte and the lookup procedure is repeated. $97$ |

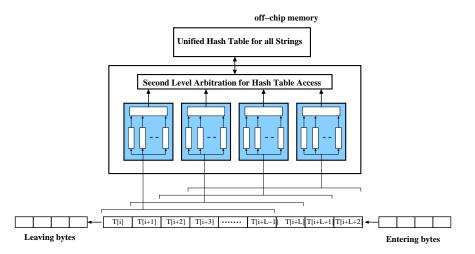

| 5.2  | String matching algorithm which essentially performs the Longest        |

|      | Prefix Matching (LPM) over the text window                              |

| 5.3  | Using multiple parallel engines for better throughput                   |

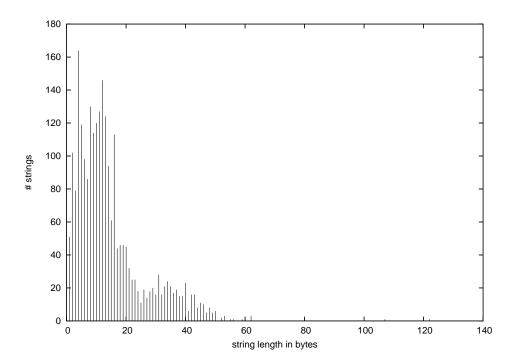

| 5.4  | String length distribution. Maximum string length is 122 bytes. 100     |

| 6.1  | Illustration of basic technique for handling long strings 104           |

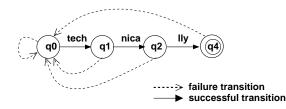

| 6.2  | Building an Aho-Corasick FA for a set of strings. Failure transi-       |

|      | tions to only non $q_0$ states are shown for the purpose of clarity.    |

|      | All other states make a failure transition to $q_0$                     |

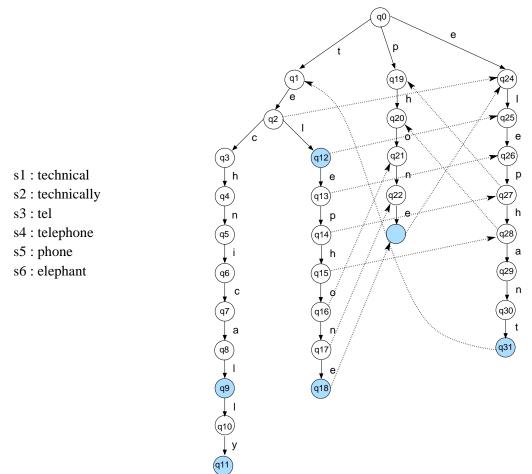

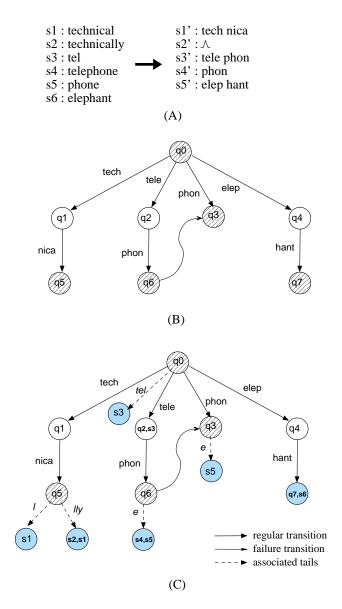

| 6.3  | (A) The original string set and modified string set. The space          |

|      | between the $k$ character boundary is shown as a demarcation (B)        |

|      | Jump-ahead Aho-Corasick (JACK) FA. The nodes with a dashed              |

|      | pattern indicate a state corresponding to a matching substring.         |

|      | Failure transition to only non $q_0$ states are shown. Failure tran-    |

|      | sitions of the remaining states are to $q_0$ (C) JACK-FA with tails     |

|      | associated with states                                                  |

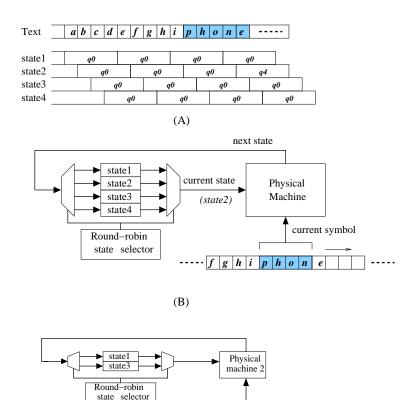

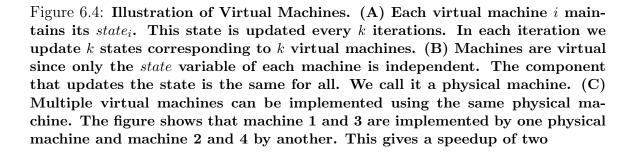

| 6.4 | Illustration of Virtual Machines. (A) Each virtual machine $i$ main-                 |     |

|-----|--------------------------------------------------------------------------------------|-----|

|     | tains its $state_i$ . This state is updated every k iterations. In each              |     |

|     | iteration we update $k$ states corresponding to $k$ virtual machines.                |     |

|     | (B) Machines are virtual since only the state variable of each ma-                   |     |

|     | chine is independent. The component that updates the state is the                    |     |

|     | same for all. We call it a physical machine. (C) Multiple virtual                    |     |

|     | machines can be implemented using the same physical machine.                         |     |

|     | The figure shows that machine 1 and 3 are implemented by one                         |     |

|     | physical machine and machine 2 and 4 by another. This gives a                        |     |

|     | speedup of two                                                                       | 111 |

| 6.5 | Algorithm for detecting strings.                                                     | 114 |

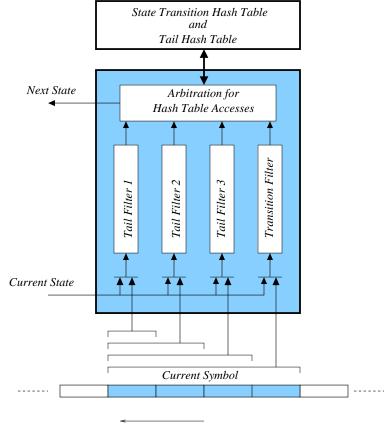

| 6.6 | Implementation of a physical machine. For this figure, $k = 4$ .                     |     |

|     | The pair $\langle state, prefix \rangle$ is looked up in the associated Bloom filter |     |

|     | before off-chip table accesses.                                                      | 115 |

| 6.7 | Algorithm for the Longest Prefix Matching.                                           | 116 |

## Acknowledgments

My inexpressible thanks to my research advisor, Dr. John W. Lockwood, for providing me an opportunity to pursue a D.Sc. under his mentorship. John provided me the freedom and support to explore the research topics of my interest. His passion for solving the *real* problems and making a difference in the world has always been inspiring. His emphasis on producing actual working systems has made me think about my research problems from a completely practical perspective. He has been very patient with me and took out time for discussions without fail even while managing a team of more than fifteen graduate students. I've always thoroughly enjoyed our non-academic, lengthy discussions and benefited from both his academic and personal advice.

Many thanks to Dr. Jonathan Turner for his invaluable guidance. It is indeed an honor to have worked with such a renowned scientist. I have learned much while closely working with him on various projects at the Applied Research Laboratory (ARL). His high-quality standards for research at ARL made me work harder to produce an interesting dissertation. His dedication to his work and unbeatable enthusiasm for his goals have been a continuous source of inspiration to me.

I also wish to thank Dr. Vern Paxson with whom I worked during the summer of 2004 at ICSI Center for Internet Research (ICIR). He introduced me to a wealth of new problems in network security and set a course for long-term collaboration. I am grateful to him for including me in the project investigating the hardware support for network security and analysis systems.

Thanks to Dr. Patrick Crowley who agreed to collaborate on exploring the packet buffer optimization problem which resulted in our Globecom'05 paper. I would also like to thank my committee members Dr. Jeremy Buhler and Dr. Ronald Indeck for their important suggestions on the technical content.

I am thankful to all my coauthors whose contributions assisted me in producing interesting publications. Particularly, I wish to thank Praveen Krishnamurthy, David Taylor, Todd Sproull, Haoyu Song, and Sailesh Kumar for their significant contributions to the publications we authored. Brainstorming sessions with them were not only great fun but also helped me shape my research ideas. Thanks to Ramaprabhu Janakiraman for introducing me to the Bloom filters.

I would like to thank Jean Grothe, Tom Evola and Jason Marqart who helped me with the issues related to my immigration status. Thanks to Myrna Harbison, Sharon Matlock, Peggy Fuller and Stella Sung for their efforts to make life easy for me and my fellow graduate students. Many thanks to Robyn Brinks for her help in editing this manuscript.

I am grateful to my research sponsors, NSF (Grant 0096052), Global Velocity, SAIC, and Agilent Labs for supporting my work.

My tenure at Washington University has been fun-filled because of my friends, roommates, and lab-mates. Many thanks to them for spicing up my stay in St. Louis.

Finally, I would like to thank my parents, grandmother, brother, sister, and my fiancée, Rashmi, for their unconditional love, constant support, and encouragement. What they have done for me can not be expressed in words. I admire their patience while I have been away from home.

Sarang Dharmapurikar

Washington University in Saint Louis August 2006

# Chapter 1

# Introduction

The Internet is one of the most important inventions of the twentieth century. Starting from a small network of computers developed for the defense purposes, the Internet rapidly evolved into a very large and complex network that is now a critical infrastructure for global communication, information exchange, and commerce. Today's Internet has millions of hosts connected to it. The layered architecture of the Internet allows independent development of services that can be deployed on top of the physical network. Day by day, innovative services are introduced which demand more complex data processing and faster data routing. The performance pressure on the network has led to the development of very high-speed routers consisting of several specialized hardware components for sophisticated packet processing.

A fundamental operation performed in the modern routers and the advanced networking devices is *searching*. In the context of packet processing, searching is the process of checking to see if network packets contain the information of interest. A simple example is the address lookup for packet forwarding. Given a routing table consisting of several addresses, the router searches the table for the destination address of each packet. Once this address is found, the packet can be forwarded to the next hop associated with this destination. Another example is searching for predefined keywords in the packet payload. The occurrence of such keywords in the payload can allow the router to give a special treatment to the packet.

Search operations are performed by key components in the data path of routers and their performance directly affects the packet forwarding speed. Slow search speeds can create performance bottlenecks and degrade the router throughput. Therefore, sophisticated and high-speed techniques are required to design these components.

The focus of this dissertation is developing high-speed network search techniques. Specifically, we address three important search problems: the longest prefix matching for Internet Protocol (IP) route lookup, packet classification, and multi-pattern matching for deep packet inspection. We propose a new and generic search technique that uniquely combines some architectural and algorithmic techniques. We demonstrate how our proposed solution is superior to some of the existing solutions for the same problems.

### **1.1** Searching in the Context of Networks

In this chapter, we introduce network search operations and discuss the commonly employed techniques. We highlight their inadequacies and introduce our new approach.

**Longest Prefix Matching (LPM):** In LPM, we wish to search the longest matching prefix of an input key in a table consisting of a large number of prefixes. This is a fundamental process performed in the IP address lookup and forwarding.

The Internet consists of millions of networked computers. The data packets are routed from one host to another using IP. A host is connected to the Internet through an *interface* that has been assigned an IP address. For the Internet Protocol version 4 (IPv4), the addresses are 32 bits wide and allow a capacity of  $2^{32}$  interfaces. Before 1993, the IP addresses were allocated to organizations in chunks of  $2^8 = 256$  (Class C network),  $2^{16} = 65,536$  (Class B network), and  $2^{24} = 16,777,216$  (Class A network). This could be accomplished by assigning the most specific 24 bits, 16 bits, and 8 bits of an IP address to Class C, B, and A networks respectively. For instance, the IP address 128.252.153.00/24 specifies a network of 256 or fewer interfaces, each having an address with the first 24 bits being 100000001111110010011001, the binary representation of 128.252.153. However, such an assignment became problematic. If an organization wanted to support a network with interfaces significantly more than 256 but significantly less than 65,634, it would still be allocated space for 65,634 addresses which would result in an overallocation. This would cause a rapid shortage of IP addresses. Therefore, to prolong the life of IPv4 addresses, Classless Interdomain Routing (CIDR) was adopted by the Internet Engineering Task Force (IETF). With CIDR, the classes were abolished. Today, the network addresses can be allocated as a.b.c.d/p where /p indicates how many bits of the address prefix should be considered for the network. Since p can be any arbitrary number of prefix bits between 0 to 32, the assignment is more flexible. For instance, if an organization wants an address space worth 3,000 interfaces, then an address a.b.c.d/20 can be assigned to the network which allows up to 4096 interfaces and reduces overallocation. All of these interfaces will share the same 20 prefix bits.

To route a packet from one interface to another, the router responsible for the network containing the source host sends the packet to the router handling the destination network. Each router maintains a routing table consisting of thousands of network addresses, each specified in *address/prefix* form, and the associated next hop information. To send the packet to the correct network, the router searches the table for the longest matching prefix of the destination address in the packet. When one is found, the packet is forwarded to the associated next hop. The more matching prefix bits, the more specific the network address. It is possible that a packet matches two prefixes, one shorter than the other. The networks specified by these two prefixes can be handled by completely different routers and service providers. In order to resolve the next hop, the router looks for the most specific network address by matching the longest prefix. Address lookup with LPM needs to be performed for each incoming packet. The speed of address lookup directly impacts the forwarding rate of the router. Hence, high-speed solutions for address lookup are important. Comparing the destination address with all prefix entries in the routing table, one-by-one, is impractical when the table consists of several thousand prefixes. Sophisticated algorithmic techniques are required. LPM is a well researched problems in computer networking. The need of an efficient LPM algorithm is even more pronounced for IPv6 where the IP address is 128 bits long, four times that of an IPv4 address. A long IP address implies longer prefixes and a larger set of possible prefix lengths, both of which lead to increased complexity.

Conceptually, an *l*-bit prefix of a *W*-bit address defines a region of  $2^{W-l}$  contiguous addresses in the space of  $2^W$  addresses. We wish to search the smallest region in which a given destination address falls.

**Packet Classification:** While the IP route lookup operates on just a single field of the packet header, a more sophisticated search in which a key is specified over all the header fields, is required for applications such as firewalls. A firewall has predefined policies to control the flow of data in and out of the protected network. Consider the following rule.

$\label{eq:sigma} \begin{array}{l} \text{if SIP} \in [a{:}b] \ \& \ DIP \in [c{:}d] \ \& \ SP \in [e{:}f] \ \& \ DP \in [g{:}h] \ \& \ Protocol = X \\ \text{then Action} = drop \end{array}$

This rule states that a packet should be dropped when the source IP address (SIP) falls in the range a to b, the destination IP address (DIP) in the range c to d, the source port (SP) in the range e to f, the destination port (DP) in the range g to h, and the protocol field is exactly X. In general, there can be any number of header fields involved in the rule specification and the associated actions can be different. This rule specification is based on five fields and is useful in several applications. The classification based on such rules is commonly known as 5-tuple packet classification. Note that if the range of the values specified is a single value (e.g. a = b), then it is essentially an exact match for that field. More flexible rule specifications are also possible. Consider the following rule.

if SIP  $\in S_1$  & DIP  $\in S_2$  & SP  $\in S_3$  & DP  $\in S_4$  & Protocol  $\in S_5$ then Action = drop

In this case, instead of defining ranges of values, a set of distinct values is specified. Thus, if SIP belongs to a set of predefined addresses,  $S_1$ , DIP belongs to  $S_2$  and so on, then the rule matches and the action is executed. Such a rule can be converted into a form of the first type of rule by simply creating a separate rule for each value contained in  $S_1$ ,  $S_2$ , and so on. In this way, a single rule can expand into several rules, each pointing to the same original rule. Given a set of several thousand 5-tuple rules, the process of packet classification returns a set of matching rules for each arriving packet. From one perspective, this process can be viewed as a key searching process. A 5-tuple of the packet header is essentially a 104-bit key (32 bits of each address, 16 bits of each port, and 8 bits of protocol). This key can take any value in the space of  $2^{104}$ . Each rule defines a region within this space. We wish to find if the given key (header of a packet) belongs to any region defined by the rules.

**Pattern matching for deep packet inspection:** With the growth of network security threats, network operators have started to control the flow of data depending on the packet content. Therefore, firewall policies which operate on just the packet header are no longer sufficient. Tighter policies that look deeper in the packet payload to decide if the data is safe are required. This gives rise to another class of searching processes: searching for a set of predefined keywords or patterns in the streaming network data. These keywords or patterns can be signature strings for detecting SPAM, Internet worms, and viruses. This problem, commonly known as multi-pattern matching, has several applications beyond network security. For example, in content-based routing, a packet is routed to the appropriate destination based on the payload which requires detection of predefined payload signatures. Copyright protection is another example in which deep packet inspection is required to protect copyrighted or sensitive data from being transferred over the network illegally.

The patterns can be more expressive than just simple strings. Consider a regular expression " $abc^+d?e$ " which matches all the keys with the first three characters "abc," followed by zero or more occurrences of 'c,' followed by character 'd,' followed by any single character followed by 'e'. Unlike LPM or packet classification, the number of *keys* represented by this expression is infinite since there is no limit on the number of times 'c' occurs after "abc". Hence, searching such keys (regular expressions) would require more sophisticated algorithmic techniques.

In summary, the network search problem deals with searching a set of predefined keys in network data that includes packet headers and payload. Most of these applications are in-line components in the data path. Therefore, the search speed directly affects the network speed and emphasizes the need for developing high-speed search techniques. For such applications, scalability of the search table is another important issue. Increasing network speeds and data traffic, growing size of the routing tables, larger firewall rule sets, and larger pattern sets, all demand scalable search techniques. Some commonly used techniques are described below.

### **1.2** Common Search Techniques

One of the most naïve ways to look up a key is walking through all the keys present in the table and looking for a match. This becomes impractically slow for large tables. Another way is to use direct indexing. If the universe of keys is small, then a table can have an entry for each possible key within that universe so that the key to be searched can be used to index the table entry. However, this is often not the case. The universe of the keys is orders of magnitude larger than the size of the key set kept in the table. Therefore, direct indexing needs prohibitively large storage.

To search such a table, the keys need to be arranged in certain data structures and algorithmic techniques must be employed. Most of the literature on searching deals with efficient representation of keys in suitable data structures and an efficient algorithm to search this data structure for a given key. The two most important criteria to evaluate any such algorithm are the memory requirement to maintain the data structure and the time required to execute a search algorithm on a key.

Among the most common techniques for such table lookups is the use of set-associative memory. In order to look up a key in a set-associative memory, the key is split into two parts, *index* and *tag*. The index is used to select a block of fixed number of contiguous memory locations. Each memory location contains a tag and associated data. The tag of the search key is compared with the tags of all the memory locations within the selected block. If a tag matches, then it indicates a complete match for the key and the associated data can be used. If the number of memory locations within a block is n, then this memory is called n-way set-associative. If n is as large as the memory size, then it is called fully-associative memory, in which case the entire key acts as a tag and there is no index. The fully-associative memory is also known as Content Addressable Memory (CAM).

A fundamental characteristic of a set-associative memory is that it does not guarantee that a specific key will always be placed in one of the memory locations. When the index part of a key to be inserted selects a completely filled block of memory locations, then the key can not be inserted without replacing a key already present in the block. While other blocks might have empty locations, the key can not be placed in them for the sake of correctness of the search. To guarantee that a given set of keys will always be placed in a given sized set-associative memory, it must be made fully-associative. Therefore, CAM is one of the most popular choices for implementing table lookup.

The main problem with CAM, however, is the excessive power consumption from large parallel comparisons. A given search key must be compared with each memory location and that consumes a significant amount of power. The power consumption gives rise to additional problems such as requirement of power dissipation mechanisms and extra space on the circuit board to accommodate them. To develop compact devices, either power reduction methods for CAM or alternative algorithmic approaches for table searching are needed. While progress is being made on both fronts by the research community and the industry, this dissertation focuses on the algorithmic techniques for table searches.

Some of the most commonly used algorithmic techniques are based on *decision trees*. In a decision tree, a search starts from the root of the tree and progresses hierarchically towards the leaves. At each level of hierarchy, the scope of the search is narrowed. After traversing the tree, if the key is not found, then it is absent from the set. Several decision tree data structures exist. B-trees, Red-Black trees, binary search trees, interval trees, and radix trees are examples [38]. Often, the tree data structure can be optimized for specific search problem. A radix tree, or *trie*, can be used for LPM. Triebased LPM techniques have been significantly improved upon in terms of memory and lookup time requirement [15, 18]. Decision-tree based packet classification algorithms have also been explored [21, 27]. The well-known Aho-Corasick automaton for multipattern matching is also similar to a decision tree algorithm [5].

Decision-tree based data structures and algorithms are natural choices for algorithmic searches. A decision tree involves multiple sequential dependent memory accesses since the next level of trie can be reached only after the node at the previous level has been read and a child node to follow has been determined. Such dependent memory accesses slow down the overall search. The speed can be improved by pipelining the accesses where each stage in the trie is busy processing a different search key. However, pipelining requires multiple memory chips. Moreover, it will also result in

A simple algorithmic alternative to CAM is a hash table. A hash table consumes an average O(n) space for n keys and an average O(1) memory accesses to search for an exact key. In a hash table, a given set of keys is mapped to the table entries using a hash function. Hash function h() takes the key, x, from the universe 1, 2, ..., U as input, computes the address of the key, h(x), between the range 0 to m-1, and inserts the key at this address. If two keys get mapped to the same location, they *collide.* One method to resolve collisions is chaining in which all the keys mapped to the same location are linked in a list. When a key is to be searched, the location of the key is calculated using the hash function and the linked list of keys mapped to this location is traversed sequentially to locate the input key. If n keys are to be stored in m memory locations, then a hash table requires an average of 1 + (n-1)/2mmemory accesses for a successful search and 1 + n/m accesses for an unsuccessful search [38]. With a sufficiently larger number of slots in the table than the number of keys (i.e. small n/m), the memory accesses for both successful and unsuccessful searches approach one. Therefore, a hash table is a memory efficient alternative to CAMs with an almost equally effective search time.

pipelines with several stages that can make the memory management difficult.

Although CAM and hash tables serve as effective solutions for searching *exact* keys, they are not suitable for searching tables with keys containing ranges and wild cards. Consider a universe of keys between 0 to 1023. Assume that a set of all the keys from 17 to 32 needs to be represented and put in a table. While each key in the range can be stored separately, it is impractical for large ranges. Clearly, a straightforward hash table application does not help until either the range is represented differently or the search key is used differently so that the searching boils down to exact searching. A variant of CAM known as Ternary CAM (TCAM), however, provides a simple solution to such searches. In a TCAM, a bit can take a value 0, 1, or don't care (denoted by \*). Each range can be represented as a set of prefixes. For instance, the range [17 : 32], which is [0000010001 : 0000100000] in binary, can be represented as a set of the following prefixes:

| 0000010001 | ≡        | [17]    |

|------------|----------|---------|

| 000001001* | $\equiv$ | [18:19] |

| 00000101** | ≡        | [20:23] |

| 0000011*** | ≡        | [24:31] |

| 0000100000 | ≡        | [32]    |

These prefixes can be stored in the TCAM. When the key 0000010110 is to be searched, it is compared with all keys, ignoring the \* bits. Since the key matches 00000101\*\*, the search is successful. Due to the ternary representation, the range key could be expressed with a small number of TCAM compatible keys. It is worth mentioning that the method presented here is not the only way to represent ranges in TCAM. There are more space-efficient ways that have been proposed recently [24].

While a TCAM provides a more sophisticated search technology, it suffers similar problems as CAM: high power consumption and high costs. The cost of a TCAM is higher than a CAM since each TCAM cell must implement a ternary comparison. Again, the research community has responded with two types of solutions to such complex search problems: ones that try to minimize the power consumption of TCAM and the others based on algorithmic techniques that use commodity memory chips. The algorithmic techniques are of particular interest because they cost less. So, the question arises: how can we devise algorithmic search techniques that match the performance of TCAM? To date, most of the algorithms have not been able to match the performance and the generality of TCAM.

Developing algorithmic search techniques as versatile and efficient as TCAM is challenging. However, by taking advantage of particular application characteristics, such techniques or even more sophisticated ones can be developed. This thesis explores such techniques and shows how a limited TCAM-like functionality can be achieved for certain search applications using parallel and embedded memory blocks on a chip in combination with commodity memory chips. Particularly, we first explore ways to express the keys and queries in a form suitable for exact searches. Then we use the hash tables for executing these searches. Most importantly, we illustrate a technique based on Bloom filters to suppress unnecessary or potentially unsuccessful exact searches in the hash table and speed up the overall searching process.

### 1.3 Thesis Organization

In the next chapter, we review the related work on Bloom filters since it is central to our algorithms. A Bloom filter is a randomized data structure which uses hashing to store a set of strings compactly but *approximately*. Several variants of Bloom filters and their applications have been proposed. We will review some of them.

In Chapter 3, we address the LPM problem. The existing solutions to the address lookup problem include both algorithmic (trie-based, hashing) and architectural (TCAM) solutions. We describe our Bloom filter based solution which is a mix of algorithmic and architectural techniques. We show how Bloom filters can be used effectively in combination with existing VLSI hardware technology to realize a LPM solution that outperforms the TCAM in terms of cost and speed.

In Chapter 4, we address the packet classification problem. We propose an approach that uses Bloom filters combined with a modified version of the Crossproducting algorithm [33]. The Crossproducting algorithm classifies a packet by performing single field lookups for each field and combining the results to get the best matching rule. It is fast but requires exorbitant memory space due to the extra rules introduced in the process of the crossproduct. We demonstrate a technique that modifies the algorithm and reduces the memory overhead by splitting the rule set into smaller subsets. More importantly, we show how we can preserve the speed of the original algorithm by reducing unnecessary memory accesses using Bloom filters.

In Chapter 5, we introduce a simple algorithm for multi-pattern matching. Like LPM, multi-pattern matching is a well researched problem with a family of algorithmic solutions. However, the existing solutions are inadequate to execute this task at very high speeds and tend to create a bottleneck. We leverage the hardware-based Bloom filters to perform multi-pattern matching at multi-gigabit per second rates.

While the algorithm introduced in Chapter 5 can process packets at line speed, it is only efficient for short strings (less than 16 characters). In Chapter 6, we extend this algorithm to handle strings of arbitrary lengths at the cost of more memory. The resulting solution is an enhancement of the classic Aho-Corasick algorithm for multipattern matching. Our solution takes advantage of the parallelism provided by the hardware and the efficiency of Bloom filters to accelerate the Aho-Corasick algorithm by a constant factor dependent on the amount of available memory resources.

Chapter 7 summarizes our contributions.

# Chapter 2

# **Bloom Filters and Variants**

A Bloom filter is a data structure used to represent a set of items compactly and approximately. It is based on the concept of multiple hashing. Formulated by Burton H. Bloom in 1970 [8], it has found several applications including in the area of databases and computer networks [9].

In this chapter, the theory behind basic Bloom filters and their variants is reviewed.

### 2.1 Bloom Filters

A Bloom filter is essentially a bit-vector (which we call *Vector*) of length m used to efficiently represent a set of bit-strings. Given a set of bit-strings, S, with n members, a Bloom filter is "programmed" as follows. For each bit-string, x, in S, k hash functions,  $h_1()...h_k()$ , are computed on x producing k values each ranging from 1 to m. Each of these values addresses a single bit in the m-bit vector, hence each bit-string xcauses k bits in the m-bit vector to be set to 1. Note that if one of the k hash values addresses a bit that is already set to 1, then that bit is not changed. The following pseudo-code describes adding a bit-string, x, to a Bloom filter.

**BFAdd** (x) 1. for (i=1 to k)2. Vector $[h_i(x)] \leftarrow 1$

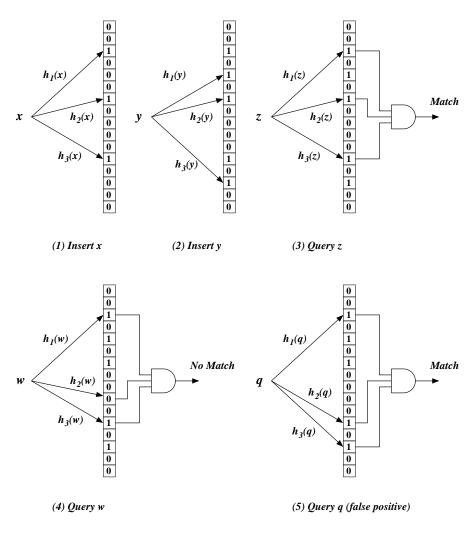

Figure 2.1: Illustration of a Bloom filter

Figure 2.1(1) and (2) illustrate Bloom filter programming. Two bit-strings, x and y are programmed in the Bloom filter with k = 3 hash functions and m = 16 bits in the array. Note that different strings can have overlapping bit patterns.

Querying the filter for set membership of a given bit-string, x, is similar to the programming process. Given bit-string x, k hash values are generated using the same hash functions used to program the filter. The bits in the *m*-bit vector at the locations corresponding to the k hash values are checked. If at least one of the k bits is 0, then the bit-string is declared to be a non-member of the set (Figure 2.1(4)). If all the bits are found to be 1, then the bit-string is said to belong to the set with a certain probability (Figure 2.1(3)). If all the k bits are found to be set and x is not a member of S, then it is said to be a false positive. The following pseudo-code describes the query process:

#### **BFQuery** (x)

- 1. for (i=1 to k)

- 2. if  $(\operatorname{Vector}[h_i(x)]=0)$  return false

- 3. return true

The ambiguity in membership comes from the fact that the k bits in the m-bit vector can be set by any of the n members of S. For instance, in Figure 2.1(5), q maps to all the bits which were set by x and y. Although  $q \notin S$ , the filter shows a match. Thus, finding a bit set does not necessarily imply that it was set by the particular bit-string being queried. However, finding a 0 bit certainly implies that the bit-string does not belong to the set; if it were a member, then all k-bits would have been set when the Bloom filter was programmed.

#### 2.1.1 False Positive Probability

Now we look at the step-by-step derivation of the false positive probability i.e., the probability of finding all the k lookup bits set for a bit-string that is not programmed. The probability that a random bit of the m-bit vector is set to 1 by a hash function is simply  $\frac{1}{m}$ . The probability that it is not set is  $1 - \frac{1}{m}$ . The probability that it is not set by any of the n members of X is  $(1 - \frac{1}{m})^n$ . Since each of the bit-strings sets k bits in the vector, the probability becomes  $(1 - \frac{1}{m})^{nk}$ . The probability that this bit is 1 becomes  $1 - (1 - \frac{1}{m})^{nk}$ . For a bit-string to be detected as a possible member of the set, all k bit locations generated by the hash functions need to be 1. The probability that this happens, f, is given by

$$f = \left(1 - \left(1 - \frac{1}{m}\right)^{nk}\right)^k \tag{2.1}$$

For the large values of m the previous equation reduces to

$$f \approx \left(1 - e^{\frac{-nk}{m}}\right)^k \tag{2.2}$$

This probability is independent of the input bit-string and is termed the *false positive* probability. The false positive probability can be reduced by choosing appropriate values for m and k for a given size of the member set, n. It is clear that the size of the bit-vector, m, needs to be much larger than the size of the bit-string set, n. For the given ratio  $\frac{m}{n}$ , the false positive probability can be reduced by increasing the number of hash functions, k. In the optimal case, when false positive probability is minimized with respect to k, we get the following relationship

$$k = \frac{m}{n}\ln 2 \tag{2.3}$$

The false positive probability at this optimal point is given by

$$f = \left(\frac{1}{2}\right)^k \tag{2.4}$$

It should be noted that if the false positive probability is to be fixed, then the size of the filter, m, needs to scale linearly with the size of the bit-string set, n. In the optimally configured Bloom filter, the probability of finding a bit set is 0.5.

### 2.2 Counting Bloom Filters

Deleting a bit-string stored in the filter is impossible without introducing false negatives. Deleting a particular entry requires the corresponding k hashed bits in the bit vector be set to 0 which could disturb other bit-strings programmed into the filter that hash to any of these bits. In order to solve this problem, *Counting Bloom Filters* were proposed in [20]. A counting Bloom Filter maintains a vector of counters (which we call *Counter*) instead of a bit-vector. Whenever a bit-string is added to or deleted from the filter, the counters corresponding to the k hash values are incremented or decremented, respectively.

Figure 2.2: Illustration of an Extended Bloom filter

As will be clear later, we use a composite data structure consisting of a counting Bloom filter and a regular Bloom filter to support incremental updates to the database of items stored in Bloom filters.

### 2.3 Extended Bloom Filters

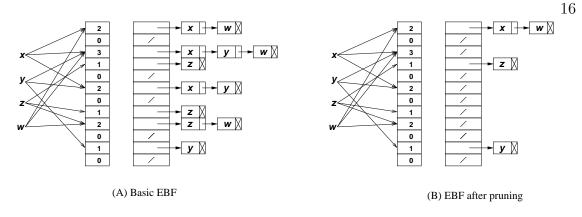

Extended Bloom Filters (EBF) were introduced by Song et. al. in [29]. An EBF is essentially a Counting Bloom filter coupled with a hash table. This combination enables not only a quick check for a query item in the set but also helps us retrieve the item and its associated information from the hash table. While some of the algorithms introduced in this work have a similar architectural flavor, there is a clear architectural separation between a Bloom filter and a hash table in our algorithms. An EBF on the other hand tightly couples the counting Bloom filter with the hash table. A one-to-one correspondence exists between the m counters of the counting Bloom filter and the m buckets of a hash table.

Song et. al. presented different flavors of the EBF. Only the basic EBF architecture is discussed here. An EBF works as follows. It maintains a counting Bloom filter with m counters and as many buckets in a hash table. An item is first inserted in the counting Bloom filter with the k hash functions and the same item is put in the k corresponding buckets of the hash table. This is illustrated in Figure 2.3(A). Items x, y, z, and w are inserted in the data structure. Each item is replicated in k different places. The counter essentially indicates the number of items stored in the corresponding bucket. When an item is searched, the counting Bloom filter is queried. If the item is present in the Bloom filter, then the **bucket with the smallest counter is searched**. For instance, if y is to be searched, it will be searched in bucket 11 which has a count of 1 (and only one item in the corresponding bucket). A tie can be broken by choosing the least loaded bucket with the smallest index. The Bloom filter then serves a dual purpose: eliminating the unsuccessful searches and when a query is successful, pointing to the least loaded bucket to enable a quicker search. The authors argue that optimal parameters almost always cause an item to hash to a bucket where no other item is stored and a counter with a value of 1 can be found with a very high probability. If the counting Bloom filter is maintained in a fast *on-chip* memory and the hash table is kept in the slower but bigger *off-chip* memory, then unnecessary and expensive off-chip memory accesses can be avoided by first querying the Bloom filter.

Several optimizations to the basic EBF data structure were presented. Although there can be k copies of an item, only the copy in the least loaded bucket is searched. Hence, all the other copies of the item can be removed resulting in a pruned data structure where there is just one copy of each item. While removing the items, the counters are left unchanged to avoid incorrect searches. A pruned data structure is shown in Figure 2.3(B). Pruning makes incremental insertions and deletions more difficult. Incremental update-friendly algorithms that also maintain the same performance as a pruned EBF were presented in [29].

### 2.4 Spectral Bloom Filters

Cohen et. al. proposed Spectral Bloom Filters (SBF) to detect items having multiplicities greater than a particular threshold [13]. An SBF is essentially a CBF. Counters corresponding to an item are incremented each time the item is stored in a SBF. The main concept is that the number of times an item is stored can not exceed the smallest counter it hashes to. Thus, the smallest counter value selected by the hash functions is an estimate of the multiplicity of the item. The same idea was proposed by Estan et. al. independently to count the number of packets belonging to a TCP flow approximately [19]. Both Cohen and Estan proposed the optimization of *conservative updates*. Essentially, since the minimum among all the selected counters represents the multiplicity of an item, the other counters don't need to be incremented until the minimum counter catches up. For instance, let an item, x, map to counters  $\{12, 17, 23\}$  having values  $C_{12} = 4$ ,  $C_{17} = 5$ , and  $C_{23} = 2$ . When the next instance of x is stored to the filter, instead of incrementing all the counters only  $C_{23}$  needs to be incremented. When the minimum counter catches up with other counters (when  $C_{23} = C_{12} = 4$ ) then any next addition of x will increment both since both are now minimum counters until some other item hashing to one of these counters changes the value. When these two counters catch up to  $C_{17}$ , then all will be incremented. With this heuristic of minimal increase, the number of updates needed per item is reduced significantly. A drawback of the minimal increase heuristic is that an incremental deletion of items from the filter can introduce false negatives.

There are two false positives associated with the SBF data structure. The first is the regular false positive probability of the Bloom filters where an item, although not present in the filter, shows a match since all the counters it maps to are greater than 0. The second happens when the multiplicity of an item is overestimated, i.e. the multiplicity of item x is actually  $f_x$  but the filter's minimum counter corresponding to x shows it to be  $f'_x > f_x$ . Both false positive probabilities have the same value as Equation 2.2.

### 2.5 Bloomier Filters

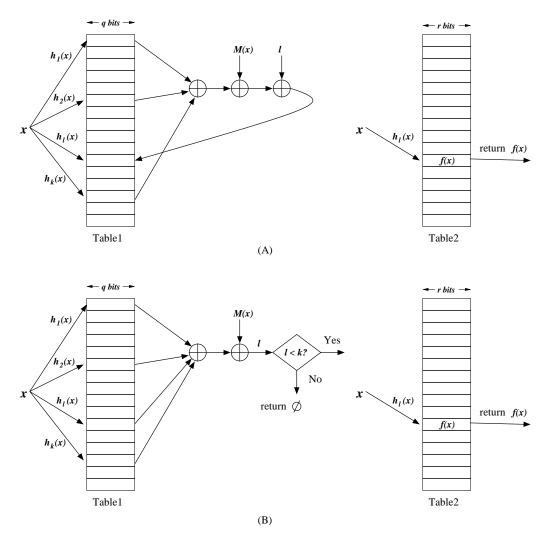

Chazelle et. al. proposed a *Bloomier* filter which can encode arbitrary functions on a small subset of items from a large universe [10]. Formally, let f be the function that maps a finite arbitrary set of items, S, chosen from the domain  $D = \{0, 1, 2, ..., N-1\}$ . Let  $R = \{\phi, 1, 2, ..., 2^r - 1\}$  be the range of this function so that f(x) is  $\phi$  for all  $x \in D \setminus S$ . Given an x, a Bloomier filter can produce f(x) correctly for all  $x \in S$  and almost correctly (with some small error probability) for all  $x \in D$ S. A limitation, however, is that S needs to be static.

Figure 2.3: Illustration of Bloomier filter

Let  $x \in D$  and let  $N(x) = \{h_1(x), h_2(x), ..., h_k(x)\}$  be the set of hash values calculated on x by the k hash functions. N(x) is called the neighborhood of x. Given set S, let  $\Pi$  denote a permutation on S. Let  $x >_{\Pi} y$  denote y precedes x in  $\Pi$ . The hash functions  $h_i$  need to satisfy the following property: for any x and y having  $x >_{\Pi} y$ , there should be at least one  $h_i$  so that  $h_i(x) \notin N(y)$ . If there are multiple such hash function indices i, then the the smallest index is chosen. Let l(x) denote that index and L(x) denote the corresponding hash value for x,  $h_{l(x)}(x)$ . It follows that for any  $x \neq y$  and  $x, y \in S$ ,  $L(x) \neq L(y)$ . In other words, there are unique locations in the array of m locations corresponding to each of the items in S. The insertion and query operation of a Bloomier filter are illustrated in Figure 2.3. The *mutable* form of a Bloomier filter contains two tables:  $Table_1$  in which each entry is q bits wide and  $Table_2$  in which each entry is r bits wide.  $Table_2$  contains the actual value associated with an item in S. The values in  $Table_2$  can be changed, however, the set S can not be changed dynamically. Items are inserted in the order specified by  $\Pi$  described before. To insert an item, x, all the values at the hashed locations of  $Table_1$  corresponding to x except the one at the unique location, L(x), are read and XORed. Then, this result is XORed with a random q-bit value, M(x), specific to x. Finally, this result is XORed with l(x) and the final result is kept in the location L(x). Note that the final result is essentially an encoding of l(x). The actual value associated with x, f(x), is kept in  $Table_2$  at L(x). Thus,

$$Table_1[L(x)] = M(x) \oplus l(x) \left( \bigoplus_{\substack{i=1\dots k\\i \neq l(x)}} Table_1[h_i(x)] \right)$$

$$Table_2[L(x)] = f(x)$$

(2.5)

Note that writing a value at L(x) does not disturb any values already written for any y that precedes x in the permutation because  $L(x) \notin N(y)$  for all such y. Hence, this value would never contribute to the values set for earlier items.

When the item is to be looked up, all the values kept in the hash locations of  $Table_1$  corresponding to the query item are XORed. The result is then XORed with M(x). If the item was stored, then the final result should be a decoded l(x).

$$result = \left(\bigoplus_{\substack{i=1\dots k}} Table_1[h_i(x)]\right) \oplus M(x)$$

$$= \left(\bigoplus_{\substack{i=1\dots k\\i \neq l(x)}} Table_1[h_i(x)]\right) \oplus Table_1[L(x)] \oplus M(x)$$

$$= \left(\bigoplus_{\substack{i=1\dots k\\i\neq l(x)}} Table_1[h_i(x)]\right) \oplus M(x) \oplus l(x) \left(\bigoplus_{\substack{i=1\dots k\\i\neq l(x)}} Table_1[h_i(x)] \oplus M(x)\right)$$

$$= l(x)$$

(2.6)

If the item is not in the table, then with a very high probability the result will be a q-bit random number since M(x) is a q-bit random number which randomizes the entire result after XORing. In the true positive case, it gets cancelled. We know that each l(x) for all x is a number between 1 and k. If the result of the lookup is > k, then it is clearly a mismatch. Therefore, if  $x \notin S$  and  $l(x) \leq k$ , then we have a false positive. The probability of this false positive is simply  $\frac{k}{2q}$ . Thus, choosing a larger q, the probability can be made very small. Once l(x) is obtained, we simply look up  $Table_2$  to retrieve the associated value,  $Table_2[L(x)]$  (remember that  $h_{l(x)}(x) = L(x)$ ).

The challenge in constructing a Bloomier filter is to find the permutation  $\Pi$  and the hash functions  $h_i()$  which satisfy the required properties. Challez et. al. give a greedy algorithm for the same and analyze its complexity.

## 2.6 Compressed Bloom Filters

A compressed Bloom filter was proposed by Mitzenmachar [25]. If a Bloom filter is used to encode a set of items and transmitted over the network to another entity, then reducing the size of the transmitted data is useful. A compressed Bloom filter is designed with this motivation. Given a set of n items and a size of z bits *after* compression, what is the best way to choose m, the original size of the Bloom filter and k, the number of hash functions, to minimize the false positive probability f? Moreover, z must respect the information theoretic bounds  $z \ge mH(p)$  where H(p)is the entropy function and p is the probability of a bit being set in the filter.

A traditional Bloom filter with optimal parameters gives the worst compression since it has maximum entropy. On the other hand, a filter with a large m and just one hash function can give a significant compression as well as a very small false positive probability. However, we can not have a very large m because the uncompressed form of the filter needs to be practical. Therefore, a compressed Bloom filter needs to be designed with some practical limitations on m. Theoretical analysis and examples are given in [25]. An example indicates that if the original Bloom filter bits per item, m/n, is 92, and the number of hash functions is k = 1, then this filter can be compressed to z/n = 8 bits per item. This filter shows a false positive probability of 0.0108 in its original form.

# Chapter 3

# Longest Prefix Matching

## 3.1 Introduction

In the Longest Prefix Matching (LPM) problem, we are given an input key I with length W bits and a table that contains keys with variable lengths from 1 to W. We are required to find the longest matching prefix of I in the table. LPM has received significant attention in the networking community due to its important role in routing packets in the Internet. A router maintains a table of Internet Protocol (IP) address prefixes. Each of these prefixes represents a set of IP addresses sharing the same prefix. Therefore, each prefix represents a sub network in the Internet. When an IP packet arrives, a router searches for the longest matching prefix of the destination address of the packet. When such a prefix is found, the router forwards the packet to the next hop associated with this prefix. The rate at which a router can forward packets directly depends on how fast it can perform LPM. Hence, efficient lookup techniques are important for high-speed packet processing.

Several LPM algorithms have been developed by the research community. A naïve way to perform LPM is by constructing a radix trie with the given set of prefixes and traversing it with the help of the IP address bits in a packet. This simple algorithm is slow because it can require W memory accesses in the worst case. Several improvements to this naïve data structure have been proposed. We will review the prominent algorithmic techniques in the next section.

## 3.2 Related Work

The Lulea scheme [15] first converts the trie into a *complete* prefix trie so that each node has either two children or no children. This is achieved with a technique known as *leaf pushing* in which the information associated with a node is pushed to the children of that node. The resulting trie is *expanded* with stride lengths of 16, 8, and 8. The expanded trie is represented using three levels of data structures containing bitmaps which can be indexed using the first 16 bits, next 8 bits and the last 8 bits of an IP address prefix. At each level, a set bit indicates that the search either terminates there in which case the next hop information is retrieved. If the bit is not set then the search terminates there and the next hop associated with the nearest ancestor of the current node is used to forward the packet. The authors use several techniques for reducing the memory requirement. This algorithm, although faster than the basic radix tree, does not match the performance of TCAM. It is primarily geared towards a software implementation. The incremental updates to the prefix set are difficult due to the trie expansion involved in the algorithm.

Waldvogel et. al. introduced a technique based on hash tables that performs a binary search on prefix lengths [40]. Assume that the prefixes of length i are kept in hash table i. For IPv4, we would have 32 hash tables in the worst case. Given the range of prefix lengths, the algorithm looks up the hash table of the middle prefix length (Hash table 16 for IPv4) with the corresponding number of IP prefix bits. If the match is found, the binary search continues in the hash tables on the right half, otherwise, it continues in the left half. Thus, if a match is found in hash table 16, then hash table 24 is probed with 24 prefix bits. Otherwise, hash table 8 is probed with 8 prefix bits. However, this scheme won't work without modification to the prefix set. For instance, let's assume that the longest matching prefix of an IP address is 9-bits long, 100110100<sup>\*</sup>. When the search is conducted on the left half of the prefix lengths, the hash table 8 would be looked up. To get the match for our 9-bit prefix, we must get a match for the 8-bit prefix so that the search is guided to the hash tables between 8 and 15. If there is no prefix  $10011010^*$  in hash table 8, then it will be a mismatch and the result will be incorrect. Hence, a prefix  $10011010^*$ , called *marker*, is artificially added to the hash table 8 in order to preserve the correctness. By adding markers to the hash tables whenever necessary, the correct longest matching can always be found. Binary search on prefix length requires  $\log_2 W$  hash table accesses in the worst case which is 5 for IPv4 and 7 for IPv6. Although attractive from the worst case performance perspective, this scheme makes the incremental updates to the data structure difficult due to the requirement of markers. The average performance does not match the performance of a TCAM.

Srinivasan et. al. introduced another technique called Controlled Prefix Expansion which is similar to the Lulea scheme [32]. All the prefixes are converted into a set of fixed length prefixes by expanding a shorter prefix to multiple longer prefixes of a predetermined length. Consider a 2-bit prefix 10\* which can be expanded to a set of 4-bit prefixes 1000\*, 1001\*, 1010\*, 1011\*. Specific prefix lengths can be picked and any prefix with shorter length can be expanded to multiple prefixes of the next predetermined longer length. The authors give an algorithm to pick the most optimal prefix lengths to expand the prefix sets. After the expansion, various LPM algorithms can be used. The authors illustrate how a multi-bit trie can be used, similar to the one used in Lulea. Binary search on prefix length algorithm can also be used. Due to the reduction in the distinct prefix lengths, the search speed improves.

Using a multi-bit trie, multiple bits of an IP address can be matched at a time. Each node in a multi-bit trie represents a set of nodes in the radix trie. The tree bitmap technique proposed by Eatherton et. al. uses a compressed representation of multi-bit trie [18]. A radix trie of depth i has  $2^{i}-1$  nodes and  $2^{i}$  children. Eatherton's technique uses two bit maps to encode the  $2^{i} - 1$  nodes of a radix trie in a single super-node: an "internal bitmap" that contains  $2^i - 1$  bits and an "external bitmap" containing  $2^i$ bits. A bit in the internal bitmap indicates if the corresponding node in the radix trie represents a valid prefix. A bit in the external bitmap indicates if the corresponding child exists. If a child exists then the search continues. All the children super-nodes of each super-node are arranged in consecutive memory slots and only the pointer to the first child is maintained. Using the knowledge from the external bitmap, the exact child super-node can be accessed by adding the corresponding offset in the base pointer. This technique saves a significant amount of memory but complicates the memory management and incremental updates. Overall, the compressed multi-bit trie is a fast and memory efficient technique but can not beat the performance of TCAM due to multiple dependent memory accesses for each lookup.

Figure 3.1: Basic configuration of Longest Prefix Matching using Bloom filters.

## 3.3 Our Approach

A hash table can be used to find the longest matching prefix of an IP address. We can construct a hash table from all the prefixes and with each prefix keep the associated next hop information. Given an IP address, we can test for the presence of each possible prefix in the hash table, starting from the longest. We stop when a matching prefix is found and the next hop information is retrieved. Constructing hash tables to minimize collisions with reasonable amounts of memory is well-studied. For our purpose, we assume that probing a hash table stored in an off-chip memory requires one memory access [40]. Therefore, this naïve approach would require W hash table lookups (and as many off-chip memory accesses) in the worst case, where W is the length of the IP address. However, we can reduce the memory accesses to almost a single access by using Bloom filters implemented in *on-chip* memory. The basic configuration of our system is shown in Figure 3.1.

We group prefixes according to length and define a Bloom filter for each set. We maintain W parallel Bloom filters in the embedded memory with each filter corresponding to a unique prefix length. There is no need to maintain a Bloom filter

corresponding to a prefix length for which there are no prefixes. Before querying a prefix in the hash table, we check to see if it is present in the corresponding Bloom filter. Only if the Bloom filter identifies a match do we proceed to query the hash table. A Bloom filter can produce a false positive match but never a false negative. If the match was a false positive, then it would be discovered after the hash table probe results in an unsuccessful search. In case of a false positive, we simply perform an extra memory access and proceed to check the next prefix showing a match in the corresponding Bloom filter<sup>1</sup>.