### Washington University in St. Louis

# Washington University Open Scholarship

McKelvey School of Engineering Theses & Dissertations

McKelvey School of Engineering

Summer 8-15-2021

# Provably and Practically Efficient Race Detection for Task-Parallel Code

Yifan Xu

Follow this and additional works at: https://openscholarship.wustl.edu/eng\_etds

#### **Recommended Citation**

Xu, Yifan, "Provably and Practically Efficient Race Detection for Task-Parallel Code" (2021). *McKelvey School of Engineering Theses & Dissertations*. 751.

https://openscholarship.wustl.edu/eng\_etds/751

This Dissertation is brought to you for free and open access by the McKelvey School of Engineering at Washington University Open Scholarship. It has been accepted for inclusion in McKelvey School of Engineering Theses & Dissertations by an authorized administrator of Washington University Open Scholarship. For more information, please contact digital@wumail.wustl.edu.

#### WASHINGTON UNIVERSITY IN ST.LOUIS

McKelvey School of Engineering

Department of Computer Science and Engineering

Dissertation Examination Committee:

I-Ting Angelina Lee, Chair

Kunal Agrawal

Sanjoy Baruah

Jeremy Buhler

Jeremy T. Fineman (Georgetown)

Provably and Practically Efficient Race Detection for Task-Parallel Code by Yifan Xu

A dissertation presented to The Graduate School of Washington University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> December 2021 St. Louis, Missouri

# Table of Contents

| List of | Table   | s                                                                  | V   |

|---------|---------|--------------------------------------------------------------------|-----|

| List of | Figur   | es                                                                 | vii |

| List of | Algor   | ithms                                                              | ix  |

| Ackno   | wledgr  | nents                                                              | X   |

| Abstra  | act     |                                                                    | xiv |

| Chapt   | er 1: I | ntroduction                                                        | 1   |

| 1.1     | Pitfall | l: Determinacy Race                                                | 2   |

| 1.2     | Limita  | ations of the Prior Studies                                        | 3   |

| 1.3     | Contr   | ibutions                                                           | 4   |

| 1.4     | Roadr   | nap                                                                | 6   |

| Chapt   | er 2: I | Preliminary                                                        | 7   |

| 2.1     | Task 1  | Parallelism                                                        | 7   |

| 2.2     | Mode    | ling Parallel Computations                                         | 8   |

| 2.3     | Work-   | Stealing Scheduler                                                 | 9   |

| 2.4     | Deter   | minacy Race Detection                                              | 10  |

| Chapt   | er 3: I | Race Detection for Pipeline Parallelism                            | 12  |

| 3.1     | 2D-O    | rder Algorithm                                                     | 14  |

|         | 3.1.1   | Notations and Definitions                                          | 14  |

|         | 3.1.2   | Reachability in 2D-Order Algorithm                                 | 15  |

|         | 3.1.3   | OM-DownFirst and OM-RightFirst Maintain Reachability Relationships | 17  |

|         | 3.1.4   | Checking Races and Updating Access History                         | 24  |

|         | 3.1.5   | Performance of 2D-Order                                            | 26  |

| 3.2    | Gener   | alizing 2D-Order                          | 27  |

|--------|---------|-------------------------------------------|-----|

| 3.3    | PRace   | er: Race Detection for Cilk-P             | 29  |

|        | 3.3.1   | Cilk-P's Support for Pipeline Parallelism | 29  |

|        | 3.3.2   | PRacer: Applying 2D-Order to Cilk-P       | 31  |

| 3.4    | Perfor  | mance Evaluation                          | 35  |

| Chapte | er 4: I | Futures and Proactive Work-Stealing       | 39  |

| 4.1    | Future  | e Parallelism                             | 42  |

|        | 4.1.1   | Modeling Future Parallelism               | 42  |

|        | 4.1.2   | Types of Futures                          | 44  |

| 4.2    | Proac   | tive Work-Stealing                        | 44  |

|        | 4.2.1   | Data Structures Used                      | 45  |

|        | 4.2.2   | The Algorithm                             | 47  |

| 4.3    | Perfor  | mance Bounds for Proactive Work-Stealing  | 50  |

|        | 4.3.1   | Bound on Execution Time                   | 52  |

|        | 4.3.2   | Bounds on Deviations                      | 54  |

| Chapte | er 5: I | Race Detection for General Futures        | 62  |

| 5.1    | Nearly  | y Series-Parallel Dag                     | 64  |

| 5.2    | Overv   | iew of F-Order                            | 64  |

|        | 5.2.1   | Access History in F-Order                 | 65  |

|        | 5.2.2   | Reachability Maintenance in F-Order       | 66  |

|        | 5.2.3   | An Illustrating Example                   | 68  |

| 5.3    | Detail  | s of F-Order and Its Correctness          | 70  |

|        | 5.3.1   | Construction of FOM Data Structures       | 71  |

|        | 5.3.2   | Reachability Queries Using FOM            | 78  |

| 5.4    | The P   | Performance Bound of F-Order              | 82  |

| 5.5    | Imple   | mentation and Empirical Analysis          | 85  |

| Chapte | er 6: I | Race Detection for Structured Futures     | 90  |

| 6.1    | Revisi  | ting Structured Futures                   | 91  |

| 6.2    | SF-Or   | der Algorithm                             | 94  |

|        | 621     | Intuition Behind the Ouery Algorithm      | 9.5 |

|     |                              | 6.2.2   | Reachability Queries in SF-Order                        | 97  |

|-----|------------------------------|---------|---------------------------------------------------------|-----|

|     |                              | 6.2.3   | Correctness Proof of the Query Algorithm                | 98  |

|     |                              | 6.2.4   | Maintaining the Reachability Data Structures On-the-fly | 105 |

|     |                              | 6.2.5   | The Access History Component                            | 105 |

| 6   | 5.3                          | Perform | mance Analysis of SF-Order                              | 107 |

| 6   | 6.4                          | Impler  | nentation and Empirical Evaluation of SF-Order          | 109 |

| Cha | $\operatorname{apt}\epsilon$ | er 7: C | Optimizing Access Histories                             | 115 |

| 7   | 7.1                          | Compi   | le-Time and Runtime Coalescing                          | 118 |

|     |                              | 7.1.1   | Compile-Time Coalescing                                 | 119 |

|     |                              | 7.1.2   | Runtime Coalescing                                      | 121 |

| 7   | 7.2                          | Interva | al-Based Access History                                 | 123 |

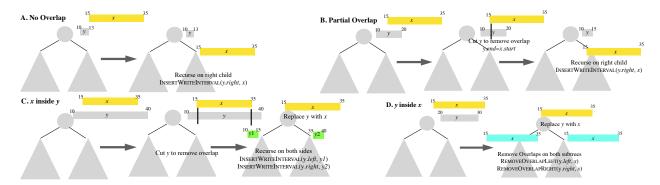

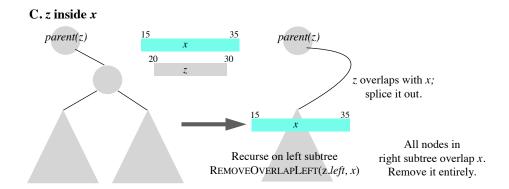

|     |                              | 7.2.1   | Updating the Write Tree                                 | 124 |

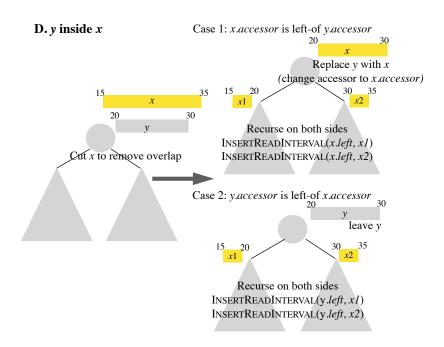

|     |                              | 7.2.2   | Inserting an Interval in the Read Tree                  | 128 |

|     |                              | 7.2.3   | Queries to Check for Races                              | 130 |

|     |                              | 7.2.4   | Performance Analysis                                    | 130 |

| 7   | 7.3                          | Empir   | ical Evaluation                                         | 133 |

| Cha | $\operatorname{apt}\epsilon$ | er 8: A | synchronous Access History                              | 140 |

| 8   | 3.1                          | Synchi  | onous vs. Asynchronous Access History                   | 142 |

| 8   | 3.2                          | The T   | race Data Structure                                     | 144 |

| 8   | 3.3                          | Asyncl  | hronous Race Detection Protocol                         | 146 |

| 8   | 3.4                          | Evalua  | tion                                                    | 150 |

| Cha | $\operatorname{apt}\epsilon$ | er 9: R | Related Work                                            | 153 |

| Cha | $\operatorname{apt}\epsilon$ | er 10:C | Conclusion                                              | 159 |

| Ref | ere                          | nces    |                                                         | 161 |

# List of Tables

| Table 3.1: | The execution characteristics of the benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2: | The execution times for the benchmarks running on one core for all configurations, shown in seconds. The numbers in parentheses indicate the overhead compared to the baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38  |

| Table 5.1: | The characteristics of the benchmarks. The sw and hw benchmarks have two implementations: structured (sf) and general futures (gf).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86  |

| Table 5.2: | Performance of the benchmarks with F-Order and FutureRD for race detection. Execution time on $P$ processors, $T_P$ , is given in seconds. Numbers in the parentheses show the overhead compared to the baseline. Numbers in the brackets show the scalability relative to $T_1$ of the same configuration. Measurements of smm running with FutureRD is not available because it segfaulted.                                                                                                                                                                                                                                                                                                                                                                       | 88  |

| Table 6.1: | The input size $(N)$ , basecase size $(B)$ , and execution characteristics of the benchmarks, including the total numbers of reads, writes, reachability queries performed throughout the execution, the number of futures used, and the number of nodes in the computation dag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 111 |

| Table 6.2: | Execution times of the benchmarks shown in seconds for the baseline executions (i.e., with no race detection, shown as $base$ ) and when running with MultiBags, F-Order, and SF-Order for race detection with two different configurations. The first configuration shown as $reach$ runs each algorithm with only the reachability construction overhead. The second configuration shown as full runs the full race detection algorithm. Columns with $T_1$ show the execution times running on one core, and columns $T_{20}$ show the execution times running on 20 cores. Numbers in the parentheses show the overhead compared to the baseline executions. Numbers in the brackets show the scalability relative to the $T_1$ time of the same configuration. | 112 |

| Table 6.3: | Memory usage of the benchmarks when running with F-Order and SF-Order for reachability maintenance, shown in gigabytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 113 |

| Table 7.1: | Overheads of a vanilla race detector. Time shown in seconds. The first four columns from left to right show the benchmark name, its running time without race detection, that with only the reachability component, and that with the full race detection. The numbers in parenthesis show the overhead comparing to the baseline. The last four columns show the number of memory locations and intervals accessed, on the order of millions.                                                                                                                                                             | 116 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 7.2: | Execution times (in seconds) and overheads of different versions of the race detector compared to the baseline (i.e., no race detection), whose values are shown in Table 7.1                                                                                                                                                                                                                                                                                                                                                                                                                              | 135 |

| Table 7.3: | Various execution statistics on memory accesses generated when running $vanilla$ , with comiler coalescing $(compiler)$ , and with both compiler and runtime coalescing $(both)$ . The $acc.$ and $int.$ indicate the number of accesses / intervals that eventually made into the access history, shown in millions. The $avg.$ shows the average size per interval accessed, and the $sum$ shows the total size (in Mbytes) accessed. The $(r)$ / $(w)$ indicate read or write.                                                                                                                          | 136 |

| Table 7.4: | The total time (in seconds) each benchmark spent updating its access history (i.e., hashmap for comp+rts and treap for treap)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 137 |

| Table 7.5: | Execution times of fft, mmul, and sort running on baseline (base, i.e., no race detection), comp+rts, and treap on different input sizes, with overhead compared to base shown in parenthesis. On the right of the execution times, we also show various stats for comp+rts (using a hashmap) and treap, where the $oh$ indicates time spent on access history only, the $ops$ indicates the number of hashmap / treap operations, the # $nodes$ shows the average number of nodes visited per treap operation, and the # $overlaps$ shows the average number of overlaps encountered per treap operation. | 138 |

| Table 8.1: | The total time (in seconds) each benchmark spent on performing runtime coalescing and uptating treap, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 141 |

| Table 8.2: | Execution times (in seconds) of different versions of the benchmarks. Columns with $T_1$ show the single-core execution times and columns with $T_{20}$ show the 20-cores execution times. Numbers in the parentheses show the overhead compared to the baseline. Numbers in the brackets show the scalability compared to its respective single-core execution $(T_1)$ .                                                                                                                                                                                                                                  | 151 |

# List of Figures

| Figure 1.1: | A simple task-parallel code that contains determinacy races                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1: | A simple fork-join code that computes the $n$ th Fibonacci number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8  |

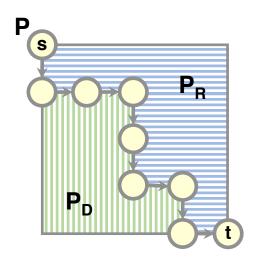

| Figure 3.1: | A path $P$ divides a 2D-dag into two regions, $P_R$ (shaded with horizontal lines) and $P_D$ (shaded in vertical lines)                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18 |

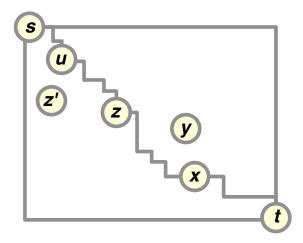

| Figure 3.2: | Figure for Lemma 9. Assume two lcas for $x$ and $y$ exist, namely $z$ and $z'$ , and let $u$ be a lca of $z$ and $z'$                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20 |

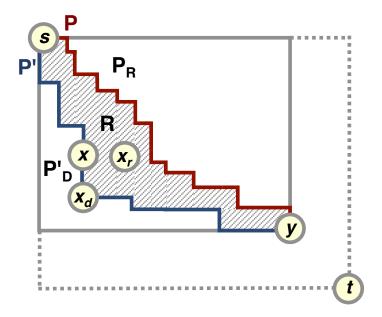

| Figure 3.3: | Figure for Lemma 10. Path $P$ is shown in red, and path $P'$ is in blue. The shaded region is $R$ . The node $x_d$ is $x.dchild$ and the node $x_r$ is $x.rchild$                                                                                                                                                                                                                                                                                                                                                                                                                       | 21 |

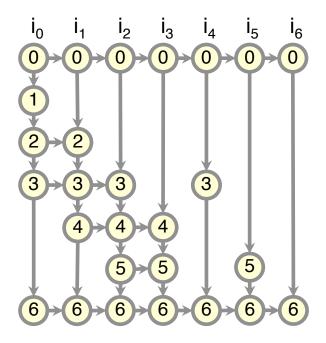

| Figure 3.4: | An example of the kind of 2D-dag Cilk-P can generate. A node presents a strand, and an edge denotes dependence between two strands. The iteration numbers are denoted above, and the numbers in the nodes denote the stage numbers.                                                                                                                                                                                                                                                                                                                                                     | 31 |

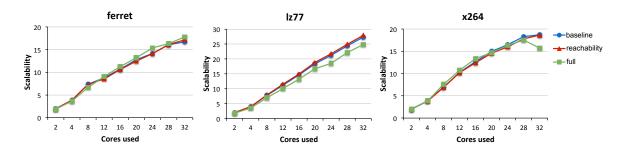

| Figure 3.5: | The scalability of the benchmarks. The x-axis shows the number of cores used. The y-axis shows the scalability, computed by taking the runtime on one core divided by the runtime on $P$ cores under the same configuration, where $P$ is the number cores used                                                                                                                                                                                                                                                                                                                         | 37 |

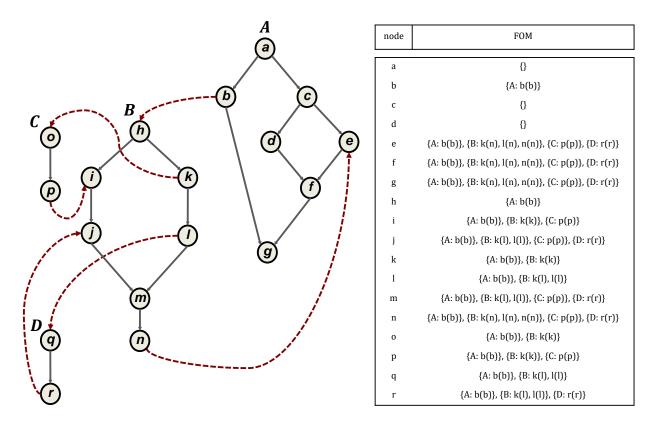

| Figure 5.1: | An example of a NSP-dag with every node's FOM data structure shown. In this NSP-dag, four SP-dags exist, ID'ed as $A, B, C$ , and $D$ , with $A$ being the main SP-dag and the others being the spawned future tasks. The non-SP edges are shown as thick dashed edges. Each node has its own instance of FOM data structure, containing entries of $\{key: value\}$ pairs, where the $key$ is the ID of an SP-dag and the corresponding $value$ is a set of non-SP ancestors from the SP-dag. The parentheses next to each non-SP ancestor shows its furthest descendant in the group. | 69 |

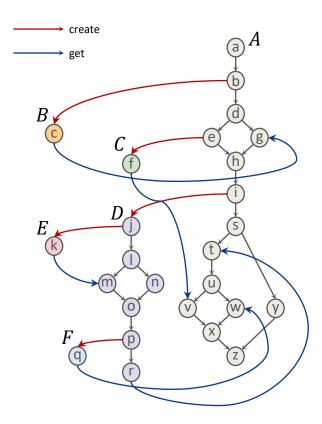

| Figure 6.1. | An example of an SF-dag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 93 |

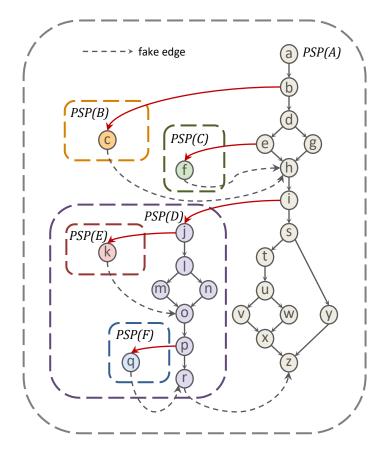

| Figure 6.2: | The corresponding pseudo-SP-dag for the SF-dag shown in Figure 6.1.                                                                         | 97  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 7.1: | All cases illustrating InsertWriteInterval $(y, x)$ — assumes and maintains the no-overlap invariant.                                       | 125 |

| Figure 7.2: | Case C of RemoveOverlapLeft( $z,x$ ). $x$ was inserted at an ancestor to the right of $z$ .                                                 | 127 |

| Figure 7.3: | Case D of InsertReadInterval $(y, x)$                                                                                                       | 128 |

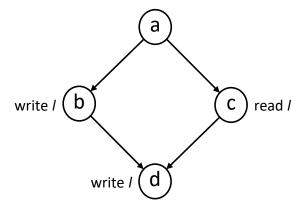

| Figure 8.1: | A parallel computation that contains a determinacy race. However, no race will be reported if we perform race detection in a certain order. | 143 |

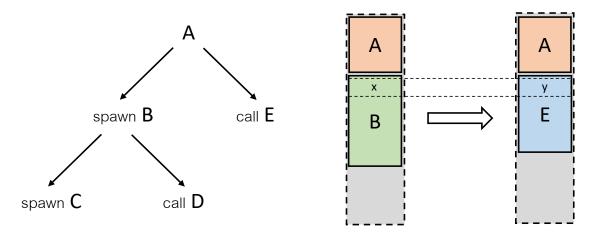

| Figure 8.2: | An invocation tree and its corresponding views of stack                                                                                     | 144 |

# List of Algorithms

| 1  | 2D-Order: Reachability Maintenance       |

|----|------------------------------------------|

| 2  | 2D-Order: Access Histories               |

| 3  | Variant 2D-Order                         |

| 4  | 2D-Order for Cilk-P                      |

| 5  | ProWS: The Main Scheduling Loop          |

| 6  | ProWS: The Steal Protocol                |

| 7  | F-Order: Construction                    |

| 8  | Helper Function: Group-Insert            |

| 9  | Helper Function: Group-Merge             |

| 10 | Group-Search in Reachability Query       |

| 11 | SF-Order: Reachability Query             |

| 12 | Base Case of matmul                      |

| 13 | Insertion-Sort Base Case of cilksort 123 |

| 14 | Trace Construction                       |

| 15 | Asynchronous Race Detection Protocol     |

# Acknowledgments

Every story has an ending, just as I am writing these acknowledgments to conclude my PhD life. Five years ago, I left my hometown, Shanghai, and began studying abroad for the first time in my life. Before I came to WashU, I had negligible research experience. I did not know if I could take care of myself without my parents' help. I did not know how to drive. There were a lot of things I needed to learn to survive my graduate study. Therefore, I was imagining a difficult and painful process of pursuing my PhD that I might not be able to stand. Every single moment from the past five years, however, had been proving that I was wrong. I published my first paper after the first year. I attended an academic conference for the first time and met interesting people. I have had a lot of such happy memories during my graduate study, and none of them would have been possible without the help of many people.

First and foremost, I would like to thank my advisor, Dr. Angelina Lee. Angelina is truly a wonderful advisor. Her advice is always very helpful to me in finding the right problem to work on. She has also taught me to think critically when reading papers and encouraged me to develop my own ideas, which benefit not only my PhD study but also my future career. I still remember that we worked together until early morning, fighting my first paper deadline. This experience sounds painful, but to me, it is truly a wonderful memory. I am very glad that she received tenure recently.

I would like to thank my reliable collaborators, especially Dr. Kunal Agrawal and my lab mate, Kyle Singer. Kunal is a great theory person, and her insights on algorithms really make my research process smooth. She and Angelina together have also helped me to improve my presentation skills through the iterations of conference talk practice.

Kyle joined our group in 2017. He has brilliant abilities to build reliable and efficient runtime systems. I cannot have most of my work done without his support.

I want to thank the other members who serve on my committee: Dr. Sanjoy Baruah, Dr. Jeremy Buhler and Dr. Jeremy Fineman. Especially, I am very grateful to Dr. Fineman for his attendance at my defense virtually from Sydney after midnight.

I am fortunate to have these great friends during my graduate study at WashU: Ruixuan Dai, Shenghua He, Dingwen Li, Songshan Liu, Wei Tang, Xiaojian Xu, Hao Yan, and Huayi Zeng. We have had a lot of fun together, including working out in the gym, hiking, going to Karaoke, having hotpot, so on and so forth, which really makes my life here colorful. I would also like to thank all my friends in Shanghai, especially Weiwei Cai, Fan Gu, Merry Hou, Zhengzhen Huang, Liang Liang, Yong Sun and Yuanyuan Zhu, for often chatting with me and sharing me interesting news from my hometown.

I would like to thank my lovely girlfriend, Tiantian Zhu, for appearing in my life. Tiantian is the most shining girl I have ever met. Even if she is not a Computer Science person, she is always willing to listen to my complaints about the difficulties I met during my research. I am also thankful for her great cooking skills, which allow me to have had so much delicious Chinese food in St. Louis where there are not many good Chinese restaurants.

I would like to end this list of acknowledgments by showing my deepest gratefulness to my Dad and Mom, for having taught me everything that cannot be taught from schools, especially, to be a nice and kind person.

The work described in this dissertation is supported in part by the National Science Foundation under grant numbers CCF-1527692, CCF-1150036, CCF-1733873, CCF-1910568,

CCF-1943456, CCF-1533644, CCF-1725647 and CCF-1439062; and by the United States Air Force Research Laboratory under Cooperative Agreement Number FA8750-19-2-1000.

Yifan Xu

Washington University in St. Louis

December 2021

Dedicated to my parents,

Xu Jiu and Xu Ruiping,

who have encouraged me to begin this journey.

#### ABSTRACT OF THE DISSERTATION

Provably and Practically Efficient Race Detection for Task-Parallel Code

by

#### Yifan Xu

Doctor of Philosophy in Computer Science Washington University in St. Louis, 2021

Advisor: I-Ting Angelina Lee

Parallel systems are pervasive nowadays. Specifically, modern computers have embraced multicore architectures due to the difficulties of exploiting higher clock speeds on single-core CPUs. However, parallel programming is challenging. Determinacy race, in particular, is a common pitfall when writing task-parallel code. It can easily lead to non-deterministic behavior of the parallel program and therefore a determinacy race is often considered as a bug. Unfortunately, such bugs are hard to debug because they do not necessarily produce obvious failures in every single execution.

To ease the debugging process of determinacy races in task-parallel code, this dissertation proposes several provably and practically efficient parallel race detection algorithms. Unlike prior works mostly target fork-join parallelism, we focus on less structured but important programming paradigms – pipeline parallelism and futures. In addition, we build an efficient runtime system for scheduling futures, which is not only a facility to study the race detection problem for futures but also useful in practice. Finally, this dissertation investigates mechanisms that optimize the access history of race detectors, which provides significant additional boost to the performance.

xiv

# Chapter 1

# Introduction

Parallel systems are pervasive nowadays. Specifically, modern computers have embraced multicore architectures due to the difficulties of exploiting higher clock speeds on single-core CPUs. Unlike rising clock speeds, serial programs are not getting much performance boost through the parallel architectures. Scalable parallel programs, in contrast, can make full use of the powerful capabilities of multicore CPUs.

However, parallelization of applications can't be done automatically. Programmers are now required to write correct and scalable parallel programs explicitly despite the fact that the serial programming abstraction was widely used before. Worse yet, parallel programming is inherently more challenging than serial programming. For example, when programming with low-level threading APIs, such as POSIX thread [40], programmers need to manually manage task decomposition, scheduling and complex synchronization.

Fortunately, much effort has been made to simplify parallel programming. Task parallelism, for example, provides programmers with language constructs to express logical parallelism of the computation, and an underlying runtime system that performs the scheduling

and synchronization among parallel computations to achieve load balancing and coordination. Such high-level programming model allows programmers to focus on the decomposition of the problem and the design of the parallel algorithm.

# 1.1 Pitfall: Determinacy Race

Even though task parallelism meets a wide range of parallel programming needs, parallel programming still remains challenging for programmers. Unlike serial programs that are naturally deterministic, meaning that the program will always produce the same output given a particular input, parallel programs can easily become non-deterministic. Take the simple task-parallel code in Figure 1.1 as an example. The spawn keyword in the main function indicates that task1 can be executed concurrently with the continuation in which task2 is invoked (lines 9–10). Then the sync keyword causes the main function to suspend until task1 returns (line 11). A risk in this task-parallel code is that, task1 and task2 update the shared variable x with different values concurrently. Therefore the output value of x can vary, depending on the scheduling order.

```

int x;

1

2

void task1() {

3

x = 1;

5

void task2() {

x = 2;

6

7

8

int main() {

9

spawn task1();

10

task2();

11

12

printf("x is %d\n", x);

13

return 0;

14

```

Figure 1.1: A simple task-parallel code that contains determinacy races.

Such risk is commonly referred to as determinacy race. A *determinacy race* occurs when two or more logically parallel tasks perform memory operations on the same memory location and one of the operations is a write. <sup>1</sup> Determinacy races can lead to non-deterministic behavior and therefore they are often bugs. Unfortunately, such bugs are hard to debug because they do not necessarily produce obvious failures in every single execution.

To that end, many race detection algorithms [2, 9, 27–29, 55, 71, 72, 90, 97, 98] have been proposed in the context of task parallelism. The algorithms usually perform race detection on-the-fly as the program executes. For a given program and input, the race detection algorithms report a race if and only if the program contains a determinacy race for that input, regardless of the schedule. Moreover, the algorithms typically consist of two components: an access history that keeps track of the readers and the writers that previously accessed a given memory location during execution and a reachability data structure that, given a reader and a writer that accessed the same memory location, answers the question of whether or not they are logically in parallel.

# 1.2 Limitations of the Prior Studies

Each of the prior works has its own limitation. First, much of the prior work [9, 27–29, 55, 71, 72, 97] supports race detecting only fork-join parallelism (formally defined in Section 2.1). Fork-join parallelism has nice structural properties and such properties enable efficient race detection algorithms. A few prior works [2, 26, 90, 98] have studied the problems outside of the realm of fork-join parallelism. Due to the lack of structural properties, however, the algorithms execute the computation sequentially and incur a large overhead. Second, most of the work has been done focused on optimizing the reachability while little attention has been paid to the access history. It is often the most expensive component of race detection in practice while in theory, the access history adds no asymptotic overhead.

<sup>&</sup>lt;sup>1</sup>In contrast, a *data race* occurs when two parallel strands, holding no locks in common, access the same memory location in a conflicting way. A determinacy race is sometimes referred to as a *general race* [61].

## 1.3 Contributions

This dissertation, therefore, proposes several provably and practically efficient parallel race detection algorithms that detect determinacy races for computations that are less structured than fork-join parallelism. In addition, we have investigated mechanisms that optimize the access history component in race detection algorithms. The rest of this chapter briefly summarizes the contributions of this dissertation.

## Race detection for pipeline parallelism

We propose a provably correct and efficient race detection algorithm, **2D-Order**, for detecting races in pipeline parallelism. 2D-Order is the first known parallel race detection algorithm that targets pipeline program and given a computation, 2D-Order executes it while also detecting races with asymptotically constant overhead. We also implemented PRacer, a race detector based on 2D-Order for Cilk-P [48, 49], which is a language for expressing pipeline parallelism. Empirical results demonstrate that 2D-Order incurs reasonable overhead and exhibits scalability similar to the baseline (executions without race detection) when running on multiple cores.

Results of this study have previously appeared in the following publication:

Yifan Xu, I-Ting Angelina Lee, and Kunal Agrawal, Efficient Parallel Determinacy Race Detection for Two-Dimensional Dags, Proceedings of the 23rd Symposium on Principles and Practice of Parallel Programming (PPoPP'18), 2018.

# Race detection for future parallelism

A provably and practically efficient scheduler for future parallelism is needed when studying the race detection problem in the context of futures. However, a program with futures could incur much higher scheduling costs, when scheduling with the *classic work-stealing* algorithm (described in Section 2.3). Therefore, we first investigate an alternative scheduling

approach, called *proactive work-stealing*, an algorithm for scheduling the future parallelism with provably efficient execution time and better cache performance compared to classic work-stealing.

We then address race detection problems for programs with different use of futures, namely *general futures* and *structured futures*. Specifically, we present two algorithms: *F-Order* and *SF-Oder*. F-Order is the first known parallel race detection algorithm that detects races on programs using general futures. SF-Order, in contrast, exploits the restrictions imposed by structured futures, and therefore achieves better execution time compared to the race detection algorithm designed for general futures. We implemented both algorithms and empirically demonstrated their efficiency.

Results of this work have previously appeared in the following publications:

- Kyle Singer, Yifan Xu, and I-Ting Angelina Lee, Proactive Work Stealing for Futures, Proceedings of the 24th Symposium on Principles and Practice of Parallel Programming (PPoPP'19), 2019.

- Yifan Xu, Kyle Singer, and I-Ting Angelina Lee, Parallel Determinacy Race Detection for Futures, *Proceedings of the 25th Symposium on Principles and Practice of Parallel Programming* (PPoPP'20), 2020.

- Yifan Xu, Kunal Agrawal, and I-Ting Angelina Lee, Efficient Parallel Determinacy Race Detection for Structured Futures, Proceedings of the 33rd ACM Symposium on Parallelism in Algorithms and Architectures (SPAA'21), 2021.

# Optimizing access history

We propose compiler and runtime mechanisms that perform memory access coalescing efficiently, and a treap-based access history data structure. Together these optimization are capable of speeding up sequential race detectors for task-parallel code.

We then extend those optimization of access history to parallel race detectors by exploring an *asynchronous access history* scheme.

Results of part of this work have previously appeared in the following publication:

Yifan Xu, Anchengcheng Zhou, Grace Q. Yin, Kunal Agrawal, I-Ting Angelina Lee, and Tao B. Schardl, Brief Announcement: Efficient Access History for Race Detection, Proceedings of the 33rd ACM Symposium on Parallelism in Algorithms and Architectures (SPAA'21), 2021.

# 1.4 Roadmap

The rest of this dissertation is organized as follows. Chapter 2 reviews the backgrounds and introduces the terminologies used throughout this dissertation. Chapter 3 addresses the race detection problem for pipeline parallelism. Chapter 4 introduces future parallelism and presents proactive work-stealing – the scheduling algorithm that serves as an essential basis for the works in the following chapters. Chapter 5 and Chapter 6 propose race detection algorithms for general futures and structured futures, respectively. Chapter 7 investigates optimizations on access history to speed up sequential race detectors and Chapter 8 extends those optimizations to parallel race detectors. Chapter 9 reviews the related work. Chapter 10 concludes this dissertation by summarizing the results presented throughout the document.

# Chapter 2

# Preliminary

# 2.1 Task Parallelism

Task parallelism is a processor-oblivious programming model that provides programmers language constructs to express logical parallelism of the computation. During the execution of a task-parallel program, an underlying runtime scheduler automates tasks such as load balancing and coordination among parallel tasks. Task parallelism is widely supported by parallel programming platforms such as Intel TBB [43], Cilk dialects [24, 44, 50], Habanero dialects [7, 16] and X10 [18].

Based on the sets of language constructs used in the task-parallel program, one can divide task parallelism into categories. Take fork-join, a traditional parallelism paradigm supported by many task-parallel platforms, for example. Fork-join parallelism can be expressed using two simple keywords: spawn and sync. When a function F spawns off another function F by prefixing the invocation with spawn, the execution of F may operate in parallel with the continuation of F. The invocation of a sync specifies that all previously

spawned functions must return before the control can pass sync.<sup>2</sup> Figure 2.1 shows a simple fork-join code that computes the nth Fibonacci number in a naive way.

```

1 int fib(int n) {

if (n < 2) return n;

int x = spawn fib(n-1);

int y = fib(n-2);

sync;

return x + y;

}

</pre>

```

Figure 2.1: A simple fork-join code that computes the nth Fibonacci number.

# 2.2 Modeling Parallel Computations

One can model the execution of a parallel program as a directed acyclic graph (dag), where a node represents a strand or a series of sequential instructions without parallel constructs, and an edge represents a dependence between two strands. Given two nodes u and v such that there exists a path from u to v, for example, then the strand represented by u must be completed before executing the strand represented by v. In other words, the incidence relations of a dag can be viewed as order relations on its nodes and edges. Notation-wise, we write  $u \rightsquigarrow v$  to denote the presence of a directed path from u to v. We say  $u \prec v$  iff  $u \rightsquigarrow v$ ;  $u \preceq v$  iff either  $u \prec v$  or u = v. We say  $u \parallel v$  iff there is no path from u to v or from v to u.

Given a computation dag, one can measure its performance using two metrics: the **work** metric, which is the number of nodes in the dag, and the **span** metric, which is the length of the longest directed path through the dag, assuming each node takes unit time to execute. Equivalently, the work metric measures how long it takes to run this computation on one

<sup>&</sup>lt;sup>2</sup>Many task-parallel platforms also support parallel loops, which can be thought of as syntactic sugar that compiles down to spawn and sync.

core and the span metric measures how long it takes to run this computation on an infinite number of cores.

## Series-parallel dag

The execution of a fork-join program generates a series-parallel dag (SP-dag) with well-defined structural properties. An SP-dag is a planar dag with a unique source node with no incoming edges and a unique sink node with no outgoing edges. Specifically, the execution of a spawn creates a spawn node with two outgoing edges: one to the spawned function and one to the continuation of the caller. The execution of a sync creates a sync node that joins together all previously spawned functions — creating an edge from the end of a spawned function to the sync node that represents continuation after the sync statement. Without loss of generality, we shall assume that a sync node consists only only two incoming edges — it is not difficult to convert a sync node with multiple incoming edges into a chain of sync nodes, each with two incoming edges.

# 2.3 Work-Stealing Scheduler

A task-parallel computation can be scheduled efficiently using a work-stealing scheduler [4, 5, 13, 14]. A work-stealing scheduler dynamically load balances a parallel computation in a distributed fashion, which incurs low contention compared to centralized approaches (e.g., work-sharing). In classic work-stealing, each worker thread keeps its own double-ended queue (or deque for short) which holds ready nodes, that is, unexecuted nodes whose predecessors in the dag have all been executed. Each worker operates on its own deque locally. Specifically, when a worker executes a ready node in the dag and causes some child nodes to be ready, the worker pushes those ready nodes onto the bottom of its deque. Then the worker gets a new ready node by popping one off the bottom of its deque and continues to execute it. If a worker finds that its deque is empty, then the worker becomes a thief.

A thief worker chooses a victim worker uniformly at random and attempts to steal the top node of the victim's deque.

The work-stealing algorithm has been shown to provide strong performance guarantees [4, 5, 13, 14]. Given a parallel computation with work  $T_1$  and span  $T_{\infty}$ , a work-stealing scheduler executes it on P processors in expected execution time  $T_1/P + O(T_{\infty})$ .

# 2.4 Determinacy Race Detection

Parallel programming introduces additional pitfalls compared to serial programming. Programmers are required to specify the execution order between certain tasks to coordinate the parallel execution flow. Inappropriately defined orders can lead to concurrency bugs, e.g., races and deadlocks. This dissertation targets determinacy races. A *determinacy race* occurs when two or more logically parallel instructions access the same memory location, and at least one of them performs a write. Determinacy races may lead to non-deterministic behavior that is generally a programming error.

# On-the-fly race detector

In this work, we focus on performing race detection on-the-fly as the program executes. For a given program and input, we want to report a race if and only if the program contains a race for that input. As mentioned in Chapter 1, an on-the-fly race detector maintains two key data structures. An access history that stores the readers and the writers that previously accessed a given memory location, and a reachability data structure that determines whether two given accesses are logically in parallel or not, or equivalently whether or not there is a directed path between the corresponding nodes in the dag. For an on-the-fly race detector, the reachability data structure must be updated incrementally as new nodes in the dag are revealed during the execution. The race detector manages the data structures during the execution of the program. Given a strand u that accesses memory location l, the race

detector performs a reachability query between u and each conflicting access stored in the access history that accessed memory location l. If u is in parallel with any of the conflicting accesses, the detector finds a race.

## Race detection for fork-join programs

Recall from Section 2.2, a dag can be viewed as partial order relations on its nodes and edges. This leads to the definition of the order-dimension — the order-dimension of a dag G is the minimum number of total orders on G such that, given two nodes u and v in G,  $u \prec v$  iff u precedes v in all the total orders. SP-dags have been proved to have order-dimension two. Consequently, Nudler and Rudolph [62] introduce English and Hebrew order, that is, two total orders of nodes in SP-dags, to determine if two nodes are logically in parallel. Later, Bender et al. [9] propose SP-Order, the first race detection algorithm for SP-dags with asymptotically optimal sequential running time, using a pair of order-maintenance (OM) data structures to perform maintenance of English and Hebrew order of all revealed nodes. WSP-Order [97] parallelizes SP-Order by incorporating additional runtime support and achieves the optimal parallel executing time, that is, given an SP-dag with work  $T_1$  and span  $T_{\infty}$ , WSP-Order runs in time  $O(T_1/P + T_{\infty})$  on P cores.

# Chapter 3

# Race Detection for Pipeline Parallelism

Pipeline parallelism organizes a parallel program as a linear sequence of stages. Conceptually, each stage processes elements of a data stream and the stream flows through the pipeline from the first stage to the last stage. Pipeline parallelism is widely supported [3, 22, 35, 38, 52, 53, 64, 64, 68, 70, 73–76, 78, 89, 95], including Intel's Threading Building Blocks (TBB) [54], OpenMP [63], and Cilk-P [48, 49], an extension to Cilk designed specifically for linear pipelines. It has been shown that a program with pipeline parallelism can be scheduled efficiently using work-stealing [48, 49].

A pipeline program can be represented using a *two-dimensional dag (2D-dag)*, that is, a planar directed acyclic graph that can be embedded within a two-dimensional grid space.<sup>3</sup> In this chapter, we present 2D-Order, a provably correct and efficient race detection algorithm for 2D-dags, that has an asymptotically optimal parallel running time. Given a pipeline program with work  $T_1$  and span  $T_{\infty}$ , 2D-Order can detect races while executing the computation on P processors with expected time  $O(T_1/P + T_{\infty})$ . This bound is asymptotically optimal, since this is the best one can do when executing the same program without

$<sup>^3</sup>$ We formally define 2D-dags that our algorithm targets in Section 3.1.

race detection. 2D-Order provides a strong correctness guarantee — it reports a race if and only if the program has a race on that input.

Like prior work, 2D-Order has two main components: a reachability data structure and an access history component. Particularly, we find that 2D-dags have order-dimension two as SP-dags. Similar to SP-Order [9] and WSP-Order [97], as it executes the computation, 2D-Order maintains two total orders of the strands it has encountered. In Section 3.1, we define these two specific orders, show how to maintain them on the fly, and prove that maintaining these two orders suffices to answer the reachability query.

For parallel race detecting fork-join programs, Mellor-Crummey [55] proves that it suffices to store two readers and a single writer per memory location in the access history. We extend this result and show that two readers and one writer suffice for pipeline programs as well, which directly follows from the fact that the reachability data structure can be maintained with two orders.

The algorithm presented in Section 3.1 assumes that when a strand u is executed, we know how many children u has. This assumption may not hold for platforms that generate the pipeline dynamically. In Section 3.2, we present a variant of 2D-Order which only assumes that a strand v knows its parents when it executes; this assumption is generally true since v can only execute after all its parents have executed. This variant has the same performance bound.

The algorithms described in Sections 3.1 and 3.2 are formulated in terms of traversing a 2D-dag as the computation unfolds. In Section 3.3, we show how one can apply 2D-Order to the language constructs provided by Cilk-P [48, 49]. Cilk-P is an extension to the Cilk language that supports linear pipelines with a provably efficient work-stealing scheduler. Cilk-P is an interesting case study. Unlike most other systems, Cilk-P supports "on-the-fly" pipeline parallelism, where the structure of the pipeline emerges as the program executes.

We have also implemented PRacer, a prototype implementation of 2D-Order race detection algorithm applied to Cilk-P. Section 3.4 empirically evaluates the overhead of PRacer and shows that it incurs virtually no overhead for reachability maintenance and achieves similar scalability compared to applications' baseline executions without race detection.

# 3.1 2D-Order Algorithm

We now describe the basic 2D-Order algorithm. In this section, we make two simplifying assumptions: (1) We assume that a node u's children are known as soon as u finishes executing; and (2) There are no redundant edges — and edge from (u, v) is removed if there is already (a different) directed path from u to v. We will remove these assumptions in the next sections. We first provide some basic definitions before describing the 2D-Order's algorithm for reachability maintenance and proving its correctness. Then, we describe what information is kept in the access history and how 2D-Order checks for races. Finally, we prove the performance bound.

#### 3.1.1 Notations and Definitions

**Definition 1.** A **a two-dimensional dag (2D-dag)** is a planar directed acyclic graph with the following properties:

- 1. It has a unique source node s with no incoming edges and a unique sink node t with no outgoing edges.

- 2. Each node has at most two incoming and at most two outgoing edges. Edges are labeled as pointing either rightwards or downwards.

This definition implies that each node can have at most two children — the down child of a node v is denoted by v.dchild and the right child is denoted by v.rchild. Similarly, the up parent of v is denoted by v.uparent and the left parent is denoted by v.lparent.

**Definition 2.** Given two distinct nodes x and y, a node v is their **common ancestor** if  $v \leq x$  and  $v \leq y$ . A node z is their **least common ancestor**, denoted by lca(x, y), if for all common ancestors v of x and y, we have  $v \leq z$ .

By definition of a 2D-dag, a unique least common ancestor exists for any two nodes (proven in Lemma 9). The following lemma states that if  $x \parallel y$ , then their lca has two children, and x follows from one while y follows from the other.

**Lemma 3.** For two nodes x and y, say  $x \parallel y$  and z = lca(x, y). Then we have (1) z has two children; (2) if z.dchild  $\leq x$  then z.dchild  $\parallel y$ , z.rchild  $\leq y$ , and z.rchild  $\parallel x$ .

*Proof.* Suppose that, for contradiction,  $w \leq x$  and  $w \leq y$  where w is a child of z; by Definition 2  $z \neq lca(x,y)$ .

This lemma allows us to relate any two parallel nodes.

**Definition 4.** Given two nodes x and y where  $x \parallel y$ . Let z = lca(x, y). Then, x is **down of**  $(\parallel_D)$  y iff z.dchild  $\leq x \& z$ .rchild  $\leq y$ , and x is **right of** y  $(\parallel_R)$  iff z.dchild  $\leq y \& z$ .rchild  $\leq x$ .

We now make some straightforward structural observations. (1) For distinct nodes x and y, exactly one of the following four conditions hold:  $x \prec y$ ,  $y \prec x$ ,  $x \parallel_D y$  or  $y \parallel_D x$ . (2) Given a node x with two children,  $x.dchild \parallel_D x.rchild$ .

# 3.1.2 Reachability in 2D-Order Algorithm

2D-Order maintains two total orders on all strands using order-maintenance data structures. An order-maintenance (OM) data structure D maintains a total order of elements and provides the following operations.

• OM-Precedes(D, x, y): Given pointers to x and y, return true iff x precedes y in the total order kept by D.

• OM-Insert(D, x, y): Given a pointer to an existing element x, splice-in a new element y immediately after x in the total order. Thus, x and all its predecessors of x are before y in the total order, while all successors of x are after y.

**Algorithm 1:** 2D-Order: Reachability Maintenance 1 Function Insert-Down-First (v)if v.rchild exists then if v.rchild.uparent not exists then OM-Insert (OM-DownFirst, v, v.rchild) if v.dchild exists then 5 OM-Insert (OM-DownFirst, v, v.dchild) 6 **Function** Insert-Right-First (v)7 if v.dchild exists then if v.dchild.lparent not exists then 9 OM-Insert (OM-RightFirst, v, v.dchild) 10 if v.rchild exists then 11 OM-Insert (OM-RightFirst, v, v.rchild) 12

2D-Order keeps two OM data structures — called OM-RightFirst and OM-DownFirst — to maintain two different orders on all the nodes in the 2D-dag. The OM data structures for both orders are initialized by inserting the source node s as the first node. Subsequently, it executes nodes of the dag in any valid serial or parallel order — that is, a node can be executed when it's predecessors have finished executing. After executing each node v, 2D-Order calls the two functions shown in Algorithm 1.

Function Insert-Down-First (v) inserts v's children into the OM-DownFirst data structure. Immediately after this function is executed, the following will be true in the OM-DownFirst order: (a) If v has a down child  $v_D$ , then  $v_D$  will be immediately after v. (2) If v has a right child  $v_R$  and  $v_R$  doesn't have an up parent, then  $v_R$  will be immediately after  $v_D$  (if  $v_D$  doesn't exist, then  $v_R$  will be immediately after v). The symmetric invariant is true for the function Insert-Right-First (v).

In other words, for any node u, its up parent is "responsible" for inserting it into the OM-DownFirst data structure and its left parent is "responsible" for inserting it into the OM-RightFirst data structure. If u doesn't have one of the parents, however, then u's other parent takes over the corresponding responsibility and inserts u immediately after its other child (or after the parent itself if the other child doesn't exist). It should be clear that each node u is inserted into each OM data structure exactly once and these insertions happen before u itself is executed.

To simplify notation, we say that  $x \to_D y$  if x occurs before y in the OM-DownFirst data structure (that is, if OM-Precedes(OM-DownFirst, x, y) returns true). Similarly, we say  $x \to_R y$  if OM-Precedes(OM-RightFirst, x, y) returns true. Note that since the algorithm never swaps the order of the nodes once they are inserted, the answer returned will be consistent once both x and y are inserted.

# 3.1.3 OM-DownFirst and OM-RightFirst Maintain Reachability Relationships

We will now prove that these two total orders are sufficient to fully specify the partial order of the dag. The following theorem, which we prove in the remaining subsection, shows that given any two nodes x and y, we can determine the relationship between them just by looking at the total orders maintained by OM-DownFirst and OM-RightFirst; if x is before y in both orders, then  $x \prec y$ ; if y is before x in both orders, then  $y \prec x$ ; otherwise  $x \parallel y$ .

**Theorem 5.** Given nodes x and y in OM-DownFirst and OM-RightFirst,  $x \prec y$  iff  $x \rightarrow_D y$  and  $x \rightarrow_R y$ .

We first prove some structural properties of 2D-dags. Lemma 6 (stated without proof) says that any subdag G' of a 2D-dag G that has a single source and a single sink is also a 2D-dag. Then, we prove that any source to sink path cuts 2D-dags into disjoint graphs with certain properties (Lemmas 7 and 8).

**Lemma 6.** Consider two nodes a and b in a 2D-dag G where  $a \prec b$ . Construct a subdag G' such that  $x \in G'$  if  $a \preceq x \preceq b$  and edge  $(x, y) \in G'$  if  $(x, y) \in G$ . Then G' is a 2D-dag with source a and sink b.

Figure 3.1: A path P divides a 2D-dag into two regions,  $P_R$  (shaded with horizontal lines) and  $P_D$  (shaded in vertical lines).

Consider a path P from the source s of a 2D-dag to its sink t. We use this path to divide all nodes of the dag into three subsets P,  $P_R$  and  $P_D$ . P contains all the nodes on the path. Note that for all  $u \in P$ , at least one of u's children (unless u = t) and one of u's parents (unless u = s) is also in P. Consider a node  $u \notin P$  — since  $s \in P$ , u has at least one ancestor in P. Say q is the ancestor of u which is topologically latest in the path P. Since nodes on P are totally ordered, there is necessarily this latest node. Then,  $u \in P_D$  if it follows from q's down child — that is, if q. Similarly,  $u \in P_R$  if q. The intuitive meaning of  $P_R$  and  $P_D$  is shown in Figure 3.1 where path P cleanly divides the graph into two "contiguous regions." We now prove that the definition matches this intuitive meaning.

**Lemma 7.** For any path P,  $P_R \cap P_D = \emptyset$  and any path from node u to node v where  $u \in P_R$  and  $v \in P_D$  must include some node on P.

Proof. First, we prove disjointness. Consider  $u \notin P$  and say q is u's ancestor which is topologically latest in P; since at least one of q's children must be in P, u cannot follow from both its children. Now, assume for contradiction that there is a path from u to v that has no node in P. Then the latest ancestor of u and v on P must be the same node — which is a contradiction since  $u \in P_R$  and  $v \in P_D$ .

#### **Lemma 8.** For any node $u \in P$ ,

- 1. If u has two children and u.rchild  $\in P$ , then u.dchild  $\in P_D$ . (Similarly, if u.dchild  $\in P$ , then u.rchild  $\in P_R$ .)

- 2. If u has two parents, if u.lparent  $\in P$ , then u.uparent  $\in P_R$ . (Similarly, if u.uparent  $\in P$ , then u.lparent  $\in P_D$ .)

PROOF SKETCH. The first statement is obvious from definition, because  $u \in P$  and u must be the latest ancestor of u.dchild in P. The easy way to see the second statement is to notice that if we flip the direction of all edges and rotate the dag, then source becomes sink, u.uparent becomes u.dchild, and u.lparent becomes u.rchild, and  $P_R$  becomes  $P_D$ . To formally prove it, one can induct on the nodes on the path.

We can now use Lemma 7 to prove that any two nodes have a unique lca.

#### **Lemma 9.** Given two nodes x and y which are in parallel, lca(x,y) exists uniquely.

Proof. For the purpose of contradiction, assume two leas exist, named z and z'. By the fact that they are both lca(x, y), they must be in parallel with each other. Wlog, assume  $z' \parallel_D z$  and let u = lca(z', z). Also wlog assume that  $x \parallel_D y$  with respect to z (i.e., x follows from z.dchild). Construct a path P that goes from the source s to u to u.rchild to z to z.dchild to x to the sink t; such a path exists by the property of 2D-dags and leas. Then, as shown in Figure 3.2,  $z' \in P_D$  (since it follows from u.dchild) and  $y \in P_R$  (since it follows from z.rchild). However, since z' = lca(x, y), there must be a path P' from z' to y, which must

Figure 3.2: Figure for Lemma 9. Assume two leas for x and y exist, namely z and z', and let u be a lea of z and z'.

cross P by Lemma 7. If P' cross P before z, it contradicts with the fact that no path exists between z and z'. If P' cross P after z, it contradicts with the fact that z = lca(x, y). Thus, the lca(x, y) must be unique.

We now use these paths to prove a lemma about the insertion order between nodes.

**Lemma 10.** At any point during the execution of 2D-Order, given node x which has two children. If  $x.dchild \notin OM$ -DownFirst, then for any y such that  $x.dchild \prec y$  and  $x.rchild \parallel y$ ,  $y \notin OM$ -DownFirst.

*Proof.* Consider the 2D-subdag G' with source s and sink y. Let S be the set of all the nodes on paths from s to y. Now we construct path P using nodes from set S: for any node u such that  $u \in S$  and  $u \notin P$ , we have  $u \in P_D$ . Intuitively, P follows the "top-most right-most" path among all paths from s to y.

First we prove  $x \in P$ . Suppose  $x \notin P$ , then by the constraint of path P, we have  $x \in P_D$ . Since  $x.rchild \notin P$  because  $x.rchild \parallel y$ , we also have  $x.rchild \in P_D$ . Now construct a path P' from s to x to x.dchild to y. By Lemma 8,  $x.rchild \in P'_R$ . Let  $R = P'_R \cap P_D$  (the shaded region in Figure 3.3). Now consider the whole 2D-dag G with source s and sink t, which

Figure 3.3: Figure for Lemma 10. Path P is shown in red, and path P' is in blue. The shaded region is R. The node  $x_d$  is x.dchild and the node  $x_r$  is x.rchild.

includes R. Since  $x.rchild \in R$  (the shaded region) and  $t \notin R$ , a path from x.rchild to t must cross with either path P P'. Since both P and P' ends at y, this means  $x.rchild \prec y$ , which contradicts with the original assumption that  $x.rchild \parallel y$ . Therefore, we are guaranteed that  $x \in P$ .

Since P is a continuous path and  $x.rchild \notin P$ , we must have  $x.dchild \in P$ . Now we show P is actually an insertion chain, which means for any node w in P except for s, w is inserted by its parent in P.

Let v and w be two consecutive nodes in P and  $v \prec w$ . For the purpose of contradiction, let's assume that w is not inserted by v. According to the Down-First part of algorithm 1, this can only happen when w has two parents in G and v = w.lparent. Since  $v \in P$ , we have  $v.uparent \in P_R$  by Lemma 8. However, since  $v.uparent \in S$ , it is guaranteed that either  $v.uparent \in P$  or  $v.uparent \in P_D$ , which leads to a contradiction. Thus, P is an insertion chain. Since we know that  $v.uparent \in P$ , and  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ ,  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ ,  $v.uparent \in P$ , and  $v.uparent \in P$ ,  $v.uparent \in P$ , v.

We can now prove the two important properties of down-first order — namely that  $x \to_D y$  if  $x \parallel_D y$  or if  $x \prec y$ .

**Lemma 11.** At any point during the execution of 2D-Order, given nodes x and y in OM-DownFirst. If  $x \parallel_D y$ , then  $x \to_D y$ .

*Proof.* We prove this lemma by induction. Suppose lemma is true before insertion is invoked on a node y. Consider any x in OM-DownFirst. We will show if  $x \parallel_D y$ , then  $x \to_D y$ . Let z = lca(x, y); we have  $z.dchild \preceq x$  and  $z.rchild \preceq y$  (The case where  $y \parallel_D x$  is similar.)

- 1. y has one single parent w: We first consider the case where z = w and z.rchild = y. Since z.dchild has not been inserted in OM-DownFirst yet, and since x must follow from z.dchild, from Lemma 10, we know x has not been inserted. So this case is trivial. Say  $z.rchild \neq y$ ; then, we have z = lca(w, x) and  $x \parallel_D w$ . By inductive hypothesis, we know  $x \rightarrow_D w$ . Because y is inserted immediately after w, therefore it's guaranteed that  $x \rightarrow_D y$ .

- 2. y has two parents: According to algorithm 1, y is inserted immediately after its up parent y.uparent, say w. We now argue that  $x \parallel_D w$ . Let z' = lca(w, x). We know that  $z' \leq z$ . If z' = z, then we are done. For the rest of the proof, we assume that  $z \parallel w$ ; therefore, z' = lca(z, w) since z' is an ancestor of z.

Assume for contradiction that  $w \parallel_D x$ ; therefore  $z'.dchild \leq w$ . Therefore,  $z'.rchild \leq z$ . Consider the 2D-dag G' with source z' and sink t and consider a path P that goes from z' to z'.dchild to w to y to t. We know that  $z'.rchild \in P_R$  (from Lemma 8); therefore,  $z \in P_R$  since otherwise, the path from z' to z will cross P at some node a and this node a = lca(z, w) instead of z'. However, we also know that  $y.lparent \in P_D$  (from Lemma 8) and  $z \leq y.lparent$ . Therefore, the path from z to y.lparent must cross P at some node b and this would mean that z is an ancestor of w which contradicts the assumption.

Therefore  $x \parallel_D w$  and by IH,  $x \to_D w$ ; therefore, when y is inserted immediately after w, we have  $x \to_D y$ .

**Lemma 12.** At any point during the execution of 2D-Order, given nodes x and y in OM-DownFirst. If  $x \prec y$ , then  $x \rightarrow_D y$ .

*Proof.* We prove this lemma by induction. Suppose lemma is true before insertion is invoked on a node y. Consider any node x in OM-DownFirst.

We first show if  $y \prec x$  then  $y \to_D x$ . Let w be the parent that inserted y. Since  $y \prec x$ ,  $w \prec x$ . By IH,  $w \to_D x$  before the insertion, and thus  $w \to_D y \to_D x$  after the insertion.

Now we show if  $x \prec y$ , then  $x \to_D y$ .

- 1. y has one single parent w: In this case, y is inserted by this parent w immediately after w. Therefore, clearly,  $w \to_D y$ . Also, if  $x \prec y$ , then  $x \preceq w$  since w is y's only parent. If x = w, we are done. If not, according to the inductive hypothesis, we have  $x \to_D w$ . Therefore, we know  $x \to_D y$ .

- 2. y has two parents: We know y is inserted immediately after y.uparent. If  $x \leq y.uparent$ , we can apply the same argument as in the single parent case. Now consider the case that  $x \parallel y.uparent$  and  $x \leq y.lparent$ . We will show that  $x \parallel_D y.uparent$  and by Lemma 11, we then have  $x \to_D y.uparent$ , which leads to  $x \to_D y$ .

For the purpose of contradiction, let's assume that  $y.uparent \parallel_D x$  and let z = lca(x, y.uparent). Consider the subdag with source z and sink t and construct a path P from z to z.rchild to x to y to t. Then by Lemma 8, we have  $y.uparent \in P_R$  and  $z.dchild \in P_D$ . Since  $y.uparent \parallel_D x$ , there must be a path P' from z.dchild to y.uparent, which must cross P by Lemma 7, which contradicts the assumption that z = lca(x, y.uparent). Thus we must have  $x \parallel_D y.uparent$  and thus  $x \to_D y$ .

Symmetrically, one can prove the following lemmas:

**Lemma 13.** At any point during the execution of 2D-Order, given nodes x and y in OM-RightFirst. If  $x \prec y$ , then  $x \rightarrow_R y$ .

**Lemma 14.** At any point during the execution of 2D-Order, given nodes x and y in OM-RightFirst. If  $x \parallel_R y$ , then  $x \to_R y$ .

Now we can prove the main result:

**Proof of Theorem 5.** From Lemma 12 and Lemma 13, it's straightforward to see that if  $x \prec y$ , then  $x \to_D y$  and  $x \to_R y$ . For the other direction, suppose  $x \parallel y$  when  $x \to_D y$  and  $x \to_R y$ . Wlog, say  $y \parallel_D x$ . Then we have  $y \to_D x$  by Lemma 11, which contradicts to  $x \to_D y$ .

### 3.1.4 Checking Races and Updating Access History

```

Algorithm 2: 2D-Order: Access Histories

/\star Called when a strand r read memory location l

*/

1 Function Read (r, l)

if Precedes (writer(l), r) is false then

ReportRace ( );

if OM-Precedes (OM-RightFirst, dreader(l), r) then

dreader(l) = r;

if OM-Precedes (OM-DownFirst, rreader(l), r) then

6

rreader(l) = r;

/\star Called when a strand w wrote to memory location l

*/

s Function Write (w, l)

if Precedes (writer(l).w) is false

or Precedes (dreader(l), w) is false

10

or Precedes (rreader(l), w) is false then

ReportRace();

12

writer(l) = w;

/* When called, we have either u \prec v or u \parallel v, but never v \prec u

*/

14 Function Precedes (u, v)

if OM-Precedes (OM-DownFirst, u, v)

15

and OM-Precedes (OM-RightFirst, u, v) then

16

17

return true

return false

18

```

We now describe how we do race detection using this algorithm — the code is shown in Algorithm 2. For each memory location  $\ell$ , our algorithm stores at most one previous writer node — called *last writer*  $writer(\ell)$  — this is simply the last node that wrote to

this memory location. If a set of reader nodes  $R_{\ell}$  have read this memory, the algorithm stores up to two reader nodes: (1) **downmost reader**  $dreader(\ell)$ : For all  $r \in R_{\ell}$ , either  $r \leq dreader(\ell)$  or  $r \parallel_R dreader(\ell)$ ; and (2) **rightmost reader**  $dreader(\ell)$ : For all  $r \in R_{\ell}$ , either  $r \leq rreader(\ell)$  or  $r \parallel_D rreader(\ell)$ .

When a node u tries to write location  $\ell$ , it uses the OM-DownFirst and OM-RightFirst data structures to check whether either  $dreader(\ell) \parallel u$ ,  $rreader(\ell) \parallel u$  or  $writer(\ell) \parallel u$ . If so, we report a race. In either case, u is now last writer  $writer(\ell)$ . When node u tries to read location  $\ell$ , it uses the OM-DownFirst and OM-RightFirst data structures to check whether  $writer(\ell) \parallel u$ . If so, we report a race. In either case, u now checks if  $dreader(\ell) \rightarrow_R u$ ; if so, u is the new downmost reader  $dreader(\ell)$ . Similarly, if  $rreader(\ell) \rightarrow_D u$ , then u is the new  $rreader(\ell)$ .

**Theorem 15.** 2D-Order never reports false races and for racy programs, reports at least one race.

This is the standard correctness guarantee for on-the-fly race detection algorithms. The proof mostly follows from previous results — with the exception of one wrinkle. It is always sufficient to store a single writer in access history; however, it is not always sufficient to store two readers. In particular, for general dags, one has to store all parallel reads that happened since the last write. Mellor-Crummey [55] proved that for series-parallel dags, it is sufficient to record two readers. We will now show that for 2D-dags, it is also sufficient to store two readers — in particular, the downmost and the rightmost readers.

First, let us notice that at any point in the execution  $rreader(\ell)$  (and  $dreader(\ell)$ ) is unique (or null if no node has read  $\ell$  yet). To see this, note that from Algorithm 2, lines 6 and 7,  $rreader(\ell)$  is simply the last node in the order maintained by OM-DownFirst that read  $\ell$ .

**Theorem 16.** At any point during the execution of a 2D-dag, let  $R_{\ell}$  be the set of nodes that have read memory location  $\ell$  and w be any other node. We have  $r \prec w$  for all  $r \in R_{\ell}$  if and only if  $dreader(\ell) \prec w$  &  $rreader(\ell) \prec w$ .

*Proof.* It is clear that if all  $r \in R_{\ell}$  precede w then so do  $dreader(\ell)$  and  $rreader(\ell)$  since they belong to the set  $R_{\ell}$ .

Now say that  $dreader(\ell) \prec w \& rreader(\ell) \prec w$ . For any  $r \in R_{\ell}$ , we have,  $r \to_R dreader(\ell) \to_R w$  (the first arrow is by definition of downmost reader and the second from Theorem 5). Similarly, we have  $r \to_D rreader(\ell) \to_D w$ . Therefore r is before w in both OM-DownFirst and OM-RightFirst orders; by Theorem 5, we know that  $r \prec w$ .

### 3.1.5 Performance of 2D-Order

**Theorem 17.** For a 2D-dag G with work  $T_1$  and span  $T_{\infty}$ , we can run do race detection using 2D-Order in time  $T_1/P + T_{\infty}$  time on P processors.