#### Washington University in St. Louis

## Washington University Open Scholarship

All Computer Science and Engineering Research

Computer Science and Engineering

Report Number: WUCS-88-28

1988-08-31

## **Advanced Communications Systems**

Jonathan S. Turner

The Advanced Communications Systems Project is concerned with new communication technologies that can support a wide range of different communication applications in the context of large public networks. Communication networks in common use today have been tailored to specific applications and while they perform their assigned functions well, they are difficult to adapt to new uses. There currently are no general purpose networks, rather there are telephone networks, low-speed data network and cable television networks. As new communication applications proliferate, it becomes clear that in the long term, a more flexible communication infrastructure will be needed. The Integrated Service... Read complete abstract on page 2.

Follow this and additional works at: https://openscholarship.wustl.edu/cse\_research

#### **Recommended Citation**

Turner, Jonathan S., "Advanced Communications Systems" Report Number: WUCS-88-28 (1988). *All Computer Science and Engineering Research.*

https://openscholarship.wustl.edu/cse\_research/785

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160.

This technical report is available at Washington University Open Scholarship: https://openscholarship.wustl.edu/ cse\_research/785

### **Advanced Communications Systems**

Jonathan S. Turner

#### **Complete Abstract:**

The Advanced Communications Systems Project is concerned with new communication technologies that can support a wide range of different communication applications in the context of large public networks. Communication networks in common use today have been tailored to specific applications and while they perform their assigned functions well, they are difficult to adapt to new uses. There currently are no general purpose networks, rather there are telephone networks, low-speed data network and cable television networks. As new communication applications proliferate, it becomes clear that in the long term, a more flexible communication infrastructure will be needed. The Integrated Service Digital Network concept provides a first step in that direction. We are concerned with the next generation of systems that will ultimately succeed ISDN. The main focus of the effort in the ACS project is a particular switching technology we call broadcast packet switching. The key attributes of this technology are (1) the ability to support connections of any data rate from a few bits per second to over 100 Mb/s, (2) the ability to support flexible multi-point connections suitable for entertainment video, LAN interconnection and voice/ video teleconferencing, (3) the ability to efficiently support bursty information sources, (4) the ability to upgrade network performance incrementally as technology improves and (5) the separation of information transport functions from applications-dependent functions so as to provide maximum flexibility for future services.

### ADVANCED COMMUNICATIONS SYSTEMS

Jonathan S. Turner

WUCS-88-28

September 1, 1987 - August 31, 1988

Department of Computer Science Washington University Campus Box 1045 One Brookings Drive Saint Louis, MO 63130-4899

with Mark A. Franklin, Guru Parulkar, Pierre Costa, Makoto Imase, Riccardo Melen, Akira Arutaki, Shahid Akhtar, Neil Barrett, Victor Griswold, Mark Hunter, Scott Johnson, Shabbir Khakoo, Tony Mazraani, Anne Reynolds, George Robbert, James Sterbenz, Einir Valdimarsson and Bernard Waxman.

## Research Objectives

The Advanced Communications Systems Project is concerned with new communication technologies that can support a wide range of different communication applications in the context of of large public networks. Communication networks in common use today have been tailored to specific applications and while they perform their assigned functions well, they are difficult to adapt to new uses. There currently are no general purpose networks, rather there are telephone networks, low-speed data networks and cable television networks. As new communication applications proliferate, it becomes clear that in the long term, a more flexible communication infrastructure will be needed. The Integrated Services Digital Network concept provides a first step in that direction. We are concerned with the next generation of systems that will ultimately succeed ISDN.

The main focus of the effort in the ACS project is a particular switching technology we call broadcast packet switching. The key attributes of this technology are (1) the ability to support connections of any data rate from a few bits per second to over 100 Mb/s, (2) the ability to support flexible multi-point connections suitable for entertainment video, LAN interconnection and voice/video teleconferencing, (3) the ability to efficiently support bursty information sources, (4) the ability to upgrade network performance incrementally as technology improves and (5) the separation of information transport functions from application-dependent functions so as to provide maximum flexibility for future services.

## Acknowledgements

The Advanced Communications Systems Project operates within the Computer and Communications Research Center, an inter-departmental research laboratory in the School of Engineering and Applied Science at Washington University. The Center's research program seeks an appropriate balance between theoretical and practical issues and has attracted considerable interest world-wide. Program sponsors interact with the Center through exchange of information and personnel.

The ACS project began on January 1, 1986. Our current sponsors are

National Science Foundation (grant DCI 8600947)

Bell Communications Research

Bell Northern Research

Italtel SIT

Nippon Electric Corporation

We thank all our sponsors for their collaboration and support. Special thanks go to Gil Devey and Steve Wolff at NSF, Eric Nussbaum and Neil Haller of Bell Communications Research, Al Winterbauer and Dan Stevenson of BNR, Maurizio Dècina and Anna Robrock of Italtel and Akihiro Kitamura and Takehiko Yamaguchi of NEC. We also thank Washington University for providing an excellent environment in which to carry out this work, in particular Dean James McKelvey and CS Department Chairman Jerry Cox for all their support and encouragement.

# Contents

| 1 | Su                                         | mmary of Progress                    | 1  |  |  |  |  |

|---|--------------------------------------------|--------------------------------------|----|--|--|--|--|

| 2 | Sw                                         | itch Architecture Studies            | 13 |  |  |  |  |

|   | 2.1                                        | Bit-Sliced Switch Fabrics            | 13 |  |  |  |  |

|   | 2.2                                        | Switches for Connectionless Networks | 21 |  |  |  |  |

| 3 | No                                         | Nonblocking Multirate Networks       |    |  |  |  |  |

|   | 3.1                                        | Strictly Nonblocking Networks        | 31 |  |  |  |  |

|   | 3.2                                        | Rearrangeably Nonblocking Networks   | 34 |  |  |  |  |

|   | 3.3                                        | Multipoint Networks                  | 36 |  |  |  |  |

|   | 3.4                                        | Complexity of Multirate Networks     | 40 |  |  |  |  |

| 4 | Prototype Hardware Design                  |                                      |    |  |  |  |  |

|   | 4.1                                        | Packet Formats                       | 44 |  |  |  |  |

|   | 4.2                                        | Timing                               | 49 |  |  |  |  |

|   | 4.3                                        | Packet Switch Element                | 51 |  |  |  |  |

|   | 4.4                                        | Packet Processor                     | 53 |  |  |  |  |

|   | 4.5                                        | Broadcast Translation Circuit        | 62 |  |  |  |  |

| 5 | Tools for Design of Communication Circuits |                                      |    |  |  |  |  |

|   | 5.1                                        | Synchronous Streams Processors       | 65 |  |  |  |  |

|   | 5.2                                        | Memory Generators                    | 72 |  |  |  |  |

|   | 5.3                                        | Control and Timing                   | 75 |  |  |  |  |

|   | 5.4                                        | Test Vector Generation               | 76 |  |  |  |  |

|   | 5.5                                        | Register Generator                   | 79 |  |  |  |  |

|   | 5.6                                        | Timing Diagram Generator             | 80 |  |  |  |  |

| 6 Multipoint Routing |                |                                                   |     |  |  |

|----------------------|----------------|---------------------------------------------------|-----|--|--|

| 7                    | $\mathbf{Vid}$ | eo Coding in Packet Networks                      | 89  |  |  |

|                      | 7.1            | Video Coding in a Diverse Application Environment | 89  |  |  |

|                      | 7.2            | Packet Transport of Video Signals                 | 93  |  |  |

|                      | 7.3            | Implications of Multicast Environment             | 94  |  |  |

| 8                    | ${ m Hi}_{i}$  | gh Speed Internetworks                            | 97  |  |  |

|                      | 8.1            | Elements of an Extended Internet Model            | 98  |  |  |

|                      | 8.2            | Design and Implementation Issues                  | 103 |  |  |

# List of Figures

| 1.1  | Publications and Related Activities                     | 2  |

|------|---------------------------------------------------------|----|

| 1.2  | Theses and Technical Reports                            | 3  |

| 1.3  | Current Graduate Students                               | 10 |

| 1.4  | Graduates                                               | 10 |

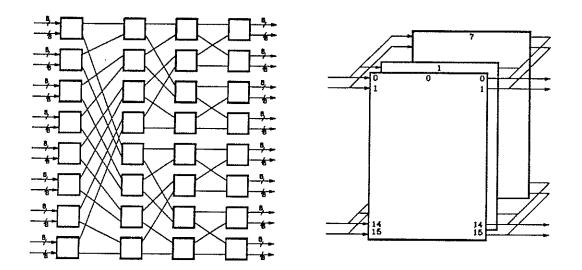

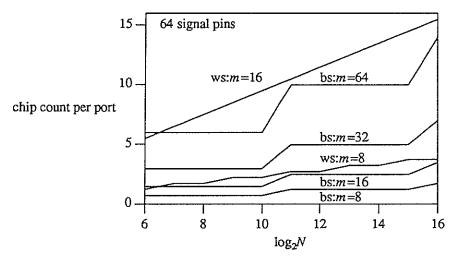

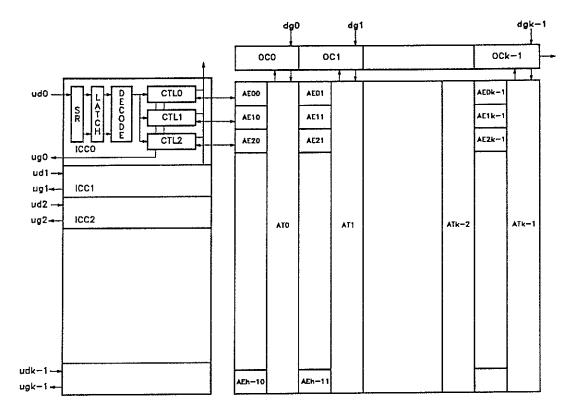

| 2.1  | Comparison of Word-Serial and Bit-Sliced Organizations  | 14 |

| 2.2  | Complexity of Word-Serial and Bit-Sliced Beneš Networks | 14 |

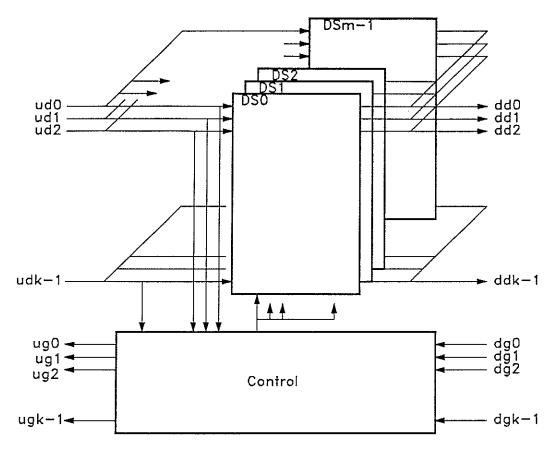

| 2.3  | Bit-Sliced Switch Element                               | 15 |

| 2.4  | Data Slice with Input Buffering                         | 16 |

| 2.5  | Control Slice                                           | 18 |

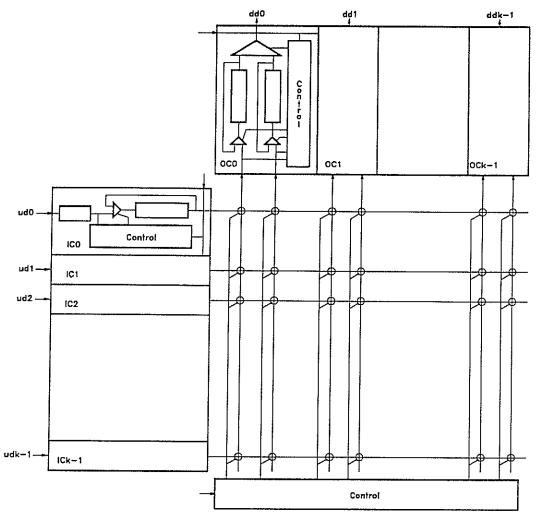

| 2.6  | Data Slice with Output Buffering                        | 20 |

| 2.7  | Data Slice with Shared Buffering                        | 21 |

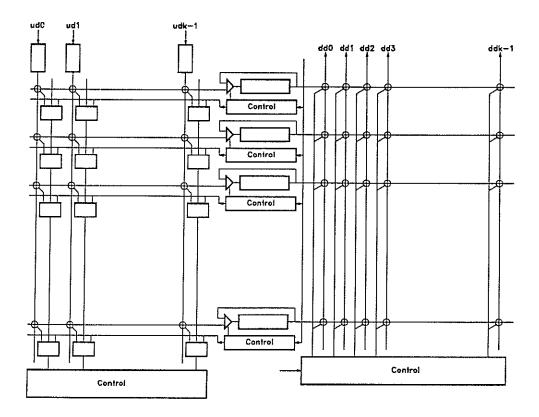

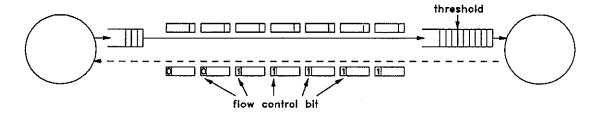

| 2.8  | Simple Flow Control Across a Link                       | 23 |

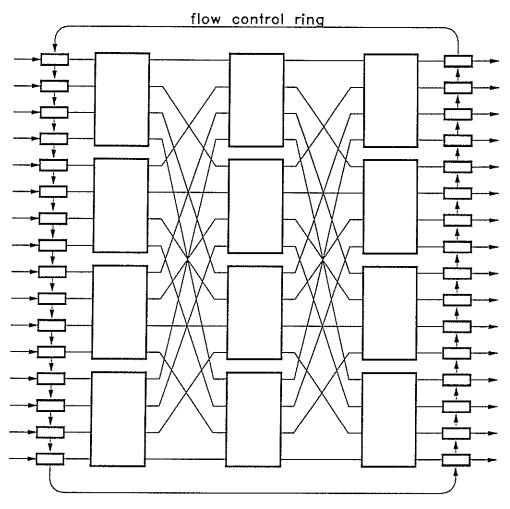

| 2.9  | Flow Control Across a Switch                            | 24 |

| 2.10 | Datagram Address Translation                            | 25 |

| 2.11 | Content Addressable Memory Cells                        | 25 |

| 3.1  | Clos Network                                            | 32 |

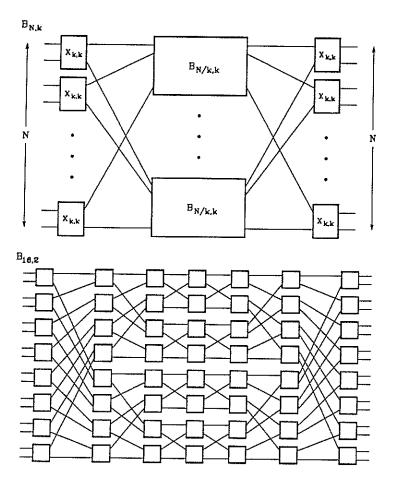

| 3.2  | Beneš Network $(B_{N,k})$                               | 33 |

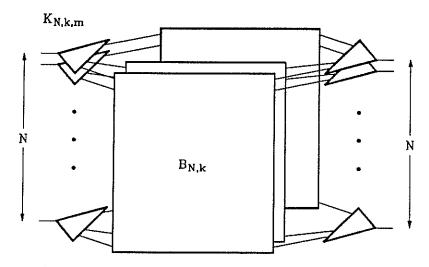

| 3.3  | Cantor Network                                          | 34 |

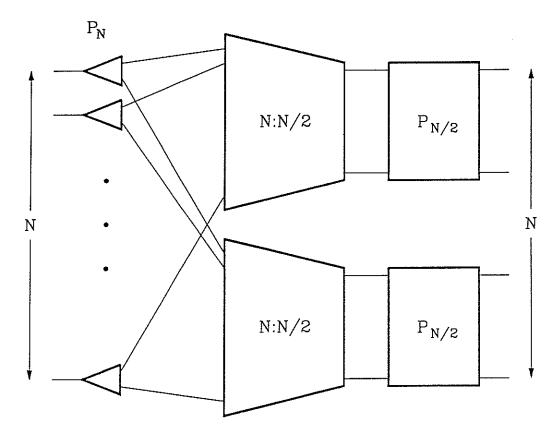

| 3.4  | Recursive Construction of $P_N$                         | 37 |

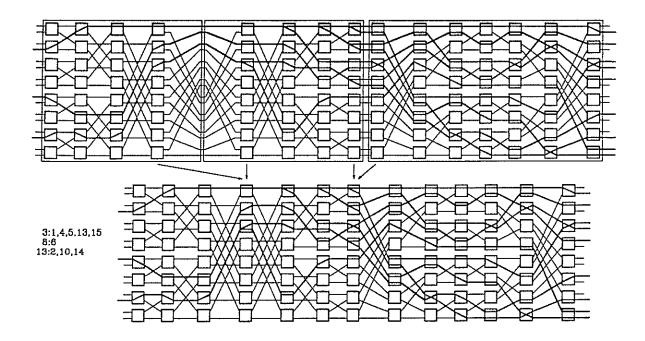

| 3.5  | Example of Routing in $T_{N2}$                          | 39 |

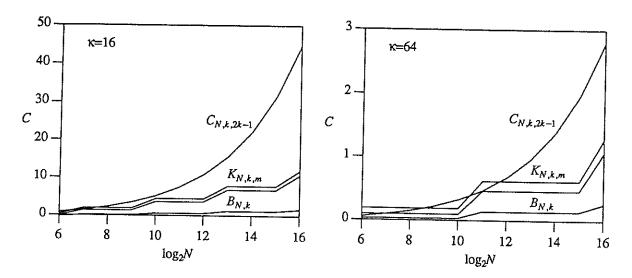

| 3.6  | Complexity of Multirate Networks: Beneš is shown for rearrangeable and strictly nonblocking case. $\beta=1/2$ for Clos and Kantor | 42 |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----|

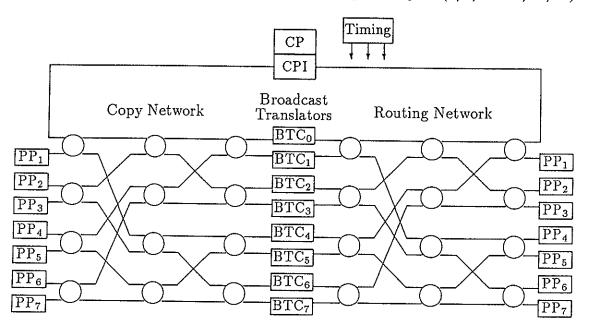

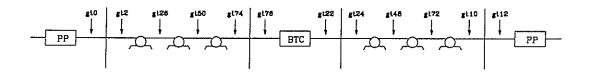

| 4.1  | Prototype Switch Module                                                                                                           | 44 |

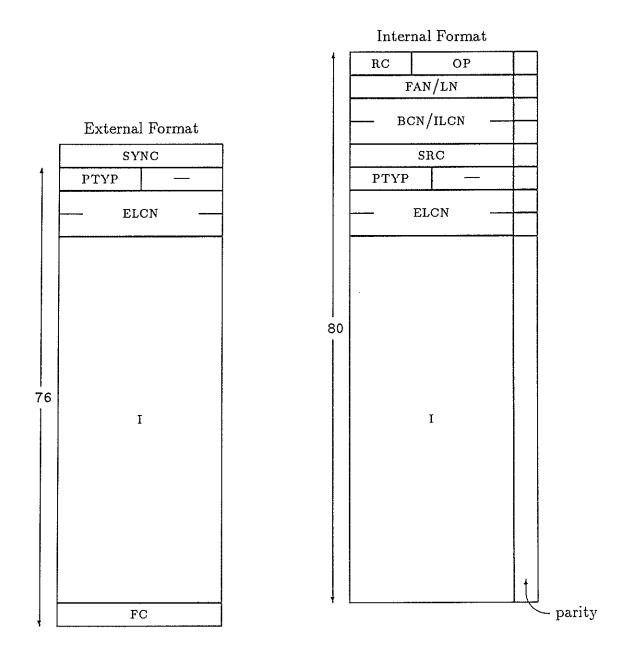

| 4.2  | Packet Formats                                                                                                                    | 45 |

| 4.3  | Packet Format Definitions                                                                                                         | 47 |

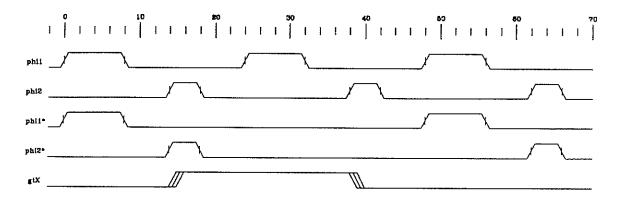

| 4.4  | Global Clock Signals                                                                                                              | 50 |

| 4.5  | Global Timing Relationships                                                                                                       | 50 |

| 4.6  | Block Diagram of Packet Switch Element Chip                                                                                       | 51 |

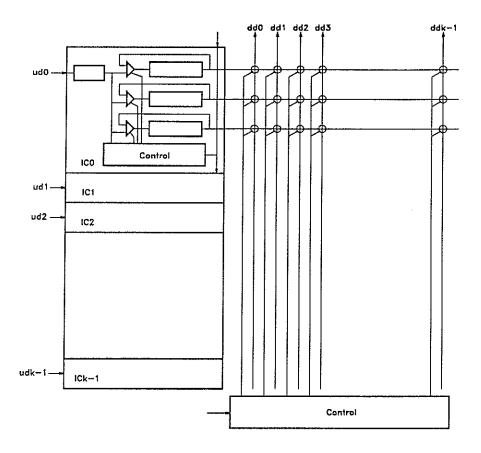

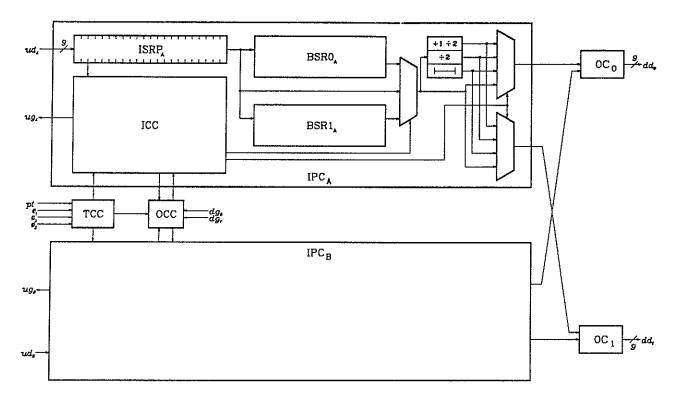

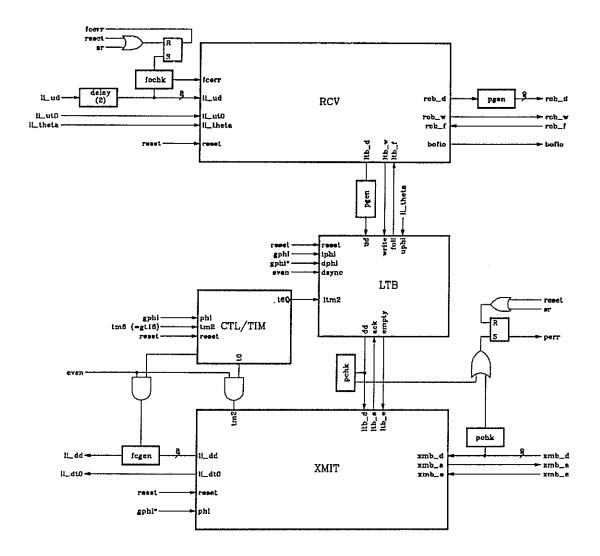

| 4.7  | Packet Processor Block Diagram                                                                                                    | 54 |

| 4.8  | Packet Processor Signals                                                                                                          | 55 |

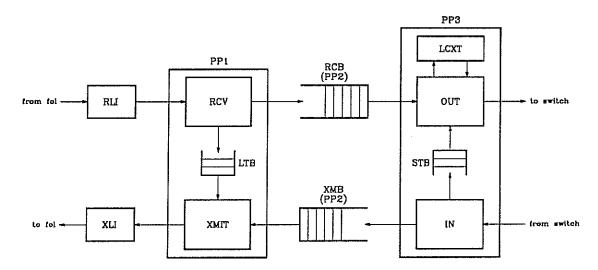

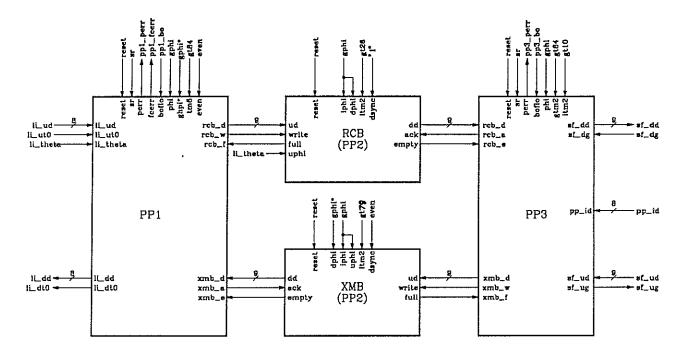

| 4.9  | PP1 Block Diagram                                                                                                                 | 58 |

| 4.10 | SSP Program for Receive Circuit                                                                                                   | 59 |

| 4.11 | PP3 Block Diagram                                                                                                                 | 60 |

| 4.12 | SSP Program for Out1 Circuit                                                                                                      | 61 |

| 4.13 | Block Diagram of Broadcast Translation Chip                                                                                       | 63 |

| 5.1  | Generic Synchronous Stream Processor                                                                                              | 66 |

| 5.2  | Unbuffered Switch Element                                                                                                         | 67 |

| 5.3  | Target SSP Architecture                                                                                                           | 67 |

| 5.4  | Structure of SSP Generator                                                                                                        | 69 |

| 5.5  | Specification of Unbuffered Switch Element                                                                                        | 70 |

| 5.6  | Intermediate Specification of Unbuffered Switch Element                                                                           | 71 |

| 5.7  | Packet Buffer                                                                                                                     | 73 |

| 5.8  | Control and Timing Example                                                                                                        | 75 |

| 5.9  | Example Test Vector Specification                                                                                                 | 77 |

| 5.10 | Example Output                                                                                                                    | 78 |

| 5.11 | Example Input to Timing Diagram Generator                                                                                         | 80 |

| 5.12 | Generated Timing Diagram                                                                                                          | 81 |

| 6.1  | Worst-Case Example for Rayward-Smith's Algorithm                                                                                  | 84 |

| 3.2  | Empirical Performance of Weighted Greedy Algorithm                                                                                | 85 |

| 7.1 | Compression Rate Comparison          | 91  |

|-----|--------------------------------------|-----|

| 8.1 | Connection Across a LAN              | 103 |

| 8.2 | Proposed Host Interface Architecture | 105 |

|  |   | • • |

|--|---|-----|

|  |   |     |

|  |   |     |

|  |   |     |

|  | • |     |

|  |   |     |

|  |   |     |

|  |   |     |

|  |   |     |

|  |   |     |

|  |   |     |

|  |   |     |

|  |   |     |

|  |   |     |

## 1. Summary of Progress

This report covers work performed from September 1987 through August 1988. This has been a productive year for us with substantial progress being made on a number of different fronts. In particular, we have developed new ideas on the design of practical switching systems that can support thousands of gigabit rate transmission links. We have made a significant generalization of the classical theory of nonblocking networks and have related it to the practical design of large scale packet switching systems. We continue to make good progress on our prototyping efforts with two new chip designs now complete and three others approaching completion; in support of this effort we have developed several design tools that represent significant contributions in their own right. We have studied a class of algorithms for video coding that yield substantially better compression than standard methods. And we have begun work on the problem of how to integrate high speed communication networks into a heterogeneous environment. Details of these and other efforts appear later in this report.

We continue to actively publish the results of our research. Papers have been presented at several conferences and revised versions have appeared or are scheduled to appear in leading journals; several theses have been completed; one patent has been awarded and an application for a patent on a hardware implementation of a buffer management system has been filed. (See Figures 1.1,1.2 for details.) Our work has generated a great deal of interest throughout the world, as evidenced by the many speaking invitations that have been received during the past year.

We summarize our progress in the following paragraphs. More detailed accounts of this work appear in later sections of the report.

#### Switch Architecture Studies

During the last year, we have been turning our attention to the architecture of packet switching systems that can support transmission link speeds in excess of a

#### Published Papers

"Fluid Flow Loading Analysis of Packet Switching Networks," by Jonathan Turner. Proceedings of the International Teletraffic Congress, June 1988. Also, submitted to Computer Networks and ISDN Systems.

"Distributed Protocols for Access Arbitration in Tree Structured Communication Channels," by Riccardo Melen and Jonathan Turner. *Proceedings of ICC 88*, June 1988. Also, submitted to *IEEE Transactions on Communications*.

"Design of a Broadcast Packet Switching Network," by Jonathan S. Turner, *IEEE Transactions on Communications*, June 1988.

"Broadcast Packet Switching Network," by Jonathan S. Turner, U.S. Patent #4,724,907, March 1988.

#### Invited Lectures

Bell Northern Research, Research Triangle Park, North Carolina (8/88)

Timeplex, Inc., Woodcliff Lake, NJ (8/88)

NEC, Tokyo, Japan (7/88)

NTT, Tokyo, Japan (7/88)

CSELT, Turin, Italy (5/88)

Italtel, Milan, Italy (5/88)

Digital Equipment Corporation, Littleton, MA (3/88)

University of California, Davis (2/88)

Tutorial on "Integrated Networks for Diverse Applications," at Globecom 88 and UCLA Extension Short Course (2/88).

Program committee for Computer Networking Symposium, April 1988. Guest editor for special issue of IEEE Journal on Selected Areas in Communications on broadband packet communications

Filed patent application on buffer management system for multipoint packet networks (3/88).

Figure 1.1: Publications and Related Activities

gigabit per second and which scale economically to very large configurations (thousands or tens of thousands of transmission links). We have concentrated on systems using CMOS integrated circuit technology with very wide internal data paths using a bit-sliced structure. We have quantified the complexity advantages of bit-sliced structures, developed practical solutions to the associated control problems, and developed a fairly detailed paper design of a system that can support up to 32 thousand fiber optic links operating at speeds of 1.6 Gb/s using current CMOS technology with 100 Mb/s clock speeds and 32 bit wide data paths. It appears

3

- "Design of Another VLSI Packet Switch Element," by Einir Valdimarsson, WUCS-88-23.

- "Improved Search Algorithms for Video Codecs," by Shabbir Khakoo, Washington University Electrical Engineering Department, MS thesis, June 1988.

- "A Circuit Generator for Synchronous Streams Processors," by George Robbert, Washington University Computer Science Department, MS thesis, May 1988.

- "Worst-case Performance of Rayward-Smith's Steiner Tree Heuristic," by Makoto Imase and Bernard Waxman, WUCS-88-13.

- "Towards a Framework for High Speed Communication in a Heterogeneous Networking Environment," by Guru Parulkar and Jonathan Turner, WUCS-88-7.

- "Buffer Management System," by Jonathan Turner, WUCS-88-6.

- "Probable Performance of Steiner Tree Algorithms," by Bernard Waxman, WUCS-88-4.

- "Nonblocking Multirate Networks," by Riccardo Melen and Jonathan Turner, WUCS-88-2.

- "Congestion Control in Fast Packet Networks," by Shahid Akhtar, Washington University Electrical Engineering Department, MS thesis, November 1987.

Figure 1.2: Theses and Technical Reports

likely that with near term technology improvements, this approach can be extended to handle speeds of 5-10 Gb/s. The details of this work appear in section 2.

Recently, we have also been exploring the problem of high speed switching systems for connectionless networks. While most researchers in the telecommunications community believe a connection-oriented approach is the most appropriate for high speed packet networks, there has not yet been a careful evaluation of the relative merits of connectionless and connection-oriented operation in a high speed networking environment. We are attempting to perform such an evaluation in order to give a clearer picture of the trade-offs involved. We have found that high speed connectionless networks are indeed possible, although they appear to be more costly to implement. The costs appear primarily in the packet processors that interface between the switch fabric and the transmission links. Connectionless networks require large buffers with priorities, link level and cross-switch flow control, plus content-addressable addressing tables. We have quantified the associated costs and estimate that a packet processor for a connectionless network might require about 20 chips to implement it (most being memory), as opposed to perhaps 4-5 for a connection-oriented network with comparable performance. While this is a clear advantage for connection-oriented networks, in some environments that cost may be less important than other factors.

## Nonblocking Multirate Networks

In the past year, we have generalized the classical theory of nonblocking networks to cover switching systems in which a switch's internal data paths are shared among different connections. This theory is applicable both to multirate circuit switching systems and packet switching fabrics in which all packets within a connection follow the same path. We have derived conditions under which the Clos, Cantor and Beneš networks are strictly or rearrangeably nonblocking. In particular, we have shown that for multirate traffic, an *i* stage Beneš network is strictly nonblocking if the internal data paths are *i* times faster than the external transmission links. This is an important practical result since with 32 port switch elements we can construct 1024 port switching fabrics in three stages. Given a 3:1 speed advantage, such a network becomes strictly nonblocking, which is potentially important in an environment where the distribution of connection bandwidths may vary widely. Even for smaller speed advantages, we expect excellent blocking behavior and are now beginning to study the blocking characteristics of such switches.

Recently, we have extended our work on nonblocking networks to networks supporting multipoint communication. We have shown that classical results due to Pippenger and Thompson can be extended to the multirate environment. We have also shown that a pair of i stage Beneš networks placed back-to-back forms a wide-sense nonblocking network for multipoint connections if we have a speed advantage of i. This configuration, together with the routing algorithm used to obtain nonblocking operation are both novel and we plan to recommend an appropriate patent filing.

## Prototype Switch Design

Work on a laboratory prototype of our switching system has been progressing well. Four integrated circuits implementing preliminary versions of the packet switch element and broadcast translation circuits have been received back from fabrication and have been tested. While we have had mixed results with these chips, we have learned a great deal from this process and have incorporated the lessons learned in the current versions, which have eight bit wide data paths and can support substantially higher clock speeds. The eight bit version of the packet switch element was submitted for fabrication at the end of July and is expected back from fabrication at the end of September. In addition to the wider data paths, this design incorporates architectural modifications in order to achieve higher clock speeds. We have also completed and fully simulated the design of a general purpose packet buffer, which will be used within the packet processor circuit. This chip will be submitted for fabrication in the near future. Three other chips are now in the

5

process of being designed. Two chips implementing parts of the packet processor and one implementing the broadcast translation chip are now in fabrication. These are being designed with the aid of a circuit generator written for that purpose. This is making the design of these chips much more rapid and less error prone than it would otherwise be.

### Design Tools

In support of our prototyping efforts we have developed several supporting design tools. The most ambitious is a circuit generation program that can be used to quickly layout a large class of common circuits required within the packet processor, broadcast translation circuit and other common subsystems. This program allows the user to specify a component of a system in a functional notation similar to a conventional programming language. It then translates this specification into a circuit satisfying the specification. This program has been written by George Robbert as part of his masters thesis research [80] and is now being applied to design of several of the major components within the packet processor and broadcast translation circuit.

We have also developed tools for generating packet buffers and lookup tables of different sizes and configurations. These tools will also allow us to more rapidly implement different components of our prototype system. Another tool that we are using extensively is a program to generate control and timing circuits from a high level specification. The circuits generate timing signals that can be qualified by a set of control inputs. This program was written originally for use within the circuit generator mentioned above but has been proven to be more generally useful and is now being used within the packet switch element and packet buffer chips. One of the more time-consuming parts of designing integrated circuits is generating the test vectors needed for logic simulation. We have developed an approach to generating these test vectors that allows us to generate both the input test vectors and expected output vectors using a special-purpose test vector generation program. We have developed such programs for both the packet switch element and packet buffers and have found them extremely helpful, allowing us to more thoroughly test these designs than we could have by manual methods.

## Connection Management

Connection management refers to the collection of algorithms used to create and maintain multipoint connections in a broadcast packet network. A multipoint connection is intended to be a flexible mechanism that can support a wide variety of different applications. In our last progress report, we described our approach

for specifying general multipoint connections, an architecture for a connection management software system and a set of protocols to implement that architecture.

We have completed development of an initial implementation of this connection management system in the form of a software simulation that allows us to configure an arbitrary network, then set up and modify multipoint connections in that network. Our implementation of multipoint connections includes a general transaction mechanism for sequencing concurrent changes to a connection. The software was implemented first on a VAX 11/750 and has since been ported to a Sun workstation environment; in this new context, we are developing a graphical user interface to allow simpler specification of network configurations as well as better observation and control of connections in progress. We expect this graphical interface to form the basis of some graphical network management tools that we hope to develop in the coming year. The simulation has proved very useful in testing out our ideas on multipoint connection management protocols. Based on experience obtained to date, we are now refining these protocols to make them simpler and more consistent at both the network access level and the internal network level. In the coming year, we will implement these refinements and add the lower level software required to control the protoype system under development.

## Multipoint Routing

The objective of the routing problem is to determine a set of network resources (primarily trunk bandwidth) sufficient to support communication among a specified set of users. Networks supporting multipoint communication channels of arbitrary bandwidth raise a variety of new issues for routing algorithms. We have primarily studied the formulation of the routing problem in which we seek to identify a shortest subtree within the network that contains the endpoints to be joined by a given connection and has sufficient bandwidth for the connection [102]. This formulation leads to a Steiner tree problem, which is known to be NP-complete.

We have experimentally evaluated several approximation algorithms for the Steiner tree problem. In the previous report, we described results for the so-called minimum-spanning tree heuristic (MST) and a dynamic greedy algorithm. In the last year, we have also evaluated an algorithm proposed by Rayward-Smith; we have recently completed an analysis of this algorithm's worst-case performance and shown that it is no better than that of MST [42]. On the other hand, our analysis has suggested a variation on Rayward-Smith that we expect may have better worst-case performance; also, its average case performance (based on exerimental evaluation) is somewhat better than MST, although both are very good. We have also evaluated a weighted version of the greedy algorithm for the dynamic version of the routing problem and have found that for appropriate choice of the weights,

7

this algorithm gives better average performance than the simple greedy algorithm; more significantly, the weighted algorithm is less subject to pathological behavior than the simple one.

We have recently begun work on a simulation environment that will permit us to evaluate our algorithms under more realistic conditions. In particular, this environment will allow us to simulate a network involving multiple connections and in which the routing algorithms are fully distributed. We expect to have performance results based on these simulations in time for the spring progress review.

#### Packet Video

Packetized transport of video signals raises a variety of important issues that we have been exploring. One major effect of packet transport on video coding is to eliminate the constraint of a constant bandwidth channel that currently drives most work in video coding. A variety of techniques including transform coding, motion compensation, differential coding and adaptive quantization are currently used to reduce the required bandwidth for video signals. Existing systems use buffering and variable rate coding, with the objective of achieving minimum image distortion for a given, fixed channel bandwidth. In the context of packet transport, we can exchange the objective function we seek to optimize with the constraint. That is, we code to achieve minimum bandwidth subject to a given constraint on distortion. This approach allows the bandwidth to vary across a wide range, achieving low average bandwidths and high picture quality.

Packetized transport also raises the issue of picture quality in the presence of packet loss. Common video coding methods rely heavily on state information that can become inconsistent when data is lost. The impact of lost packets can be reduced by interpolation schemes, in which a given block of information is split across multiple packets, allowing partial recovery of lost information. We expect that the use of such methods in combination with low rate transmission of complete state information can maintain high picture quality in the face of substantial packet loss rates and we are studying such methods to assess their potential.

Historically, video coding methods have been used primarily to produce moderate quality video for conference applications. With high speed packet networks it may also be advantageous to apply video coding methods to very high resolution signals; the objective becomes not bandwidth reduction but higher resolution. In the last year, we have studied hybrid coding algorithms employing transform coding, motion compensation and adaptive quantization. We have discovered that the commonly used search algorithms for motion compensation perform poorly in

the presence of moderate to high motion. While they work adequately in video conferencing situations (which typically involve very little motion), they do poorly in more general contexts. We have developed a new class of *signature-based* search algorithms, which compute a concise signature for each position in the search space and match the current sub-block against each signature. We have evaluated one set of algorithms in this class and have found it increases the effective compression by a factor of three or four during rapid motion [50].

### High Speed Internetworking

In our earlier work, we have concentrated on high speed networking in the context of a homogeneous environment. This is also typical of the approach taken by other groups working on high speed communication systems, but is in some ways unrealistic as it fails to explicitly take into account the diversity of existing and future networks, and the resulting need for inter-operation among separately administered and/or technologically dissimilar networks. In the last six months we have begun work on a framework for allowing diverse networks to inter-operate, while supporting both very high speed applications and multipoint communication [68]. This framework follows the general approach to interworking adopted in the ARPA internet protocols, but extends it in several respects. First it adds a connection-oriented transport service at the internet level, that can support applications with demanding performance requirements. Second it includes a more general addressing scheme, to allow interworking among diverse subnets. Third, it provides a framework for parametric description of subnet capabilities and connection requirements, allowing the routing of connections through subnets with appropriate capabilities in an application-independent fashion.

A connection-oriented transport service is important for several reasons. Perhaps the most obvious is performance. Connection-oriented systems separate the more complex control operations from data transfer, allowing simple and fast hardware implementations of the data transfer. Connection-oriented networks are also attractive because they allow the network to make explicit resource allocation decisions when connections are established, and this in turn makes it possible to offer far more predictable performance than in connectionless networks. Finally, connection-oriented networks offer more generally useful methods of multipoint communication than are possible in truly connectionless networks.

In our work we envision interoperation among a much wider class of networks than envisioned by the current internet model. In particular, we would like to support inter-operation between high speed packet networks, the current ARPA internet, X.25 networks and the public telephone network. Addressing is a key issue in allowing this level of diversity. We have proposed an addressing scheme that

9

would accommodate such diversity without requiring that the individual subnetworks abandon their native addressing mechanisms.

Given the variety of capabilities of the subnetworks included in an extended internet, we feel it is essential that the internet protocol include mechanisms for describing the capabilities of subnetworks, so that routing decisions can be guided by this information. For example, when selecting a route for a connection requiring a bandwidth of 1 Mb/s it is essential that the route not traverse subnetworks incapable of supporting that bandwidth. Similarly connections requiring low packet loss rates should not be routed through subnets that lose packets frequently.

#### Administrivia

In the past year, our research team has expanded with the addition of two new faculty members. We now have three faculty members involved in the project, one full-time staff person, one visiting research associate, ten graduate students and two part-time undergraduate students. Guru Parulkar joined the Computer Science Department in September 1987, after completing his PhD at the University of Delaware. Dr. Parulkar's thesis research focussed on the design and analysis of highly reliable local area networks based on flooding protocols. He is now concentrating on the problem internetworking of high speed packet networks. Andreas Bovopoulos is our most recent new faculty member, who has joined us from Columbia University where he studied the performance of flow control and routing protocols in networks. Riccardo Melen who was here as a visiting researcher in 1987 has returned to CSELT. His year here was a very productive one; he co-authored two papers with Dr. Turner [59,60] and co-invented a novel multipoint switching fabric. In March, Dr. Makoto Imase of NTT joined us for a one year visit. He has begun working with Buddy Waxman on the multipoint routing problem and their collaboration has already resulted in the solution of an important open problem in this area; a paper describing this work has been submitted for publication.

Among the students participating in the project, several changes have taken place. Four students have completed masters degrees. Shahid Akhtar graduated last fall and is now working at Bell Northern Research, in Research Triangle Park, NC, George Robbert graduated in May and is now with Hewlett-Packard in Fort Collins, CO, Shabbir Khakoo graduated in June and is working for AT&T Information Systems in Middletown, NJ and Mark Hunter who also graduated in June is working for McDonnell Douglas in St. Louis. All four of these students made strong contributions to the project and we wish them success in their future endeavors. We have several students who have joined the project in the past year. Tony Mazraani joined the project in January and has been working initially on several projects related to our prototype development effort. Gaurav Garg and

| Name               | Degree (exp. grad.) | Research Area                       |

|--------------------|---------------------|-------------------------------------|

| Neil Barrett       | MS (5/89)           | memory use in fast packet switching |

|                    |                     | systems                             |

| Einir Valdimarsson | MS (5/89)           | blocking probability in fast packet |

|                    |                     | networks                            |

| Bernard Waxman     | DSc (5/89)          | multipoint routing                  |

| Victor Griswold    | DSc (12/89)         | distributed program debugging       |

| Tony Mazraani      | MS (12/89)          | communication circuit design        |

| James Sterbenz     | DSc (12/89)         | interfacing computers to high speed |

|                    |                     | networks                            |

| Akira Arutaki      | DSc (5/90)          | switching architectures             |

| Haifeng Bi         | MS(5/90)            | communication circuit design        |

| Gaurav Garg        | MS(5/90)            | communication circuit design        |

| Michael Gaddis     | DSc (5/91)          | connection management               |

Figure 1.3: Current Graduate Students

| Name           | Degree | Date | Dept.                  | Thesis Title                             |

|----------------|--------|------|------------------------|------------------------------------------|

| Shabbir Khakoo | MS     | 8/88 | EE                     | Improved Search Algorithms for Video     |

|                |        |      |                        | Codecs                                   |

| Mark Hunter    | MS     | 8/88 | CS                     |                                          |

| George Robbert | MS     | 5/88 | CS                     | A Circuit Generator for Synchronous      |

|                |        | -    |                        | Streams Processors                       |

| Shahid Akhtar  | MS     | 1/88 | $\mathbf{E}\mathbf{E}$ | Congestion Control in Fast Packet        |

|                |        | •    |                        | Networks                                 |

| Rick Bubenik   | MS     | 8/85 | CS                     | Performance of a Broadcast Packet Switch |

Figure 1.4: Graduates

Haifeng Bi joined the project this summer and have also been involved in the prototype efforts. Mike Gaddis has just joined the project this fall and will probably be working in the area of connection management and internetwork protocols. We also have two part-time undergraduate students working on the project; Scott Johnson started last fall and has designed several graphics programs and has been assisting with some of the prototype design. Anne Reynolds started this summer and has been working on integrated circuit testing, among other things.

Our funding picture is fairly healthy. Bell Northern Research joined the project

11

in earlier this year, becoming our fourth industrial sponsor. Our support from the National Science Foundation has remained stable, but we will have to apply for new NSF funding this fall, as our current grant expires in June of next year. In addition to the direct grant support, NSF provides access to MOSIS, their silicon fabrication service which we are using heavily in our prototyping effort.

For administrative purposes, the ACS project operates within the Computer and Communications Research Center directed by Professor Mark Franklin. The Center has a central office suite housing professors Franklin and Turner, one technical staff person, plus seven graduate students, on the third floor of Bryan Hall, across from our main laboratory facility. This laboratory houses most of our computers, and a cluster of terminals and workstations for graduate student use and also serves as an informal meeting room. We also have additional office and laboratory space on the fifth floor of Bryan. Seven students and two additional staff members are located in this area. While our space situation is adequate, it is somewhat cramped and is likely to remain so for the next 18 months, while construction of a new 50,000 square foot research building is underway. When that building is completed, it will mean substantial new space for the Computer Science and Electrical Engineering Departments. We expect that at that point, we will move into the fourth floor of Bryan Hall, consolidating our group in one area and giving us additional space to work with.

The Center's base of equipment includes a VAX 750, a MicroVax II/GPX and a Sun workstation environment including a 3/280 file server, a 3/150 which will interface to our prototype switching system, and six 3/50 diskless workstations. In the last year a Sun 3/60 and a Sun 3/160 workstation have been added to that configuration. The 3/60 has supported our integrated circuit design efforts and the 3/160 will be used as the connection processor for our prototype switch. We have also doubled the disk storage on our file server to over one gigabyte, in response to the demands imposed by our VLSI design activities. The Center has also acquired a 64 processor NCUBE parallel computer, which Professor Franklin will be using to support his research in the area of design automation. We also anticipate its possible use in our project. In addition we have about fifteen conventional terminals, a PC/AT, another VLSI design station, several printers, and assorted lab equipment including a Tektronix logic analyzer and IC tester.

We have been generally successful in expanding the Center's space and facilities to meet our needs. As we are not planning substantial additional growth in the immediate future, we feel reasonably comfortable with the current situation. On the other hand, space shortages may develop in the next year as the Computer Science and Electrical Engineering departments continue to expand their faculties. While the construction of the new building should provide ample space in the longer term, there will be an intermediate period of limited space that will have

to be managed carefully.

## 2. Switch Architecture Studies

Faculty

Graduate Students

Jonathan Turner Akira Arutaki Neil Barrett Haifeng Bi Einir Valdimarsson

The architecture of high speed packet switching fabrics is of course central to the work of this project. While we are concentrating our efforts on a particular design [93], we continue to evaluate alternatives, in order to identify possible improvements. In the past year, we have begun an examination of systems that can support gigabit rate transmission using a bit-sliced internal architecture. Such systems represent a substantial improvement in performance and economy of implementation over current designs. We have also begun studies of global memory organization in large switching systems, queueing and blocking behavior in such systems and a study of switch design options for connectionless packet networks. Finally, we have extended an earlier simulation program used to assess our current design, by providing a graphical display that shows the status of the simulated network and provides interactive control of traffic sources and monitoring.

## 2.1. Bit-Sliced Switch Fabrics

Packet switching fabrics employing parallel data paths can be organized in a couple different ways. One possibility is the so-called word-serial approach, in which all the bits in a given data path pass through the same physical components. Another is the bit-sliced approach, in which the components making up the switch fabric are "sliced" so that each bit of the data path passes through a different set of components. An example illustrating these two approaches is shown in Figure 2.1. In the figure on the left, each box corresponds to a single integrated circuit, as do the rectangles on the right. Notice that each of these structures implements a 16

Figure 2.1: Comparison of Word-Serial and Bit-Sliced Organizations

Figure 2.2: Complexity of Word-Serial and Bit-Sliced Beneš Networks

port switching fabric with 8 bit wide data paths and that the integrated circuits in both cases require 32 signal leads. However, the word-serial structure requires 32 chips while the bit-sliced structure requires just eight. For large systems, this advantage of bit-sliced structures becomes even more dramatic. Figure 2.2 plots the chip count per port for Beneš networks with several choices of the data path width. N is the number of ports the switch fabric has, m is the data path width, m0 stands for word-serial and m0 for bit-sliced. Notice that for the bit-sliced organization, we can achieve data path widths of 32 at a cost of about five chips per port for switches with between 2,048 and 32,768 ports.

Of course, on the other side, the word-serial organization is somewhat simpler

Figure 2.3: Bit-Sliced Switch Element

to control. In the bit-sliced organization, each slice must make the same control decisions for the packets it receives. This can be done either by replicating the control information and sending it to each slice, or by having one slice decode the control information, make the appropriate decisions and communicate the results to the other slices. We examine the latter alternative and describe a practical design of a packet switching element that implements it.

Figure 2.3 illustrates a design of a bit-sliced switch element with k input and output ports and supporting m bit wide data paths. Typical values for k might be 16 or 32. Values for m might range from 8 to 64. Packets enter on one of the k upstream data lines at left, and the m bits of each packet are distributed across m separate data slices (DS). The packets exit from the switch element on the downstream data lines at the right. The switch element contains sufficient internal buffering to store several packets for each port and implements a simple hardware flow control mechanism to prevent packets from overflowing these buffers. We will describe three versions of the data slice; one with the buffering on the input side, another with the buffering on the output side and a third with shared buffering.

Figure 2.4: Data Slice with Input Buffering

The control slice shown at the bottom of the figure contains the circuitry used to control the operation of the switch element. It receives a set of downstream grant signals from the downstream neighbors and generates a corresponding set of upstream grant signals which are sent to the upstream neighbors. In general, a switch element asserts an upstream grant signal ug, if it is prepared to receive a packet on the upstream data lines ud. The packets flowing through the switch element are organized so that all the control information (in particular, the addressing information) passes through the first data slice DS<sub>0</sub>. This allows the control circuit to easily monitor the control information for all packets entering the data slice. Using this information, together with the downstream grants and the internal status of the switch elements, it makes control decisions and broadcasts those decisions to the data slices. In addition, the first bit of the packet in every data slice is a control bit indicating the presence or absence of a packet.

Figure 2.4 shows the organization of a chip implementing a data slice in which

the buffering is placed on the input side. The chip contains one Input Circuit (IC) for each input. Each IC contains several buffers, each able to store a complete bit slice of a packet. The buffers can be implemented as dynamic shift registers with a feedback path used to recirculate a packet if it is unable to proceed during a given cycle. The control circuit within the IC, keeps track of which buffers contain packets, detects the arrival of new packets and steers them to the first empty buffer. During one operational cycle, the control slice sends each IC one bit of control information for each buffer slot that the IC controls. If that bit is high, any stored packet in the buffer is recirculated, if it is low, any stored packet is transmitted from the buffer and the buffer becomes available to receive a new packet. The data slice also contains a crossbar matrix which provides access to the downstream data lines. During any given cycle, one crosspoint from each column of the crossbar is closed. The selected crosspoint is determined by a control register whose contents is determined by the control slice. Notice that the crossbar organization allows a packet to be sent to multiple outputs during a given cycle, permitting multipoint connections. Also notice that a packet that must be sent to several outputs need not be sent to all outputs simultaneously. If not all outputs are immediately available, it can be sent to the available outputs and recirculated in the input buffer until the remaining outputs become available.

The control slice is shown in Figure 2.5. This chip does not include any data storage; it merely monitors the bit slice containing the control information, makes the appropriate decisions and transmits these decisions to each of the data slices. The chip has an Input Control Circuit (ICC) for each of the k inputs. It also has a set of k downstream grants and k upstream grants. A downstream grant is asserted by one of a switch element's downstream neighbors if the neighbor is able to receive another packet. Similarly, the switch element asserts its upstream grant for each input that is able to receive another packet. The bit slice containing control information enters the chip on the upstream data leads. Each ICC shifts in the control information, latches it and decodes it. It is then stored in one of several control registers corresponding to the data buffers in which the packet data is stored. The control registers (CTL) independently contend for access to one or more outputs by sending their requests to an arbitration circuit.

The arbitration circuit consists of an array of arbitration elements (AE) together with an arbitration tree (AT) for each output. During a given operation cycle, a control register transmits to one row of arbitration elements, the range of outputs it requires access to; for example, it might request outputs 5–14. Each arbitration element in the row decodes the requested range and determines if its associated output has been selected. If so, it contends for the output by sending a request to the arbitration tree. Each arbitration tree is structured as a simple binary tree which accepts requests from the arbitration elements in one column of the

Figure 2.5: Control Slice

arbitration circuit and selects one of the contending AEs. If the downstream grant for that output indicates that the downstream neighbor is ready to receive a packet, the winner of the contention receives an acknowledgement indicating that it can transmit its packet. The output control circuits (OCC) at the root of the arbitration trees send the identities of the winning contenders to the data slices, where they are used to control the output crossbar. Each arbitration tree in fact makes its decision based on a priority sent to it from the arbitration elements. The high order field of the priority is the number of operation cycles that the contending packet has been waiting; this ensures that packets following the same path through the switch are served in first-in-first-out order and that no packet is kept waiting too long. It's of course also possible to implement more sophisticated priority schemes using the same basic mechanism. If a packet is to be transmitted to multiple outputs but does not receive access to all the required outputs on a particular cycle, the arbitration elements inform the control registers of that fact, and re-contend on the next cycle, continuing in this fashion until the packet has been transmitted to all required outputs. When the control circuit is informed that the packet has been transmitted to all outputs, it becomes available to receive a new packet.

Let  $C_d(k, m)$  be the complexity of a data slice with k inputs and designed for

an m bit wide network, and let  $C_c(k)$  be the complexity of the control slice. Then,

$$C_d(k, m) \approx kLBx_1/m + k^2x_2$$

(data slice)

$C_c(k, m) \approx kx_3 + k^2Bx_4$  (control slice)

where L is the total packet length in bits, B is the number of buffer slots per port,  $x_1$  is the cost per bit of memory,  $x_2$  is the cost per crosspoint,  $x_3$  is the cost for one IC plus one OC and  $x_4$  is the cost for one AE plus one AT node. Based on preliminary designs, we estimate  $x_1$  at eight transistors,  $x_2$  at  $8 + \log_2(1 + Bk)$  transistors,  $x_3$  at 1000 transistors and  $x_4$  at 200 transistors. If we select L = 4096, B = 3 we have for example,  $C_d(32,32) \approx 114,000$  transistors and  $C_c(32,32) \approx 646,000$  transistors. These estimates show that while the data slice is clearly feasible using 2 micron CMOS technology, the control slice is at best marginal for 2 micron technology. It could however be implemented in a 1 micron technology with no problem.

Another important parameter of the design is the amount of control information that must be sent from the control slice to the data slices during each packet cycle. If we let I(k, B) denote the amount of information required for a switch element with k ports and B buffers per port then

$$I(k,B) = kB + k\lceil \log_2(1+kB)\rceil$$

The time needed to transmit the control information to the data slices puts a lower bound on the length of a packet cycle. If r pins are used to carry the control information, then the packet length should be at least mI(k,B)/r. For example, if k=m=32, B=3 and r=8, we require a packet with at least 1280 bits. A more realistic packet length is probably about twice this. For 64 bit wide data paths, the required packet length would of course double.

Figure 2.6 shows an alternative design for a data slice in which most of the buffering is placed on the output side. A single slot buffer is required for each input to prevent packets from being lost. The control information for the ICs, OCs and crossbars is received from the control slice. The circuit complexity of the data slice is approximately equal to that for the input buffering case. The control slice is perhaps a little more complicated as it requires a more sophisticated output arbitration tree. The amount of information required to control the data slice is given by

$$2k + k(B-1)\lceil \log_2(k+1) \rceil$$

In most cases, this is substantially higher than that required for the input buffered data sliceed data slice.

Figure 2.7 shows a third design in which the buffering is shared equally among the inputs and outputs. In this design, the packets enter at the top left, pass

Figure 2.6: Data Slice with Output Buffering

through an input crossbar to a set of buffers, before being sent through an output crossbar to the downstream data lines. The buffers and output crossbar are controlled in exactly the same way as for input buffering. The input crossbar requires no external control information. In this design, the complexity of the data slice is approximately

$$kLBx_1/m + k^2(x_2 + x_5)$$

where  $x_5$  is the complexity of an input crosspoint. If we estimate this at 50 transistors, the complexity of a switch element with k=m=32, L=4096 and B=3 is approximately 165,000 transistors. The control slice is almost identical to the input buffering case, as is the amount of information required to control the data slice.

Based on this design we have estimated that a packet switching system com-

Figure 2.7: Data Slice with Shared Buffering

prising a Beneš network with 32 bit wide data paths and supporting 4096 fiber optic data links would require about twelve standard equipment cabinets. Another four cabinets would be required for the link interfaces and packet processors. If such a system was operated with a clock rate of 100 Mb/s (an achievable rate even with CMOS), its internal data paths would operate at an effective rate of 3.2 Gb/s, which is sufficient to support external link speeds of 1.6 Gb/s. This represents an order of magnitude improvement over the speeds being achieved by current research prototypes. While there are limits to how far such techniques can go, it appears likely that at least another factor of four is possible through a combination of higher clock rates and greater parallelism.

## 2.2. Switches for Connectionless Networks

Most work on high speed packet switching has centered on systems that transfer data using logical connections rather than datagrams. There are several good reasons to prefer connection-oriented networks. First and most important, in a

connection-oriented network it is possible to allocate resources to individual applications, allowing the network to provide a predictable performance level to an application even when the network is heavily loaded. Because the network has knowledge of the resource requirements of user applications, it can block new traffic when it lacks the resources to support it. In a connectionless network, when the network becomes overloaded all users experience degraded performance. A second advantage of connection-oriented networks is that they are simpler to implement, requiring only the simplest routing algorithms, no link level flow control and relatively modest buffer requirements. Connection-oriented networks also permit the implementation of general multipoint communication, something that is possible in connectionless networks only by introducing the idea of a multicast address, which is in fact nothing more or less than a connection by another name.

On the other hand, connectionless networks have their attractive points as well. First, because there is no need to establish a connection, the use of connectionless networks is much simpler. In particular, for many applications, determination of resource requirements in advance is difficult or impossible. Since connectionless networks don't require such a determination they are easier to use. Also, the design of network equipment is simplified somewhat by the elimination of connection management. Second, connectionless networks are inherently more robust than connection-oriented networks; because they lack the state information that defines connections, they can recover from failures of switches and transmission links without perceptible impact on users. Third, connectionless networks can distribute traffic more evenly, since packets are individually routed; of course this has the drawback that packets can be delivered in the wrong order.

In this section, we examine the possibility of implementing switching systems for high speed connectionless networks. Our objective is to get an understanding of the complexity of such systems so that we can make comparisons between them and systems for connection-oriented networks. We conclude that while high speed switching is connectionless networks is more complex in some respects and offers less predictable performance when heavily loaded, it is possible to build systems that match the raw speed of connection-oriented networks. Such systems may merit consideration in environments where the ease of use and inherent reliability of connectionless networks offset their drawbacks.

We start with the issue of buffering and flow control in connectionless networks. Because the flow of traffic in connectionless networks is unpredictable, flow control appears to be required to prevent excessive loss of packets during local overloads and to help steer traffic around congested areas. Flow control may be required both across links and between the input and output ports of switching systems.

Flow control across transmission links can be readily implemented in hardware so long as it is not coupled to error recovery as in conventional window-based

Figure 2.8: Simple Flow Control Across a Link

protocols. Figure 2.8 illustrates the basic idea. At the receiving end of the link is a buffer whose level is monitored at all times. When the level is above a threshold, a flow control bit is set in all packets sent in the reverse direction. When the level is below the threshold level, the flow control bit is cleared. When there are no user packets to send in the reverse direction, dummy packets are sent with the flow control information. In order to prevent buffer overflow and realize maximum link throughput, the receiving buffer should have a storage capacity that is four times that of the transmission link and the threshold should be set at the half full level. The storage capacity of a transmission link is given by RL/c where R is the rate bits are transmitted on the link, L is the length of the link and c is the propagation speed of the signal, which is approximately 200,000 km/s for optical fiber. So for example, a 1000 km link operating at a speed of 100 Mb/s has a bit capacity of 0.5 Mb, requiring a buffer size of 2 Mb. This goes to 20 Mb for a link operating at 1 Gb/s. Even a 20 Mb buffer could be reasonably constructed using video RAMS, or similarly organized memories. Commercial video RAM chips are available in sizes up to 1 Mb, so the 20 Mb buffer would require 20 memory chips meaning that a packet processor containing such a buffer would probably consume a large fraction of a circuit board and cost one to two thousand dollars. While this is higher than comparable costs in connection-oriented networks, it may not be unreasonable in certain environments. Also note that for short links (say 10 km), much smaller buffers could be used, allowing inexpensive packet processors to be used in access links where the cost sensitivity is highest.

Figure 2.9 illustrates how flow control can be performed across a switch using a control ring that contains one bit of flow control information for each outgoing link. In this example, the switching fabric is assumed to be a buffered Beneš network with flow control between switch elements. The outgoing packet processors (PP) have buffers capable of holding say, 20 packets and when the buffer occupancy exceeds a threshold, the PP sets the flow control bit. This prevents the input PPs from sending more packets to the overloaded PP, although packets within the switch fabric will still reach it. The use of flow control within the switch ensures that packets are not lost. The flow control ring limits the size of the switch somewhat. Note however that the ring need not make a full circulation on

Figure 2.9: Flow Control Across a Switch

each cycle, and it can be made several bits wide if necessary. Switch sizes as large as 256 ports can be easily accommodated if the packet cycle is at least 64 clock ticks long.

We next consider the issue of routing packets in a datagram network. To distribute traffic through the network, we need some method for selecting alternate routes. However, the need for high speed routing translation means that only fairly simple choices can be made on a per packet basis. We present a possible approach that is well-suited to hardware implementation, and which together with the flow control mechanisms described above could be effective. We assume that each switch has a Control Processor (CP) that manages the overall operation of the switch. In particular, the CP maintains a graph model of the entire network including all switches, the capacities of interconnecting trunk groups and possibly

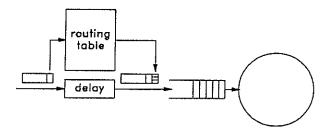

Figure 2.10: Datagram Address Translation

Figure 2.11: Content Addressable Memory Cells

the addresses of all terminals associated with each switch. Using this, the CP can compute for each destination, an ordered list of links that can be used to reach that destination.

Each PP has an address translation table that it can use to translate a network address to a list of links that can be used to reach that address. The content of these tables is determined by the CP. The address translation is done before a packet is placed in an incoming PP's buffer, as shown in Figure 2.10. When the packet reaches the front of the buffer, one of the outgoing links is selected, based on the flow control information communicated through the control ring. That is, if the first outgoing link in a packet's list has not set its flow control bit, the packet is sent to it. If it has set its bit, the second link in the list is tried, and so forth.

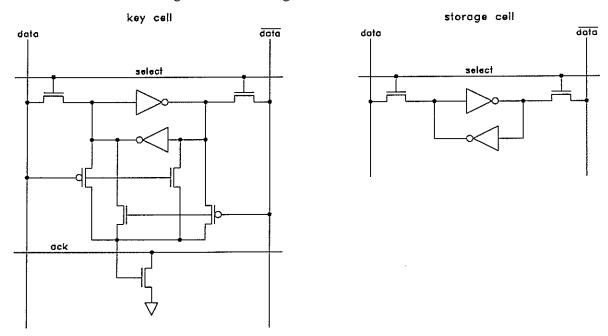

There are two obvious approaches to address translation. One is to use a hierarchical address based on physical location that can be translated in several steps. A simple version of this is a two step hierarchy in which the first part of the address identifies the access switch for a particular destination and the second part gives a port number on that switch. In a network with a few thousand switches, the required address translation tables would be small enough to fit readily in a single integrated circuit. Another possibility is the use of a large flat address space. If the address space is very large (say 32 bits), it is impractical to store the translation information for every possible address. We can however reasonably store in each PP the translation information for a few thousand addresses using a content addressable memory (CAM). Figure 2.11 shows a storage cell and a key cell for a CAM. The storage cell is a conventional six transistor memory cell. The key cell contains additional circuitry that allows it to compare the stored bit with the information on the data lines and signal a match using a common precharged acknowledgement line. Notice that the key cell requires 11 transistors meaning that a CAM with 1024 words including a 32 bit key and 32 bits of data would require about 550 thousand transistors, for the main memory array. In one micron CMOS this can be easily fit on a single integrated circuit.

Because a CAM-based address translator cannot store information about all network addresses, we require a mechanism for handling packets for which translation information is not present in the CAM. One approach is to send such packets to the CP. So long as these exceptions occur infrequently, the CP can route them and at the same time update the CAM of the PP where the packet arrived, so that subsequent packets to that destination can be handled by the PP. This of course raises the issue of what happens when a PP's CAM is full. In this case, the CP has to discard one of the entries in the CAM in order to make room for a new one. To determine which entry to discard, the CP needs a way of determining which entries have been used recently. A possible solution to this problem is to supplement each CAM word with a mark bit, which is set by the CAM whenever that word is accessed. The CP can periodically (say every ten seconds) poll the status of all mark bits in the CAM via a control packet and simultaneously clear the mark bits. Using this information it can easily track the entries that have been most recently used.

The use of flow control, large buffers and dynamic packet routing all imply that delays can be large and vary widely when the network is heavily loaded. This in turn suggests that priorities may be required to ensure satisfactory performance for time-critical applications. This is particularly important in the large buffers on the input side of the packet switches, which could have to store as many as several thousand packets (20 Mb buffer with 5000 bit packets). A priority queue controller for such a buffer can be implemented using a circuit similar to the buffer controller described in [99]. We estimate that such a controller would require about 300–500

transistors per packet stored, making a single chip implementation of a controller for a 4096 packet buffer feasible.

# 3. Nonblocking Multirate Networks

Faculty Research Associate Jonathan Turner Riccardo Melen

In this section we discuss a generalization of the classical theory of nonblocking switching networks to model communication systems designed to carry connections with a multiplicity of data rates. The theory of nonblocking networks was motivated by the problem of designing telephone switching systems capable of connecting any pair of idle terminals, under arbitrary traffic conditions. We extend the classical model to switching systems in which the internal data paths carry multiplexed traffic in which individual user channels consume an arbitrary fraction of the bandwidth, subject only to the constraint that the total traffic not exceed the capacity of the data path. Our model is applicable in particular to packet switched fabrics in which all packets in a given connection follow the same path through the switching system. More details of this work may be found in [60].

We start with some definitions. We define a network as a directed graph G = (V, E) with a set of distinguished input nodes I and output nodes O, where each input node has one outgoing edge and no incoming edge and each output node has one incoming edge and no outgoing edge. We consider only networks that can be divided into a sequence of stages. We say that the input ports are in stage 0 and for i > 0, a node v is in stage i if for all links (u, v), u is in stage i - 1. A link (u, v) is said to be in stage i if u is in stage i. In the networks we consider, all output ports are in the same stage, and no other nodes are in this stage. When we refer to a k stage network, we generally neglect the stages containing the input and output ports. We refer to a network with n input ports and m output ports as an (n, m)-network. We let  $X_{n,m}$  denote the network consisting of n input nodes, m output nodes and a single internal node. In this network model, nodes correspond to the hardware devices that perform the actual switching functions and the links to the interconnecting data paths. This differs from the graph model traditionally

used in the theory of switching networks, which can be viewed as a dual to our model.

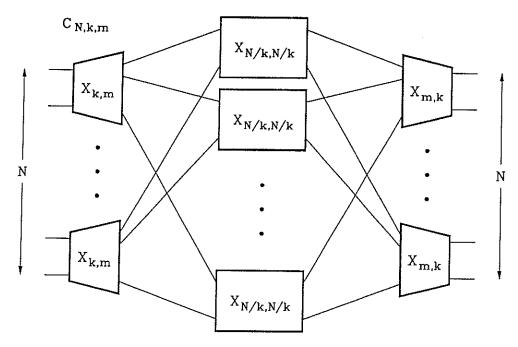

When describing particular networks we will find it convenient to use a composition operation. We denote the composition of two networks  $Y_1$  and  $Y_2$  by  $Y_1 \circ Y_2$ . The composition operation yields a new network consisting of one or more copies of  $Y_1$  connected to one or more copies of  $Y_2$ , with a link joining each pair of subnetworks. More precisely, if  $Y_1$  has  $n_1$  outputs and  $Y_2$  has  $n_2$  inputs, then  $Y_1 \circ Y_2$  is formed by taking  $n_2$  copies of  $Y_1$  numbered from 0 to  $n_2 - 1$  followed by  $n_1$  copies of  $Y_2$ , numbered from 0 to  $n_1 - 1$ . Then, for  $0 \le i \le n_1 - 1$ ,  $0 \le j \le n_2 - 1$ , we join  $Y_1(i)$  to  $Y_2(j)$  using a link connecting output port j of  $Y_1(i)$  to input port i of  $Y_2(j)$ . Next, we remove the former input and output nodes that are now internal, identifying the edges incident to them and finally, we renumber the input and output nodes of the network as follows; if u was input port i of  $Y_1(j)$ , it becomes input  $jn_1 + i$  in the new network; similarly if v was output port i of  $Y_2(j)$ , it becomes output  $jn_2 + i$ . We also allow composition of more than two networks; the composition  $Y_1 \circ Y_2 \circ Y_3$  is obtained by letting  $Z_1 = Y_1 \circ Y_2$  and  $Z_2 = Y_2 \circ Y_3$ , then identifying the copies of  $Y_2$  in  $Z_1$  and  $Z_2$ . This requires of course that the number of copies of  $Y_2$  generated by the two initial compositions be the same. Note this is not the same as  $(Y_1 \circ Y_2) \circ Y_3$ .

A connection in a network is a triple  $(x, y, \omega)$  where  $x \in I$ ,  $y \in O$  and  $0 \le \omega \le 1$ . We refer to  $\omega$  as the weight of the connection and it represents the bandwidth required by the connection. A route is a path joining an input node to an output node, with intermediate nodes in  $V - (I \cup O)$ , together with a weight. A route r realizes a connection  $(x, y, \omega)$ , if x and y are the input and output nodes joined by r and the weight of r equals  $\omega$ .

A set of connections is said to be compatible if for all nodes  $x \in I \cup O$ , the sum of the weights of all connections involving x is  $\leq 1$ . A configuration for a network G is a set of routes. The weight on an edge in a particular configuration is just the sum of the weights of all routes including that edge. A configuration is compatible if for all edges  $(u, v) \in E$ , the weight on (u, v) is  $\leq 1$ . A set of connections is said to be realizable if there is a compatible configuration that realizes that set of connections. If we are attempting to add a connection  $(x, y, \omega)$  to an existing configuration, we say that a node u is accessible from x if there is path from x to u, all of whose edges have a weight of no more than  $1 - \omega$ .

A network is said to be rearrangeably nonblocking (or simply rearrangeable) if for every set C of compatible connections, there exists a compatible configuration that realizes C. A network is strictly nonblocking if for every compatible configuration R, realizing a set of connections C, and every connection c compatible with C, there exists a route r that realizes c and is compatible with R. For strictly nonblocking networks, one can choose routes arbitrarily and always be guaranteed that any

31

new connections can be satisfied without rearrangements. We say that a network is wide-sense nonblocking if there exists a routing algorithm, for which the network never blocks; that is, if we use the routing algorithm to select routes for each new connection request, it is always possible to realize a new connection by adding a route to the current configuration.