## Washington University in St. Louis Washington University Open Scholarship

All Computer Science and Engineering Research

**Computer Science and Engineering**

Report Number: WUCSE-2006-50

2006-01-01

## Auto-Pipe and the X Language: A Toolset and Language for the Simulation, Analysis, and Synthesis of Heterogeneous Pipelined Architectures, Master's Thesis, August 2006

Eric J. Tyson

Pipelining an algorithmis a popularmethod of increasing the performance of many computationintensive applications. Often, one wants to form pipelines composed mostly of commonly used simple building blocks such as DSP components, simple math operations, encryption, or pattern matching stages. Additionally, one may desire to map these processing tasks to different computational resources based on their relative performance attributes (e.g., DSP operations on an FPGA). Auto-Pipe is composed of the X Language, a flexible interface language that aids the description of complex dataflow topologies (including pipelines); X-Com, a compiler for the X Language; X-Sim, a tool for modeling pipelined architectures... **Read complete abstract on page** 2.

Follow this and additional works at: https://openscholarship.wustl.edu/cse\_research Part of the Computer Engineering Commons, and the Computer Sciences Commons

#### **Recommended Citation**

Tyson, Eric J., "Auto-Pipe and the X Language: A Toolset and Language for the Simulation, Analysis, and Synthesis of Heterogeneous Pipelined Architectures, Master's Thesis, August 2006" Report Number: WUCSE-2006-50 (2006). *All Computer Science and Engineering Research*. https://openscholarship.wustl.edu/cse\_research/201

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160.

This technical report is available at Washington University Open Scholarship: https://openscholarship.wustl.edu/ cse\_research/201

## Auto-Pipe and the X Language: A Toolset and Language for the Simulation, Analysis, and Synthesis of Heterogeneous Pipelined Architectures, Master's Thesis, August 2006

Eric J. Tyson

#### **Complete Abstract:**

Pipelining an algorithmis a popularmethod of increasing the performance of many computation-intensive applications. Often, one wants to form pipelines composed mostly of commonly used simple building blocks such as DSP components, simple math operations, encryption, or pattern matching stages. Additionally, one may desire to map these processing tasks to different computational resources based on their relative performance attributes (e.g., DSP operations on an FPGA). Auto-Pipe is composed of the X Language, a flexible interface language that aids the description of complex dataflow topologies (including pipelines); X-Com, a compiler for the X Language; X-Sim, a tool for modeling pipelined architectures based on measured, simulated, or derived task and communications behavior; X-Opt, a tool to optimize X applications under various metrics; and X-Dep, a tool for the automatic deployment of X-Com- or X-Sim-generated applications to real or simulated devices. This thesis presents an overview of the Auto-Pipe system, the design and use of the X Language, and an implementation of X-Com. Applications developed using the X Language are presented which demonstrate the effectiveness of describing algorithms using X, and the effectiveness of the Auto-Pipe development flow in analyzing and improving the performance of an application.

Department of Computer Science & Engineering

2006-50

# Auto-Pipe and the X Language: A Toolset and Language for the Simulation, Analysis, and Synthesis of Heterogeneous Pipelined Architectures, Master's Thesis, August 2006

Authors: Eric J. Tyson

Corresponding Author: etyson@wustl.edu

Abstract: Pipelining an algorithmis a popularmethod of increasing the performance of many computation-intensive applications. Often, one wants to form pipelines composed mostly of commonly used simple building blocks such as DSP components, simple math operations, encryption, or pattern matching stages. Additionally, one may desire to map these processing tasks to different computational resources based on their relative performance attributes (e.g., DSP operations on an FPGA).

Auto-Pipe is composed of the X Language, a flexible interface language that aids the description of complex dataflow topologies (including pipelines); X-Com, a compiler for the X Language; X-Sim, a tool for modeling pipelined architectures based on measured, simulated, or derived task and communications behavior; X-Opt, a tool to optimize X applications under various metrics; and X-Dep, a tool for the automatic deployment of X-Com-or X-Sim-generated applications to real or simulated devices.

This thesis presents an overview of the Auto-Pipe system, the design and use of the X Language, and an implementation of X-Com. Applications developed using the X Language are presented which demonstrate the

Type of Report: Other

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160

## WASHINGTON UNIVERSITY THE HENRY EDWIN SEVER GRADUATE SCHOOL DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

## AUTO-PIPE AND THE X LANGUAGE:

A TOOLSET AND LANGUAGE FOR THE SIMULATION, ANALYSIS, AND SYNTHESIS OF HETEROGENEOUS PIPELINED ARCHITECTURES

by

Eric J. Tyson

Prepared under the direction of Professor Mark A. Franklin

A thesis presented to the Henry Edwin Sever Graduate School of Washington University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

August 2006

Saint Louis, Missouri

## WASHINGTON UNIVERSITY THE HENRY EDWIN SEVER GRADUATE SCHOOL DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

#### ABSTRACT

## AUTO-PIPE AND THE X LANGUAGE: A TOOLSET AND LANGUAGE FOR THE SIMULATION, ANALYSIS, AND SYNTHESIS OF HETEROGENEOUS PIPELINED ARCHITECTURES

by

Eric J. Tyson

ADVISOR: Professor Mark A. Franklin

August 2006

Saint Louis, Missouri

Pipelining an algorithm is a popular method of increasing the performance of many computation-intensive applications. Often, one wants to form pipelines composed mostly of commonly used simple building blocks such as DSP components, simple math operations, encryption, or pattern matching stages. Additionally, one may desire to map these processing tasks to different computational resources based on their relative performance attributes (e.g., DSP operations on an FPGA).

Auto-Pipe is composed of the X Language, a flexible interface language that aids the description of complex dataflow topologies (including pipelines); X-Com, a compiler for the X Language; X-Sim, a tool for modeling pipelined architectures based on measured, simulated, or derived task and communications behavior; X-Opt, a tool to optimize X applications under various metrics; and X-Dep, a tool for the automatic deployment of X-Com- or X-Sim-generated applications to real or simulated devices.

This thesis presents an overview of the Auto-Pipe system, the design and use of the X Language, and an implementation of X-Com. Applications developed using the X Language are presented which demonstrate the effectiveness of describing algorithms using X, and the effectiveness of the Auto-Pipe development flow in analyzing and improving the performance of an application.

# Contents

| st of [ | Tables                                                                   |                                                                                                                                                                                                                                                                          | iv                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| st of ] | Figures                                                                  | 5                                                                                                                                                                                                                                                                        | v                                                                                                                                                                                                                                                                                                                                                                                                                        |

| knov    | wledgn                                                                   | nents                                                                                                                                                                                                                                                                    | vii                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Intro   | oductio                                                                  | on                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.1     | Backg                                                                    | ground                                                                                                                                                                                                                                                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.2     | Motiv                                                                    | vation                                                                                                                                                                                                                                                                   | 8                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.3     | The A                                                                    | uto-Pipe System                                                                                                                                                                                                                                                          | 9                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | 1.3.1                                                                    | The X Language and Compiler                                                                                                                                                                                                                                              | 10                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 1.3.2                                                                    | The X-Sim Simulation Environment                                                                                                                                                                                                                                         | 11                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 1.3.3                                                                    | The X-Opt System Performance Optimizer                                                                                                                                                                                                                                   | 12                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 1.3.4                                                                    | Auto-Pipe Development Flows                                                                                                                                                                                                                                              | 13                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.4     | Relate                                                                   | ed Work                                                                                                                                                                                                                                                                  | 16                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.5     | Overv                                                                    | view of Thesis                                                                                                                                                                                                                                                           | 22                                                                                                                                                                                                                                                                                                                                                                                                                       |

| The     | X Lang                                                                   | guage                                                                                                                                                                                                                                                                    | 24                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.1     | Goals                                                                    |                                                                                                                                                                                                                                                                          | 24                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.2     | Tutori                                                                   | ial Walkthrough                                                                                                                                                                                                                                                          | 27                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 2.2.1                                                                    | A simple algorithm                                                                                                                                                                                                                                                       | 28                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 2.2.2                                                                    | Another algorithm                                                                                                                                                                                                                                                        | 31                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 2.2.3                                                                    | Platforms, Linktypes, and Resources                                                                                                                                                                                                                                      | 34                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 2.2.4                                                                    | Mapping                                                                                                                                                                                                                                                                  | 39                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.3     | Termi                                                                    | nology                                                                                                                                                                                                                                                                   | 43                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.4     | Langu                                                                    | Lage Specification                                                                                                                                                                                                                                                       | 45                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 2.4.1                                                                    | Lexical conventions                                                                                                                                                                                                                                                      | 46                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 2.4.2                                                                    | Pre-processing directives                                                                                                                                                                                                                                                | 47                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 2.4.3                                                                    | Statements                                                                                                                                                                                                                                                               | 47                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |                                                                          |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | 2.4.4                                                                    | Data type syntax                                                                                                                                                                                                                                                         | 48                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | 2.4.4<br>2.4.5                                                           |                                                                                                                                                                                                                                                                          | 48<br>49                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | st of 1<br>cknow<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>The<br>2.1<br>2.2 | st of Figures<br>knowledge<br>Introductio<br>1.1 Backg<br>1.2 Motiv<br>1.3 The A<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4<br>1.4 Relate<br>1.5 Overv<br>The X Lang<br>2.1 Goals<br>2.2 Tutor:<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.3 Termi<br>2.4 Langu<br>2.4.1<br>2.4.2 | Introduction         1.1       Background         1.2       Motivation         1.3       The Auto-Pipe System         1.3.1       The X Language and Compiler         1.3.2       The X-Sim Simulation Environment         1.3.3       The X-Opt System Performance Optimizer         1.3.4       Auto-Pipe Development Flows         1.4       Related Work         1.5       Overview of Thesis         The X Language |

|    |        | 2.4.7    | Edge Syntax                                                                                                                       |

|----|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------|

|    |        | 2.4.8    | Generation syntax                                                                                                                 |

|    |        | 2.4.9    | Behavior                                                                                                                          |

| 3  | Usi    | ng the 2 | X Compiler                                                                                                                        |

|    | 3.1    | Devel    | $ opment Roles \dots \dots$ |

|    | 3.2    | Х Арр    | plication Authoring                                                                                                               |

|    |        | 3.2.1    | Deployment                                                                                                                        |

|    |        | 3.2.2    | Usage                                                                                                                             |

|    |        | 3.2.3    | Support Tools                                                                                                                     |

|    | 3.3    | Block    | Implementation Programming    63                                                                                                  |

|    |        | 3.3.1    | The C Code Generator and API                                                                                                      |

|    |        | 3.3.2    | The HDL Code Generator and API                                                                                                    |

|    | 3.4    | X Sys    | tem Extension                                                                                                                     |

|    |        | 3.4.1    | X-Com Function                                                                                                                    |

|    |        | 3.4.2    | The C Code Generator                                                                                                              |

|    |        | 3.4.3    | Adding Resource Types    76                                                                                                       |

| 4  | Sam    | ple Ap   | oplications                                                                                                                       |

|    | 4.1    | Triple   | DES Encryption                                                                                                                    |

|    |        | 4.1.1    | Design                                                                                                                            |

|    |        | 4.1.2    | Performance                                                                                                                       |

|    | 4.2    | Signa    | l Cleaner                                                                                                                         |

|    |        | 4.2.1    | Design                                                                                                                            |

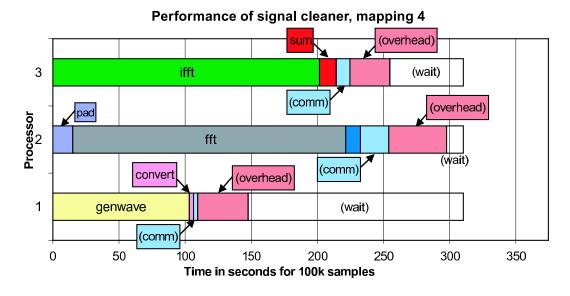

|    |        | 4.2.2    | Performance                                                                                                                       |

|    | 4.3    | Gamn     | na Ray Event Parametrization                                                                                                      |

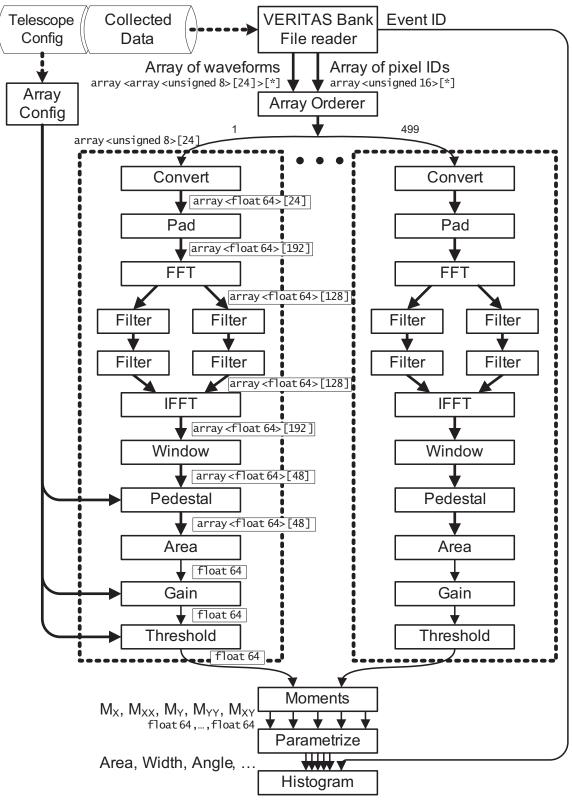

|    |        | 4.3.1    | Design                                                                                                                            |

|    |        | 4.3.2    | Performance                                                                                                                       |

|    |        | 4.3.3    | Further performance analysis                                                                                                      |

| 5  | Sun    | nmary    |                                                                                                                                   |

|    | 5.1    | 5        | usions                                                                                                                            |

|    | 5.2    |          | ibutions and Implementation Status                                                                                                |

|    | 5.3    |          | e Work                                                                                                                            |

| Re | eferei | nces .   |                                                                                                                                   |

| 17 | ta     |          |                                                                                                                                   |

| v  | а      | • • • •  |                                                                                                                                   |

# **List of Tables**

| 1.1 | Overview of related projects                                      | 20  |

|-----|-------------------------------------------------------------------|-----|

| 3.1 | C API Data Types                                                  | 68  |

| 3.2 | HDL API Data Types                                                | 71  |

| 4.1 | Results of mapping 1                                              | 88  |

| 4.2 | Estimated contributions of non-ideal scaling effects in mapping 4 | 108 |

# **List of Figures**

| 1.1  | An example application dataflow                                           | 3  |

|------|---------------------------------------------------------------------------|----|

| 1.2  | An example feed-forward pipeline                                          | 4  |

| 1.3  | An example processing architecture                                        | 5  |

| 1.4  | An example of mapping the algorithm to the processing architecture        | 6  |

| 1.5  | Another example of mapping the algorithm to the processing architecture . | 7  |

| 1.6  | X-Opt Flow Chart                                                          | 12 |

| 1.7  | X-Com algorithm design flow                                               | 13 |

| 1.8  | X-Com flow                                                                | 14 |

| 1.9  | X-Com plus X-Sim flow                                                     | 15 |

| 1.10 | X-Com plus X-Sim plus X-Opt flow                                          | 16 |

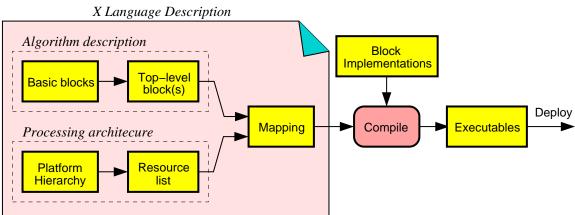

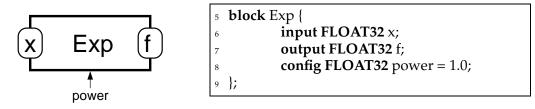

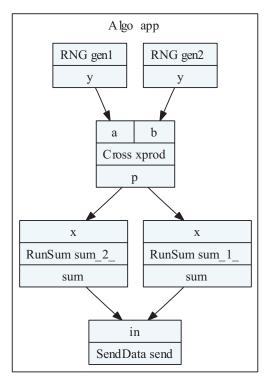

| 2.1  | Overview of X Language description                                        | 28 |

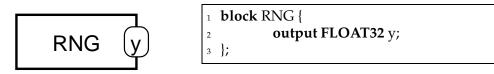

| 2.2  | A basic block                                                             | 28 |

| 2.3  | Another block                                                             | 29 |

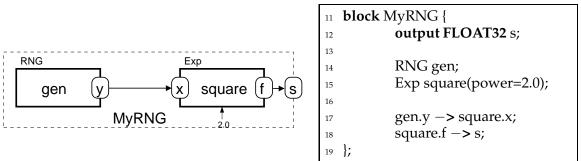

| 2.4  | A compound block                                                          | 30 |

| 2.5  | A complete algorithm                                                      | 30 |

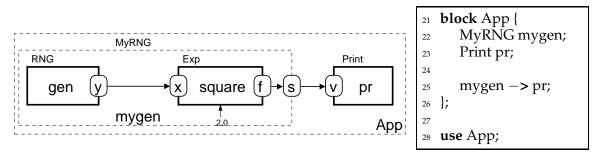

| 2.6  | The complete Section 2.2.1 example                                        | 32 |

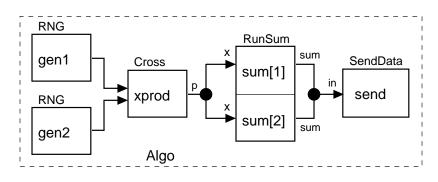

| 2.7  | A more complex algorithm                                                  | 32 |

| 2.8  | The complete Section 2.2.2 example                                        | 33 |

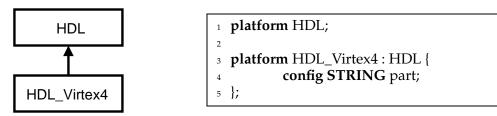

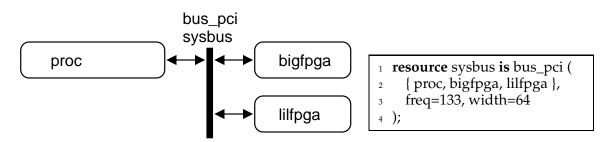

| 2.9  | Example HDL platform hierarchy                                            | 35 |

| 2.10 | Example C platform hierarchy                                              | 36 |

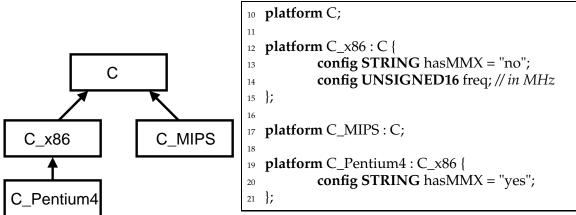

| 2.11 | Example bus linktype hierarchy                                            | 36 |

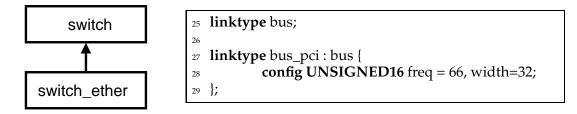

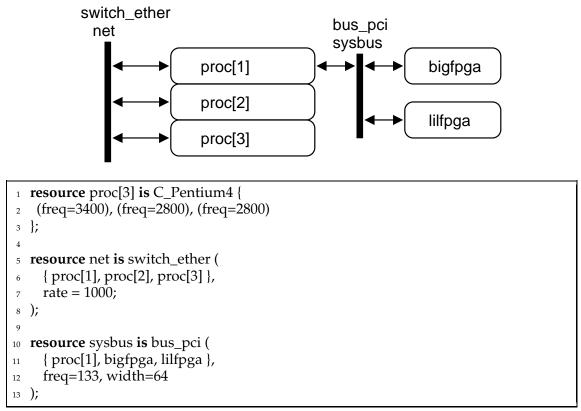

| 2.12 | IR instantiation and small processing architecture example                | 37 |

| 2.13 | Larger processing architecture example                                    | 38 |

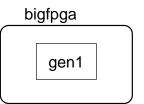

| 2.14 | Mapping to a computation resource                                         | 39 |

| 2.15 | Mapping to an interconnect resource                                       | 39 |

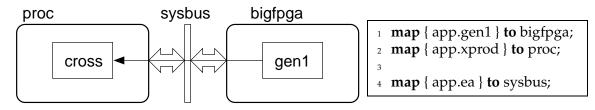

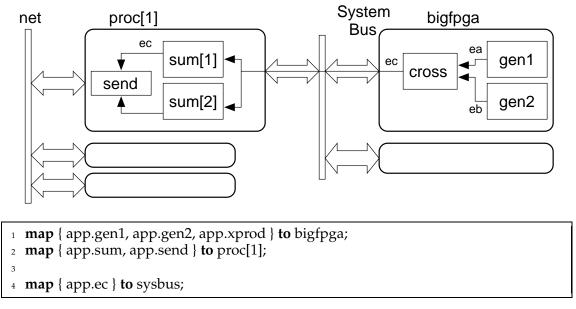

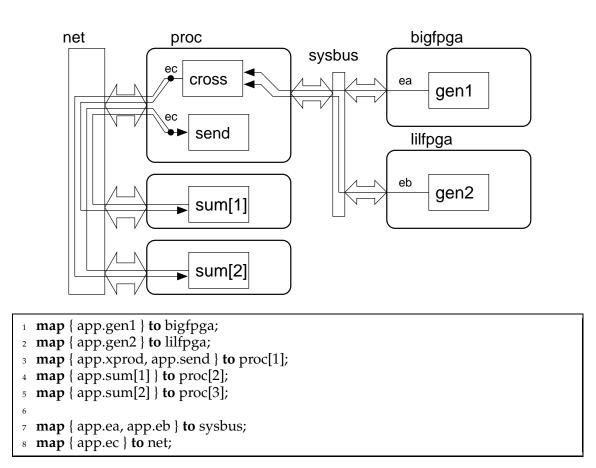

| 2.16 | A complete mapping                                                        | 40 |

|      | Another complete mapping                                                  | 41 |

| 3.1  | X-Com flow (same as Figure 1.8)                                           | 60 |

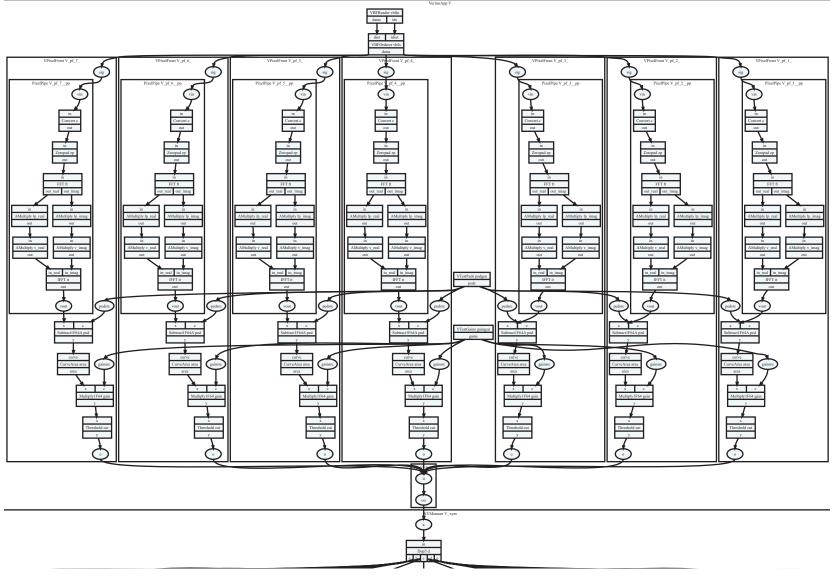

| 3.2  | Visualization of the Section 2.2.2 example using X-Viz                    | 61 |

| 3.3  | A large algorithm visualization using X-Viz                             | 62  |

|------|-------------------------------------------------------------------------|-----|

| 3.4  | Example X Block and corresponding X Language C API structure            | 65  |

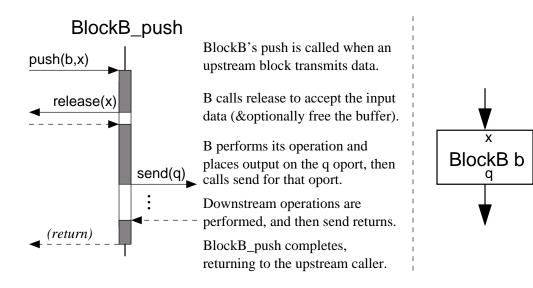

| 3.5  | Sequence diagram of edge communication using the C API                  | 67  |

| 3.6  | Sequence diagram of communication between two blocks in one processor . | 67  |

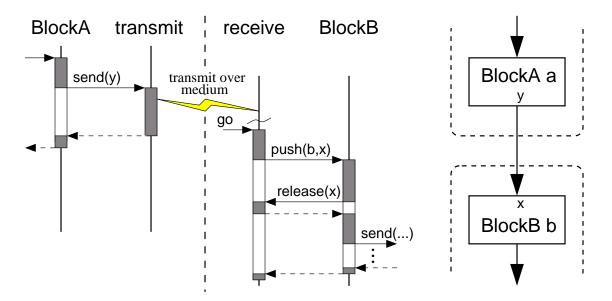

| 3.7  | Sequence diagram of communication between two blocks on two processors  | 68  |

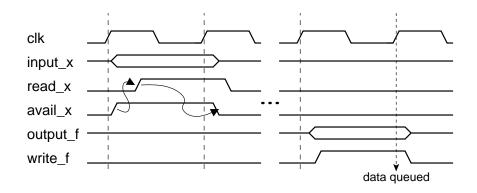

| 3.8  | Timing diagram of the HDL API                                           | 70  |

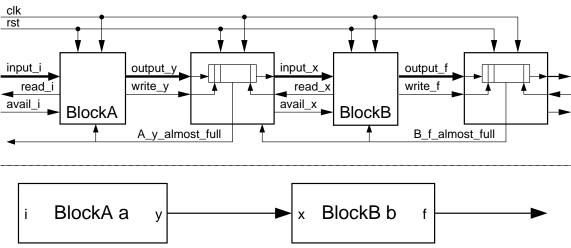

| 3.9  | Interface diagram of edge communication using the HDL API               | 71  |

| 3.10 | Edge collapse operation                                                 | 73  |

| 3.11 | Edge simplification operation                                           | 74  |

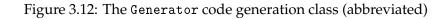

| 3.12 | The Generator code generation class (abbreviated)                       | 75  |

| 3.13 | The LinkCode I/O code generation interface (abbreviated)                | 76  |

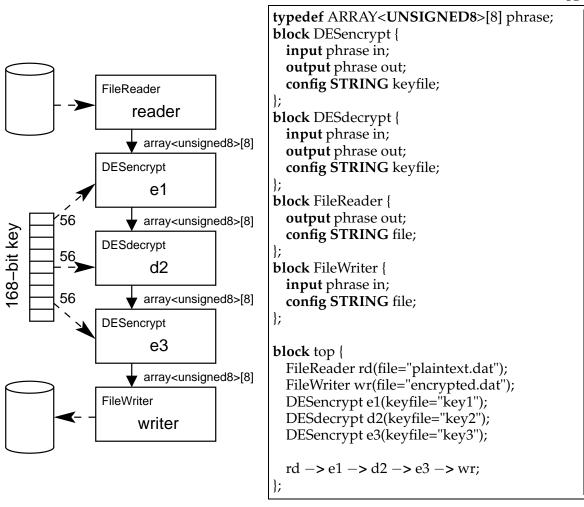

| 4.1  | Triple-DES algorithm flow and X code                                    | 81  |

| 4.2  | Triple-DES mappings                                                     | 82  |

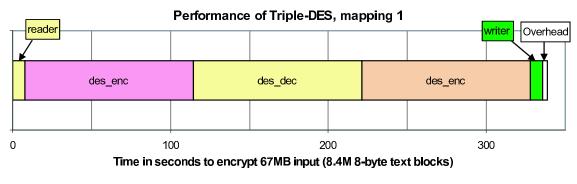

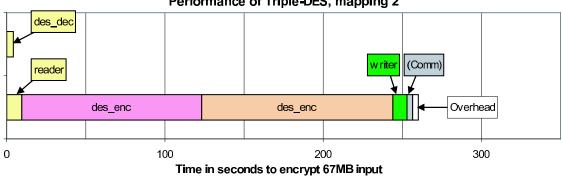

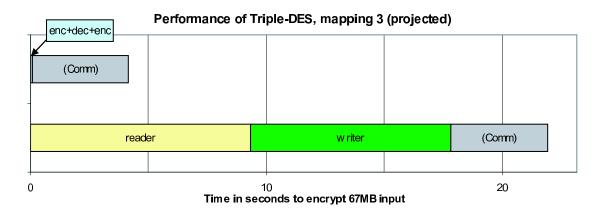

| 4.3  | Results of mapping 1                                                    | 83  |

| 4.4  | Results of mapping 2                                                    | 83  |

| 4.5  | Results of mapping 3                                                    | 84  |

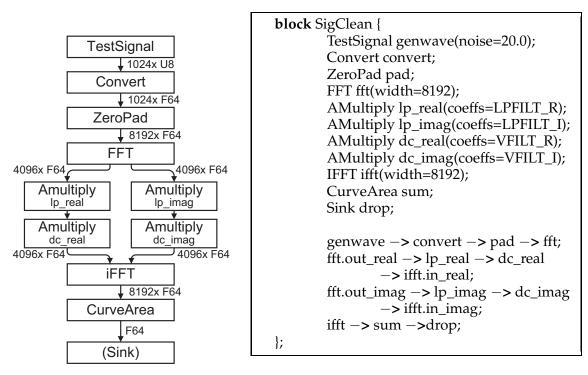

| 4.6  | Signal cleaner algorithm flow and X code                                | 85  |

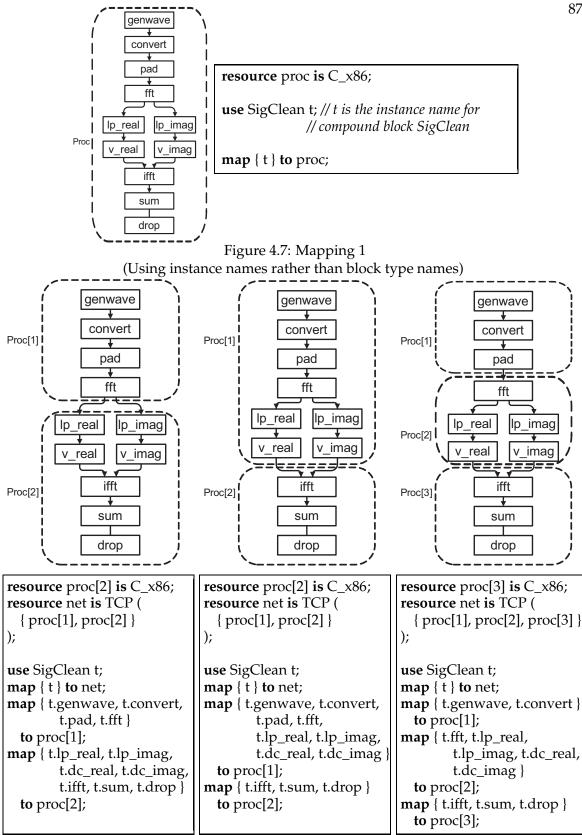

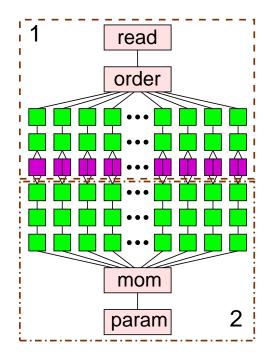

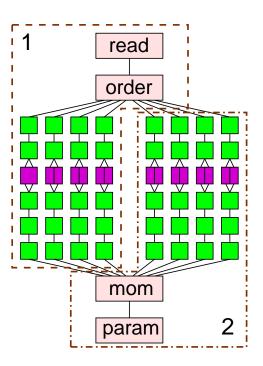

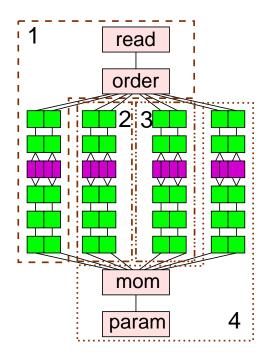

| 4.7  | Mapping 1                                                               | 87  |

| 4.8  | Mapping 2                                                               | 87  |

| 4.9  | Mapping 3                                                               | 87  |

| 4.10 | Mapping 4                                                               | 87  |

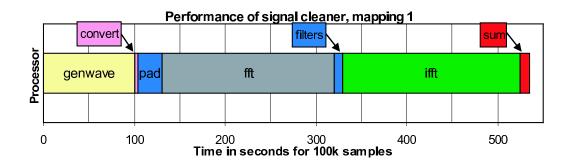

| 4.11 | Results of mapping 1                                                    | 88  |

| 4.12 | Results of mapping 2                                                    | 90  |

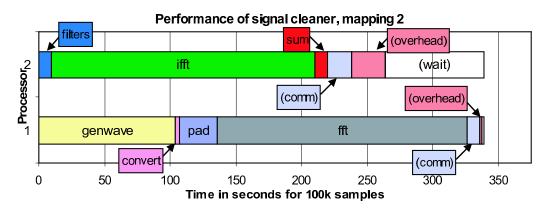

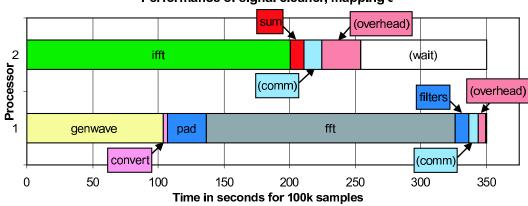

| 4.13 | Results of mapping 3                                                    | 91  |

| 4.14 | Results of mapping 4                                                    | 92  |

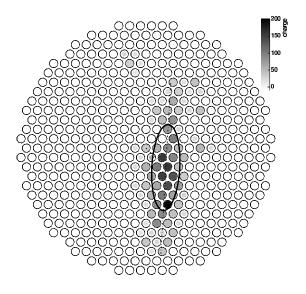

|      | VERITAS PMT array with sample event superimposed                        | 96  |

| 4.16 | VERITAS gamma ray signal processing pipeline in X                       | 98  |

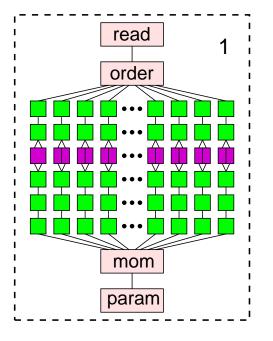

| 4.17 | Mapping 1                                                               | 101 |

| 4.18 | Mapping 2                                                               | 101 |

| 4.19 | Mapping 3                                                               | 101 |

| 4.20 | Mapping 4                                                               | 101 |

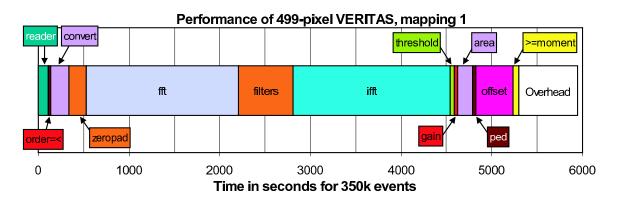

| 4.21 | Results of mapping 1                                                    | 102 |

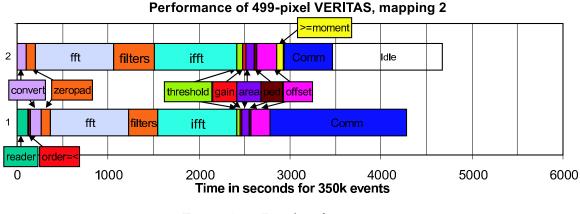

| 4.22 | Results of mapping 2                                                    | 103 |

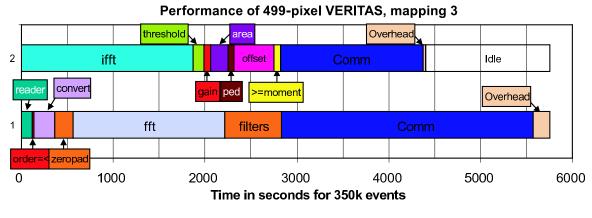

| 4.23 | Results of mapping 3                                                    | 104 |

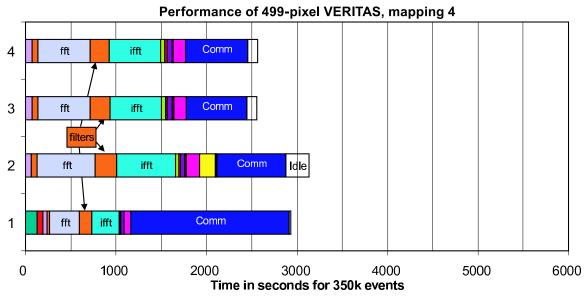

| 4.24 | Results of mapping 4                                                    | 105 |

# Acknowledgments

First and foremost I would like to thank my family and friends for all their encouragement during the writing of this thesis.

Thanks to my mom and dad, who have always supported the directions I've taken in life with great enthusiasm.

Thanks to my friends, who have enriched my life with all the little distractions from work that keep me sane.

Thanks to my colleagues in the Storage Based Supercomputing group, and throughout the Computer Science and Engineering and Physics departments, for discussions which have been invaluable in writing this thesis, the compiler, and the science applications. Thanks in particular to my advisor, Mark Franklin, and Roger Chamberlain, for their feedback in making this thesis both useful and usable.

Finally, I am grateful for the financial support of the National Science Foundation through grant CCF-0427794, without which this and other valuable research would not have been possible.

Eric J. Tyson

Washington University in Saint Louis August 2006

## Chapter 1

## Introduction

This thesis introduces Auto-Pipe, a toolset and development environment that aids the creation of applications developed in a pipelined and/or parallel manner. Tools are provided to analyze performance and explore the many options in the design space. These options include, for example, the use of both real and hypothetical processing devices and connection topologies.

The X Language has been created to express the applications that use the Auto-Pipe tools. Analyses of these applications are performed with the X-Sim tool, a federated simulation environment which uses the X Language compiler. An optimization tool tentatively called X-Opt is proposed to find optimal mappings of algorithms onto complex sets of interconnected processing platforms and explore the design space. The capabilities and use of the X Language, X-Sim, and X-Opt are presented herein.

This chapter investigates the background and motivation for creating a new language and a new toolset. A set of prior work in this area is reviewed, including projects with similar techniques but dissimilar goals, some of which are complementary to the Auto-Pipe system. The design of the Auto-Pipe system and contributions thus far are discussed broadly as an introduction to the detailed discussion of the X Language and compiler found in the following chapter. An outline of the thesis is provided at the end of the chapter.

## 1.1 Background

Auto-Pipe is a development environment concentrating on high-performance applications. Auto-Pipe aids developers in creating and understanding applications distributed across multiple, potentially dissimilar computational nodes and interconnection resources.

Such applications are easily found in many areas of science and industry, including:

- Networking and communications

- Scientific computing, including real-time experimentation and offline data analysis

- Media creation and playback

- Data mining

The process of creating an efficient implementation of a given application can be broken into the following components:

- 1. Develop the algorithm:

- (a) Identify the tasks involved in the computation and program control.

- (b) Determine the communication structure of these tasks.

- (c) Implement (e.g., in C, C++, VHDL, etc.) the tasks as needed.

- (d) Evaluate the implementation's correctness by executing the algorithm on a simplified platform, such as a development machine.

- 2. Identify the *computation resources* (CRs) on which the application tasks may be deployed.

- 3. Identify potential communication topologies of these resources, specifically the *interconnect resources* (IRs) connecting sets of CRs.

- 4. Determine a *mapping* of the application tasks and communications onto the CRs and IRs. This mapping must be valid, thus it must:

- map all tasks and communications to compatible CRs and IRs in the topology,

- not exceed the resource limitations of any CR or IR, and

- map tasks in a manner that satisfies algorithm requirements for correctness.

- 5. Implement the mapping, creating the code to connect the tasks using the available IRs.

- 6. Execute the implementation and analyze the performance. Execution here may take place on real CRs and IRs, simulations of CRs and IRs, or a combination of both.

- 7. As needed, improve the application's performance based on the analysis of 6 by redoing the mapping in step 4, and repeating the subsequent steps.

As will be described in Section 1.3, the X Language enables expression of steps 1 through 4 above. Auto-Pipe tools then perform the remaining steps. The following discussion will examine, at a high level, the process described above.

Dataflow languages are languages that express an algorithm in terms of the flow of data between connected tasks with precise interfaces. The algorithm portion of the X Language can be considered as a dataflow language. Tasks in such a language can form a partially ordered set of data dependencies. This set is naturally visualized as a directed graph.

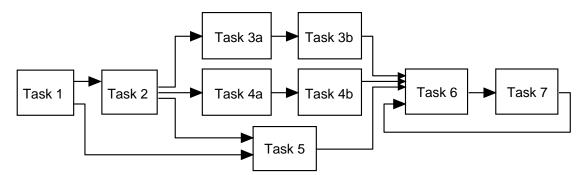

Figure 1.1: An example application dataflow

An example of such a directed graph is shown in Figure 1.1. This graph can be used to determine valid task execution schedules — for instance, Task 2 cannot run until Task 1 has completed, and Task 5 will depend on the output of *at least* one of Task 1 or Task 2, and

possibly both. To completely understand the algorithm, though, additional information is needed. The semantics of both tasks and edges must be known — does Task 1 produce data on both of its outputs, or just one or the other? And does Task 6 consume the three forward inputs at the same time, or individually? Furthermore, the *feedback loop* edge that connects Task 7 to Task 6 can clearly present a scheduling challenge, and may even introduce the risk of deadlock.

In this thesis, only *feed-forward* pipelines are considered. More advanced techniques may be employed to deal with topologies containing feedback loops, however these will not be presented in this thesis. A feed-forward pipeline is a sequence of tasks that contains only forward-directed edges; no edges may connect to tasks occuring earlier in the sequence. These pipelines may be expressed as acyclic directed graphs.

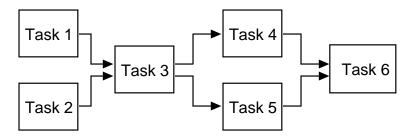

Figure 1.2: An example feed-forward pipeline

Figure 1.2 shows a simple pipeline of six tasks that will be used as an example. The process of determining what tasks 1 through 6 do, and how they are connected, is equivalent to steps 1(a) and 1(b) in the procedure from page 2. To create an executable application from this pipeline, the *processing architecture* must also be determined.

Processing architectures are graphs of connected *computation resources* (CRs). A CR is a generic term for a device that is capable of performing tasks, and includes general purpose processors (e.g., the Intel x86 series), embedded processors, network processors, field-programmable gate arrays (FPGAs), digital signal processors, and others. Identifying the CRs on which the user may potentially place the algorithm constitutes step 2 of the overall procedure.

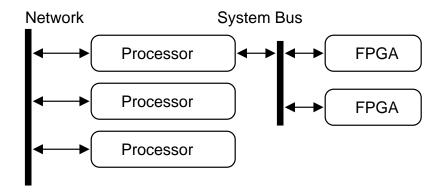

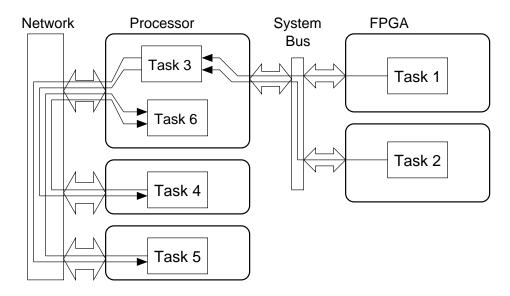

Figure 1.3: An example processing architecture

Also important to the behavior of a processing architecture are the connections, or *interconnect resources* (IRs). Identifying the IRs corresponds to step 3 of the application development process. IRs can be one-way or bidirectional, and can be point-to-point or shared. Sometimes processors are not directly connected to each other, but rather communication must be forwarded over one or more other processors. Additionally, real-world connection fabrics can be almost arbitrarily complex when resource sharing, non-uniform access, non-deterministic performance (such as the Internet), and other behaviors are taken into account.

An example of a processing architecture is given in Figure 1.3. In this figure, three processors share a switched network. Another two CRs, FPGAs, are connected to one of the processors using a system bus. For this example, it will be assumed that the processors are roughly equivalent when performing the same operations, while the FPGAs may have very different performance for the same task.

*Mapping* is the operation of assigning a specific task to a CR, or a specific interconnecting edge to an IR. A complete mapping of an application involves performing this step for every task and edge. In order to implement and execute an application, a complete mapping must be performed. Determination of a mapping is step 4 of the development procedure and completes the X Language program description.

The choice of a "good" mapping can become quite difficult, both in a computation sense (the minimum parallel processor total flow time problem is NP-Hard [19]) and in choosing the proper method and performance metric to evaluate what constitutes a "good" mapping. In general, a good mapping choice cannot simply consider the best resource available for a single task, due to a large number of conflicting factors such as:

- Relative performance of each task on different resources

- Relative performance of the different interconnections

- Resource contention within the processing resources

- Resource contention within the interconnection resources

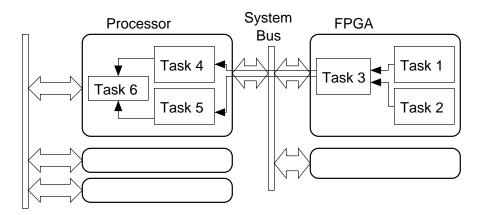

Figure 1.4: An example of mapping the algorithm to the processing architecture

Figure 1.4 demonstrates one potential mapping of the example application onto the example architecture. In this example, tasks 1, 2, and 3 have been mapped to one FPGA, and tasks 4, 5, and 6 have been mapped to the first processor. This mapping causes task 3 to communicate with tasks 4 and 5 over the system bus, while other task communications take place within the processor; in an FPGA, this might be a simple handshaking protocol, and on a processor this could be a function call or a job queue.

Figure 1.5 demonstrates another possible mapping of the same application and architecture. In this example, the tasks have been distributed more evenly across the processors.

Figure 1.5: Another example of mapping the algorithm to the processing architecture

Depending on their relative performance, this may cause the tasks to execute more efficiently than in the first mapping; execution of tasks 4 and 5 have been distributed to two processors, and there is more potential for parallel task execution.

Note that the second mapping may not actually perform better than the first, even with better distribution of computation since there is much more communication over the network interconnect. Communication overhead, especially over the shared link, may offset the faster computation. This demonstrates a common tradeoff that occurs in parallel computing — the balancing of algorithmic parallelism versus the reduction of communications overhead. Determining which mapping results in higher overall performance requires consideration of the overall system performance including the performance of each task and communication link in the system. This analysis is performed in step 6 (page 3), and the results are used for step 7, which regenerates the mapping to improve performance.

A second level of resource association called *binding* is considered later. Binding concerns the deployment of CRs and IRs onto particular real-world devices (or simulations/emulations of such devices). Mechanisms to bind and deploy are not examined in depth in this thesis; our approach to this operation will be briefly discussed in Chapter 3.

The performance of streaming applications are generally evaluated in terms of two metrics: *latency*, the time from input to output of time-sensitive data, and *throughput*, the quantity of data processed per unit time. Other metrics such as power consumption and total implementation costs are also used. This thesis concentrates primarily on maximizing throughput, which is often the most important metric in high-performance applications without strict latency requirements.

## 1.2 Motivation

Auto-Pipe was created to overcome several difficulties in developing applications that are distributed across diverse computational nodes, particularly those that benefit from being decomposed into pipelines and other parallel structures.

The difficulties addressed by Auto-Pipe include:

- Implementing an application expressed in both hardware and software programming languages (often referred to as hardware/software *co-design*), or multiple software languages, is awkward and error-prone.

- Debugging and simulating such a mixed infrastructure (*co-simulation* or federation simulation) to ensure functional correctness.

- Developing efficient communication interfaces to transport data between CRs. This is tedious, time-consuming, and often unnecessarily repeats work done by others.

- Measuring the implications of different CR partitionings, performance-area tradeoffs, performance-memory tradeoffs, and various mappings. This is generally timeconsuming and lacks sufficient tool support.

- Optimizing system performance over a large design space.

Due to these obstacles, designers are presently faced with a set of choices:

- Put a large amount of effort into developing, debugging, and optimizing the application across multiple platforms: This approach requires time, money, and programmers skilled in developing and optimizing for each of the platforms used.

- Limit the application to only general purpose CPU platforms for which development tools are available and which tend to be less expensive and easier: This results in an implementation that may not fully exploit the speed and unique performance capabilities of general purpose processors, programmable hardware (e.g. FPGAs), and special-purpose CPUs (e.g. DSPs).

- Limit the simulation and optimization of the co-designed system: This also may reduce the performance of the application. Developers choosing this option are often left with a system having unpredictable performance, and for which development efforts may concentrate on the wrong set of components.

In each of these choices, the developer ends up with a limited implementation of the application that cannot be easily extended to new processing platforms.

Auto-Pipe is an option that provides developers with a rich set of development and analysis tools to overcome these obstacles. It also provides an infrastructure to easily add support for new platforms and efficient communications links.

## 1.3 The Auto-Pipe System

The Auto-Pipe system and its components were created to aid developers of streaming applications. Auto-Pipe comprises a set of tools, compiler-level libraries, and user-level libraries to create an environment for the development of individual applications.

The three primary tool components are discussed below: the compiler, the simulation environment, and the performance optimizer. The X Language and compiler are the main subject of this thesis; the simulator and optimizer are currently under development and only their preliminary design is introduced here.

#### 1.3.1 The X Language and Compiler

The primary means of expressing the programs created and analyzed using Auto-Pipe is the X Language. While its compiler, X-Com, does not depend on other Auto-Pipe tools, X has been developed specifically for the Auto-Pipe system and application development is greatly enhanced by use of its tools. The X Language is a coarse-grained dataflow coordination language where the actual tasks are expressed and executed utilizing other traditional and non-traditional programming languages. X programs describe a hierarchy of tasks, called *blocks*, and the interconnections of their interfaces, called *edges*. The language also provides a syntax to describe classes of computation resources on which tasks are to eventually execute and to describe the specific instances of these resources. A block-to-CR *mapping* may then be specified to indicate on which resources the tasks are to execute. The X Language has syntax to place portions of the application on different CRs, and easily change this allocation in order to explore the performance of the system under different partitionings.

As part of X-Com, an internal interface has been developed to connect modules that perform code generation. This interface is easily extended so that users can target new devices and languages without changing the dataflow synthesis and analysis details that form the core of X-Com and other tools.

Application programmer interfaces (APIs) have been created for a variety of programming environments to allow users to create their own blocks which can be used by X. Particular attention has been paid to the usability of these interfaces, as it is expected that most users of X and Auto-Pipe will want to create their own blocks for application-specific tasks (such as sensor or database I/O).

The output of X-Com is a set of "almost executable" source code files corresponding to each CR in the processing architecture. A second tool, X-Dep, the X application deployer, is used to perform the final linking steps and deploy the application to real hardware devices or simulations (or emulations) of devices. This tool does not affect the actual behavior of the

generated executable; it only makes the X-Com-generated code deployable to its intended real target. X-Dep is discussed further in Section 3.2.

#### **1.3.2** The X-Sim Simulation Environment

Another core component of the Auto-Pipe toolset is X-Sim, a simulator for X applications partitioned across multiple simulated devices. X-Sim incorporates software and hardware simulations (of various fidelity) to characterize the performance of the system and of individual blocks, edges, and interconnects. These characteristics can be interpreted by the designer (using analysis tools) to locate performance bottlenecks and motivate design decisions. X-Sim also permits the testing of hypothetical devices and topologies to further drive the design process.

X-Sim comprises a set of steps surrounding the X compiler. When performing an X-Sim simulation, "simulation bindings" are passed to X-Com that indicate which components are to be simulated, along with the type of simulator and potential simulation options. For instance, the C generator might support simulation using either native processor execution or execution under SimpleScalar [5], where the latter could be passed options indicating what degree of simulation fidelity is desired. The output of X-Com is a set of code that may be directly compiled, cross-compiled, or specially linked (depending on the requirements of the simulator) through binding.

The code generated by the simulation-bound applications uses a simulation-mode interconnect mechanism. This mechanism uses an intermediate data file to store the data transmitted along an edge; this common format permits communication between different simulators. Depending on the simulation environment, it may also generate a file containing processing times and potentially other run-time information (e.g., instantaneous power, cache misses, etc.). After each intermediate data set is written, X-Sim uses a communication model corresponding to the edge's IR to model the time delay before the data is available to the receiving block. A second timestamp file is generated that reflects the transmission delay, and the data and timestamps are then provided to the simulator of the receiving block. Since simulators of widely varying quality are supported, the simulator might or might not actually make use of the timestamps.

X-Sim is used to gather performance statistics and processing characteristics for each simulated device, to better understand the execution of the application. X-Sim will also be used with a performance analysis tool to further examine and optimize the data flow. This analysis is then used with the third major component of Auto-Pipe, the X-Opt performance optimizer, which is described in the following section.

#### 1.3.3 The X-Opt System Performance Optimizer

The final main piece of the Auto-Pipe toolset is X-Opt, an optimizer for X applications. Given a feed-forward pipelined, streaming application, X-Opt will use a combination of the simulator and a throughput (or latency) optimization algorithm to find optimal or near-optimal task-to-CR and CR-to-device allocations.

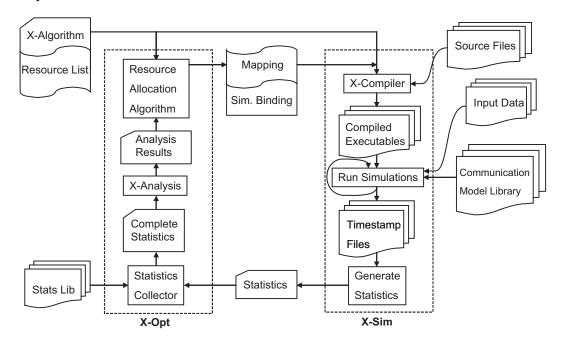

Figure 1.6: X-Opt Flow Chart

Figure 1.6 diagrams the design of X-Opt and its connection with X-Sim. X-Opt (or the user) creates an initial mapping and binding of blocks and edges to devices which are then simulated using X-Sim. X-Opt is responsible for ensuring that this mapping-binding is valid, with all blocks and edges properly mapped to resources. After gathering and analyzing statistics for this mapping, X-Opt revises its mapping-binding and repeats the simulation. This continues until a satisfactory result or some other end condition is reached.

This thesis does not deal directly with implementation of X-Opt and X-Sim. To demonstrate overall system capabilities, the "resource allocation algorithm" block for examples presented here utilize a human trial-and-error approach. The goal, however, is to eventually have a largely automated computer algorithm.

#### 1.3.4 Auto-Pipe Development Flows

The X Language is open-ended and the Auto-Pipe tools permit the user to approach development of an application in a number of ways. There are four progressively more thorough development procedures or "flows" for the Auto-Pipe system discussed here which most users will likely use or expand upon for their development.

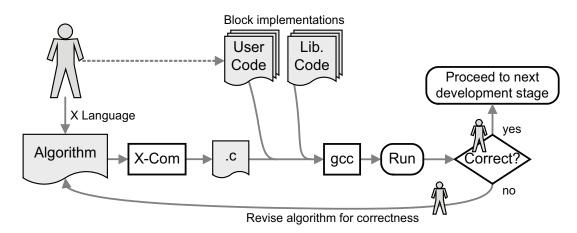

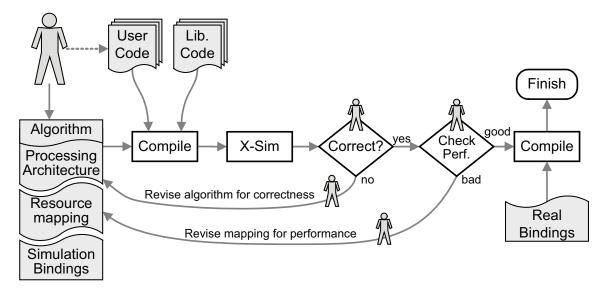

Figure 1.7: X-Com algorithm design flow

The most basic flow is depicted in Figure 1.7. Here, the user first creates an X Language file containing their algorithm partitioned into X blocks which are implemented in C (the

default for testing). This algorithm instantiates blocks from the available libraries and any user-defined blocks that are needed. X-Com processes the file and creates a top-level source file that can be compiled to a single-threaded executable that runs on the native machine. The user examines the output for functional correctness, redesigning the algorithm as necessary, until a implementation has been created that is correct.

Note that this flow does not yet create hardware components, nor does it use multiple computational resources. In general, block implementations are easier to write, test, and debug when written in software using single-threaded execution. Most users will desire to first develop their overall algorithm using this model, before introducing the complexities of hardware device programming and concurrent execution. It may not be desirable to directly deploy the result of this flow, as the generated program does not take advantage of any degree of parallelism. Rather, this is a useful initial testing stage before proceeding further.

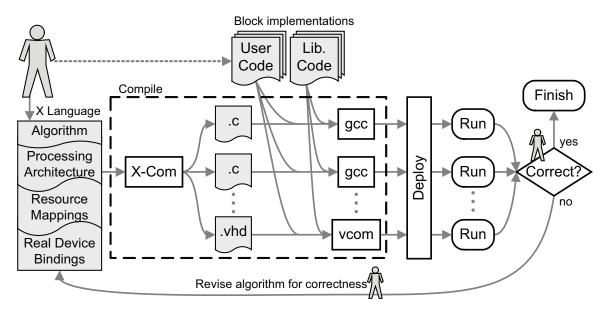

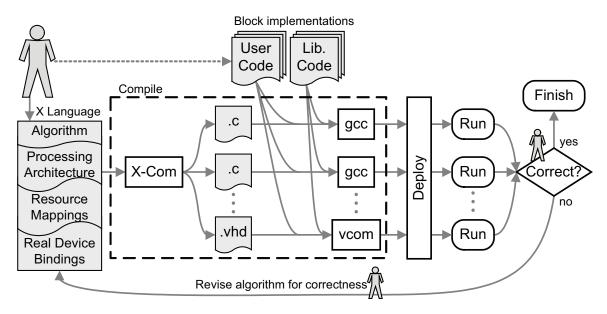

Figure 1.8: X-Com flow

The Figure 1.8 X-Com flow introduces user-selected processing architectures. In this flow, X-Com creates a top-level source file for each CR in an appropriate language (this mechanism is described in Chapter 2). Compilation of the generated source files is done using the appropriate language compiler for the target system, which may necessitate crosscompilation. After compiling, the user can deploy the finished application onto real compute and interconnect resources, execute the distributed application, and examine the output for correctness.

Figure 1.9: X-Com plus X-Sim flow "Compile" incorporates X-Com and the compiler steps depicted in Figure 1.8

The first performance-improving flow involves the X-Sim simulator, depicted in Figure 1.9. In this flow, compilation proceeds as before, except that the generated programs are bound to simulated environments instead of real devices. This causes X-Com to create simulation-mode source files that enable X-Sim to analyze the communications between blocks and run the executables on simulation platforms (such as SimpleScalar [5] or ModelSim [6]). As before, the generated source files are compiled using their respective compiler, potentially a cross-compiler or hardware synthesis tool. In addition to the correctness check as in the previous flow, the user may also examine the X-Sim performance report, which will give insight into what components of the processing architecture are potential performance bottlenecks. From this information, the user may attempt to revise the mappings to achieve

greater performance, such as by improving the task partitioning. Once performance is satisfactory, the simulation bindings are replaced with their "real" equivalents so that a deployable set of executables are created.

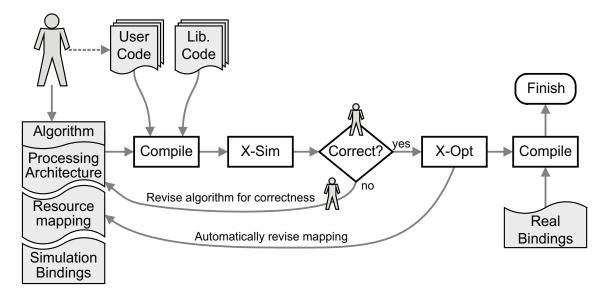

Figure 1.10: X-Com plus X-Sim plus X-Opt flow

Figure 1.10 modifies the flow of Figure 1.9 by replacing the user performance check with the X-Opt tool. X-Opt will explore the design space and be capable of quickly checking different performance characteristics. X-Opt will continually revise the mappings to test different configurations, until an end condition specified by the user is met (such as a minimum performance requirement or maximum exploration time).

### **1.4 Related Work**

The sequential programming model is widely understood to be the most basic and ubiquitous way to develop an application on present-day machines. Other models exist, however, to exploit the physical and logical parallelism present on many modern processing platforms and thus potentially achieve higher performance. Dataflow is a programming model that delineates the parallelism available in a program. Originally, dataflow was developed to exploit the massive parallelism available in some applications. It does this by departing from the globally updated memory model which had become a bottleneck for traditional von Neumann processors [16]. In dataflow, an application is expressed as a directed graph of processing tasks, each with all its inputs and outputs explicitly provided. In *fine-grain* dataflow, these tasks may be single instructions or logic operations. In *coarse-grain* (also called large-grain) dataflow, these tasks may be arbitrarily more complex, but usually describe a single high-level operation that is not efficiently or conveniently broken into smaller pieces [24].

Whereas early work concentrated on fine-grain dataflow to replace the classic von Neumann architecture, later work recognized that practically, better performance was reached on traditional machines through *hybrid* approaches, which use coarse-grain dataflow to direct internally von Neumann processes [25]. Modern dataflow architectures, especially in the digital signal processing (DSP) domain, have seen benefits from using such a hybrid approach [3]. Recently, Johnston, et al. have suggested that coarse-grain approaches "[offer] the most potential for improvements to dataflow programming" [16].

Dataflow languages tend to have many advantages, as well as limitations. By explicitly specifying the inputs and outputs of every task, the flow of data through the application may be optimized, which allows for an effective allocation of operations to resources. Certain applications, particularly DSP and audio/video media processing are easily expressed using dataflow, and several dataflow languages exist in these domains [12, 23, 33, 21].

Additionally, dataflow lends itself to visualization, which has a positive effect on the communicability of dataflow programs even to those not familiar with the language. This has led to the popularity of data flow visual programming languages (DFVPLs) such as Lab-View [14] with researchers in the natural sciences.

A recent development in dataflow has been the recognition of the *streaming* application domain. These are applications that operate on large sequential "streams" of consistently formed data such as audio, video, radio-frequency communications, network traffic, and

sensor network readings. The authors of the StreamIt language ascribe the following characteristics to streaming applications (paraphrased from [28]):

- The application operates on large or virtually infinite sequences of data.

- The algorithm performs a sequence of independent, self-contained transformation "filters" on the stream.

- The algorithm operates in a stable computation pattern, where the set of filters are "repeatedly applied in a regular, predictable order".

- The application will occasionally pass out-of-stream communications, such as error messages or changes to run-time configurations such as volume settings or filter coefficients.

- Users of the application expect high performance, in terms of resource efficiency, throughput, and latency.

Note that while this list is generally accurate, not all streaming applications rely on all these characteristics. Many limit or avoid the amount of out-of-stream communications passed through the system in order to simplify the portion of the application that needs to be fine-tuned. Also, it is quite common to leverage an increase in end-to-end latency in order to get an improvement in throughput through the use of pipelining techniques.

Given a sequential series of tasks and a pipeline of computation resources, it is possible to optimize the mapping of tasks to resources based on the performance (modeled or profiled) of each task. A variety of algorithms to perform this optimization in the context of network processors is presented in [7]. These algorithms are generalizable to the heterogenous systems supported in Auto-Pipe. Similar algorithms may be able to optimize for other metrics such as those mentioned in Section 1.1.

In order to optimize a mapping as mentioned above without a combinatorial explosion (every input data set, and every assignment of task to resource), the system must be modeled with certain assumptions. These analytically-based models can take many forms, the simplest and most common of which assumes that every task takes a different but constant time to perform its operation. This model, which often uses the mean value of the task execution time (and is thus called the "mean value model"), is often sufficient when task execution times have low variance. This simple model may also be extended [18] to support tasks with arbitrary degrees of processing time variance and covariances with other tasks. Additional models are needed to take into account data-correlated processing times and other complexities.

Auto-Pipe incorporates a wide set of features from many areas of computer technology. Thus, Auto-Pipe and the X Language share features with many related projects, both commercial and academic. The X Language has common goals with a diverse range of programming languages in the linguistic domains of dataflow, hardware description, simulation, and application-specific codesign. However, X is the only language to date that incorporates the broad set of features discussed below. Further empowered by X-Sim and X-Opt, the Auto-Pipe system builds on previous work in pipeline optimization.

Table 1.1 provides an overview of selected related projects, including languages, compilation tools, and design environments. Check marks ( $\sqrt{}$ ) indicate that the project (row) possesses that feature (column). The "Language" heading lists the languages (or language types) supplied by the user when creating applications. When multiple languages are used for different purposes within the project environment, the design or coordination language (or languange type) is listed first, followed by the implementation language(s). "Visual" refers to whether the dataflow graphs are visualized and/or edited through a graphical interface; "in" here means that dataflow graphs are input and edited visually, and "out" means that dataflow graphs may be visualized. "SW Gen" and "HW Gen" specify whether the parser or other tools can create components that are deployable to software or hardware using the application description. "Sim[ulation]," "Perf[ormance] Ana[lysis]," and "Optimization" indicate if the project supports reasonably useful algorithm simulation, application performance analysis, and analysis-based algorithm optimization, respectively.

| Project name | Language(s)             | Visual     | SW         | HW         | Het.         | Sim.         | Perf.        | Optim-  |

|--------------|-------------------------|------------|------------|------------|--------------|--------------|--------------|---------|

|              | (design; impl)          | in/out     | gen.       | gen.       | codes.       |              | ana.         | ization |

| GLU          | functional; C           |            |            |            |              |              |              |         |

| Ptolemy      | scripted; C, asm        | $\sqrt{/}$ |            |            |              |              |              |         |

| PtolemyII    | XML; Java               | $\sqrt{/}$ | *          |            | $\checkmark$ | $\checkmark$ | $\checkmark$ |         |

| LabView      | visual only             | $\sqrt{/}$ | $\sqrt{*}$ | $\sqrt{*}$ |              |              |              |         |

| StreamC      | C++-like; C++           |            |            |            |              |              |              |         |

| StreamIt     | C++-like; C             | / √        |            |            |              |              |              |         |

| X-Com only   | X; C, VHDL,             | /          |            |            | $\checkmark$ |              |              |         |

| Auto-Pipe    | as above                | / √        |            |            |              |              |              |         |

|              | * See text for details. |            |            |            |              |              |              |         |

Table 1.1: Overview of related projects

bee text for details.

Granular Lucid or GLU [15] is a language that, similar to X, employs a hybrid dataflowprocedural structure. Rather than use a simple structural language, however, GLU uses Lucid as its coordinating language. Lucid [2] is a functional dataflow language whereby function evaluations form the "flow" of the data. GLU uses the concurrency and control mechanisms of Lucid, but with procedurally defined (written in C) basic functions and datatypes. As a functional language, GLU's coordination syntax is more sophisticated than X at expressing control flow. However, this is at some detriment to large or deep algorithms, or those with high flow complexity such as highly branched topologies.

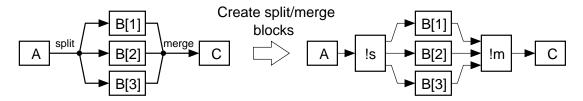

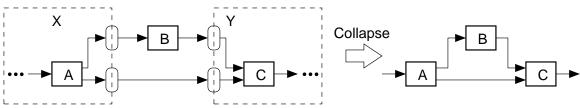

Ptolemy II [8] is "a set of Java packages supporting heterogeneous, concurrent modeling and design." It supports the simulation of a number of computation model domains, including dataflow, discrete-event and continuous-time systems, finite state machines, and process networks, and many other domains and sub-domains. Ptolemy II uses a GUI called Vergil to create XML descriptions of interconnected tasks. These tasks, or "actors," are implemented using Java, and are invoked by the appropriately scheduled calls from customized computation model domain controllers. Some work on code generation from Ptolemy II models does exist [29], but it is not a primary goal of Ptolemy II, and the generators neither concentrate on high performance, nor do they yet support any targets other than a desktop Java environment. Ptolemy II is a very vast, complex, and diverse environment, encompassing many different development and research goals as well as the different computation models.