#### Washington University in St. Louis

### Washington University Open Scholarship

McKelvey School of Engineering Theses & Dissertations

McKelvey School of Engineering

Spring 5-15-2015

### Utilizing Magnetic Tunnel Junction Devices in Digital Systems

Michael James Hall Washington University in St. Louis

Follow this and additional works at: https://openscholarship.wustl.edu/eng\_etds

Part of the Engineering Commons

#### **Recommended Citation**

Hall, Michael James, "Utilizing Magnetic Tunnel Junction Devices in Digital Systems" (2015). *McKelvey School of Engineering Theses & Dissertations*. 89. https://openscholarship.wustl.edu/eng\_etds/89

This Dissertation is brought to you for free and open access by the McKelvey School of Engineering at Washington University Open Scholarship. It has been accepted for inclusion in McKelvey School of Engineering Theses & Dissertations by an authorized administrator of Washington University Open Scholarship. For more information, please contact digital@wumail.wustl.edu.

#### WASHINGTON UNIVERSITY IN ST. LOUIS

School of Engineering and Applied Science Department of Computer Science and Engineering

> Dissertation Examination Committee: Dr. Roger D. Chamberlain, Chair Dr. Ron Cytron Dr. George Engel Dr. Viktor Gruev Dr. Robert Morley Dr. Dave Richard

Utilizing Magnetic Tunnel Junction Devices in Digital Systems by Michael J. Hall

> A dissertation presented to the Graduate School of Arts and Sciences of Washington University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> > May 2015 Saint Louis, Missouri

© 2015, Michael J. Hall

# **Table of Contents**

| Acknowledgments       xxx         Abstract       xxx         Chapter 1: Introduction       xxx                                                                      | $\mathbf{v}$    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Acknowledgments                                                                                                                                                     | x               |

| Abstract                                                                                                                                                            | xii             |

| Chapter 1: Introduction                                                                                                                                             | civ             |

|                                                                                                                                                                     | 7 <b>iii</b>    |

|                                                                                                                                                                     | 1               |

| 1.1 Uses of MTJs                                                                                                                                                    | 3               |

| 1.2 Virtualized hardware                                                                                                                                            | $\overline{7}$  |

| 1.3 List of contributions                                                                                                                                           | 8               |

| 1.4 Outline of the dissertation                                                                                                                                     | 10              |

| Chapter 2: Background and Related Work                                                                                                                              | 11              |

| 2.1 MTJ devices                                                                                                                                                     | 11              |

| 2.2 MTJ read circuits                                                                                                                                               | 14              |

| 2.3 Current conveyor operation                                                                                                                                      | 16              |

| 2.4 Magnetologic circuits                                                                                                                                           | 17              |

| 2.5 $C$ -slow transformation $\ldots \ldots \ldots$ | 19              |

| 2.6 Hardware virtualization                                                                                                                                         | 20              |

| 2.7 Queueing notation                                                                                                                                               | $\frac{1}{22}$  |

| 2.8 Vacation model                                                                                                                                                  | $\overline{23}$ |

| Chapter 3: MTJ Read Circuit Theory                                                                                                                                  | 25              |

| 3.1 Analysis of a current-mode read circuit                                                                                                                         | 26              |

| $3.1.1$ Methodology $\ldots$                                                                                                                                        | 27              |

| 3.1.2 Noise analysis                                                                                                                                                | 30              |

| 3.1.3 Validation                                                                                                                                                    | 33              |

| 3.1.4 Design guidance                                                                                                                                               | 38              |

| $3.1.5$ Discussion $\ldots$                                                                                                                                         | 50              |

| 3.2 Current conveyor structures                                                                                                                                     | 40              |

| 3.2.1 Basic                                                                                                                                                         | 40<br>42        |

|        | 3.2.2 P-cascode                                                                                                                                                            | 51         |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|        | 3.2.3 NP-cascode                                                                                                                                                           | 58         |

|        | $3.2.4$ Generalized $\ldots$                                                              | 64         |

| 3.3    | Read circuit design                                                                                                                                                        | 57         |

|        | 3.3.1 Area                                                                                                                                                                 | 0          |

|        |                                                                                                                                                                            | '1         |

|        | -                                                                                                                                                                          | <b>'</b> 4 |

|        |                                                                                                                                                                            | ·6         |

|        |                                                                                                                                                                            | <b>'</b> 6 |

|        |                                                                                                                                                                            | ~          |

| _      | 1 /                                                                                                                                                                        | <b>9</b>   |

| 4.1    |                                                                                                                                                                            | 80         |

|        | 0                                                                                                                                                                          | 33         |

|        | 0                                                                                                                                                                          | 86         |

|        |                                                                                                                                                                            | 88         |

| 4.2    | 1                                                                                                                                                                          | 0          |

|        | 0                                                                                                                                                                          | )3         |

|        |                                                                                                                                                                            | 95         |

|        |                                                                                                                                                                            | 96         |

| 4.3    | Experimental results                                                                                                                                                       | )8         |

|        | 4.3.1 Functional and performance testing                                                                                                                                   | 98         |

|        | 4.3.2 Static measurements $\ldots \ldots \ldots$           | )7         |

|        | 4.3.3 Stability and dynamic measurements                                                                                                                                   | 5          |

| 4.4    | Summary 11                                                                                                                                                                 | 9          |

| Chante | er 5: Virtualization of Hardware Logic Circuits                                                                                                                            | 1          |

| 5.1    | Clock model                                                                                                                                                                |            |

| 0.1    | 5.1.1 Model development of the expectation of the maximum of C samples                                                                                                     | 0          |

|        | of random variable $X$                                                                                                                                                     | 7          |

|        | 5.1.2 Model of $t_{CLK}$ and investigation of model $\dots \dots \dots$    |            |

| FO     |                                                                                                                                                                            |            |

| 5.2    |                                                                                                                                                                            |            |

|        | 5.2.1 Queueing model $\dots$ 13                                                                                                                                            |            |

| 5.0    | 5.2.2 Validation $\ldots$ 13                                                                                                                                               |            |

| 5.3    | $M/G/1$ queueing model development with vacation model $\dots \dots \dots$ |            |

|        | 5.3.1 Vacation waiting time model $\ldots \ldots \ldots$   |            |

|        | 5.3.2 Service time model $\dots \dots \dots$                               |            |

|        | 5.3.3 Queueing model                                                                                                                                                       |            |

|        | 5.3.4 Validation                                                                                                                                                           |            |

| 5.4    | Calibration of clock and resource models for three $C$ -slowed applications 15                                                                                             |            |

|        | 5.4.1 Synthetic cosine application with added feedback $(COS)$ 15                                                                                                          | 5          |

|        | 5.4.2 Advanced Encryption Standard (AES) cipher in cipher-block chaining                                                                                                   |            |

|        | mode $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $16$                                                                                          | 60         |

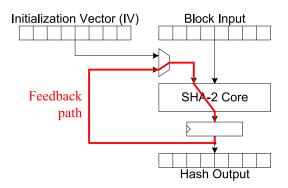

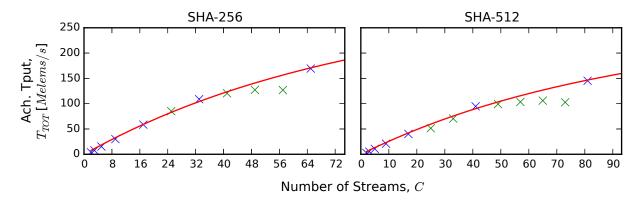

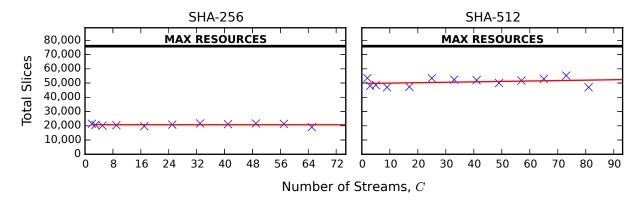

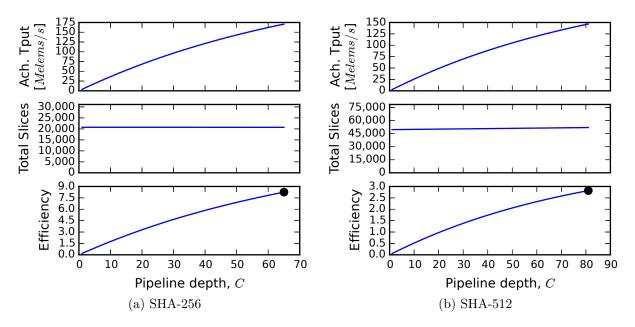

|        | 5.4.3 Secure Hash Algorithm (SHA-2) with 256 and 512 bit digests 16                                                                                                        | 5          |

| 5.5 Analytic model results                                                                            | 169 |

|-------------------------------------------------------------------------------------------------------|-----|

| 5.5.1 Design Scenario 1: Fix C, optimize for latency $(W_T)$                                          | 169 |

| 5.5.2 Design Scenario 2: Fix N, tune C, optimize for latency $(W_T)$                                  | 173 |

| 5.5.3 Design Scenario 3: Optimize for throughput-slice/area efficiency                                | 177 |

| 5.6 Summary $\ldots$ | 181 |

| Chapter 6: Conclusions and Future Work                                                                | 183 |

| 6.1 Conclusions                                                                                       | 184 |

| 6.2 Future work                                                                                       | 188 |

| References                                                                                            | 191 |

| Appendix A Read Circuit Design Guidance Validation                                                    | 197 |

| Appendix B Summary of Queueing Model Equations                                                        | 203 |

| Vita                                                                                                  | 207 |

# List of Figures

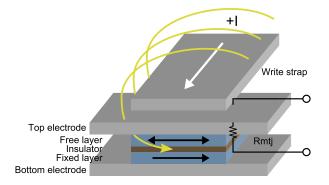

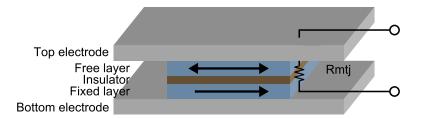

| Figure 1.1: | A magnetic tunnel junction (MTJ) device that encodes state informa-<br>tion in the magnetic orientation of the free layer | 2  |

|-------------|---------------------------------------------------------------------------------------------------------------------------|----|

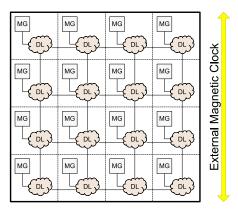

| Figure 1.2: | Magnetic clocking across a chip using an external magnetic field                                                          | 5  |

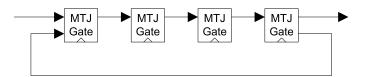

| Figure 1.3: | Pipelined magnetologic circuit with feedback                                                                              | 6  |

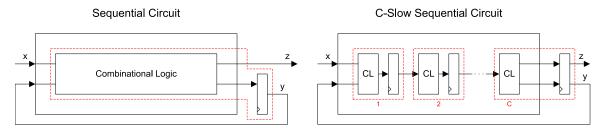

| Figure 1.4: | Application of the C-slow technique to a non-pipelined circuit                                                            | 7  |

| Figure 2.1: | Magnetic tunnel junction (MTJ) device                                                                                     | 12 |

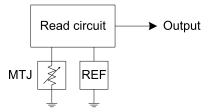

| Figure 2.2: | Read circuit block diagram for an MTJ                                                                                     | 14 |

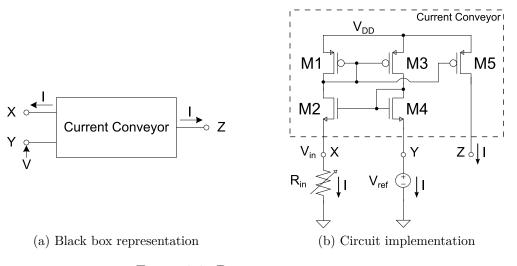

| Figure 2.3: | Basic current conveyor                                                                                                    | 17 |

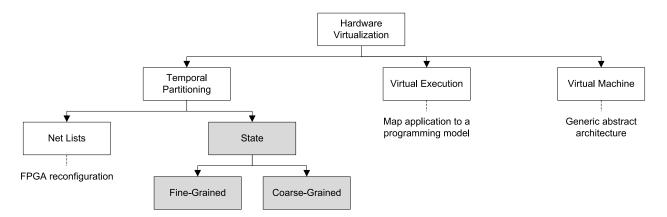

| Figure 2.4: | Hardware virtualization approaches                                                                                        | 21 |

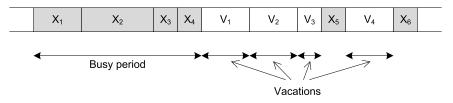

| Figure 2.5: | ${\rm M/G/1}$ queueing model with vacations                                                                               | 24 |

| Figure 3.1: | Noise model of the current-mode read circuit for sensing MTJ resistance                                                   | 28 |

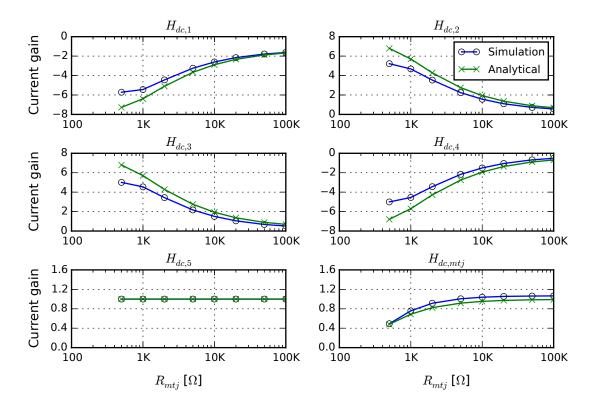

| Figure 3.2: | DC transfer function validation with analytical and simulation results                                                    | 34 |

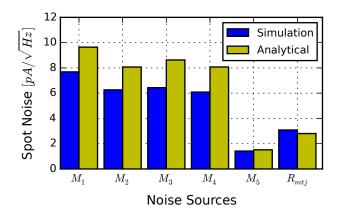

| Figure 3.3: | Thermal noise spectrum validation with analytical and simulation re-<br>sults                                             | 35 |

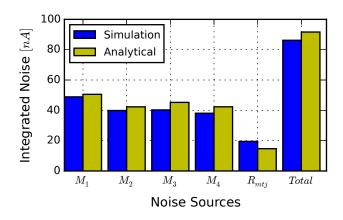

| Figure 3.4: | Total integrated output noise validation with analytical and simula-<br>tion results                                      | 38 |

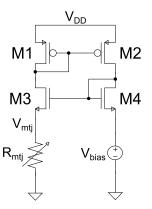

| Figure 3.5: | Basic current conveyor                                                                                                    | 43 |

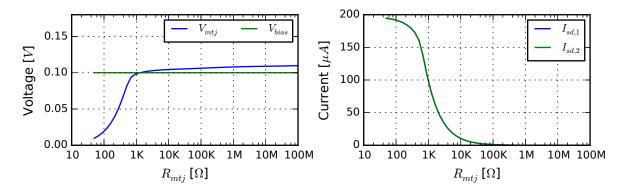

| Figure 3.6: | Simulation of the basic current conveyor                                                                                  | 51 |

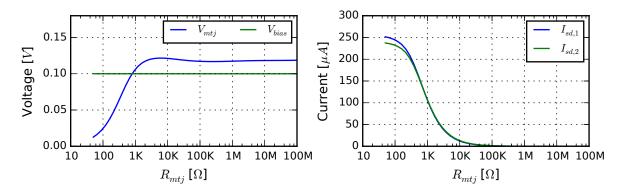

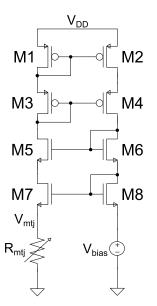

| Figure 3.7: | P-cascode current conveyor                                                                                                | 52 |

| Figure 3.8:  | Simulation of the P-cascode current conveyor                                                                                                                                                                   | 58  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

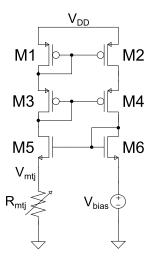

| Figure 3.9:  | NP-cascode current conveyor                                                                                                                                                                                    | 59  |

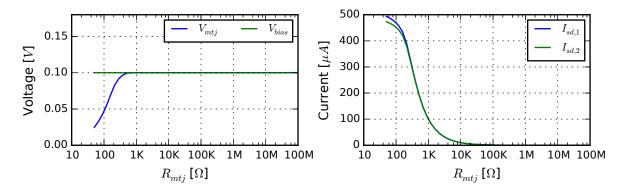

| Figure 3.10: | Simulation of the NP-cascode current conveyor                                                                                                                                                                  | 64  |

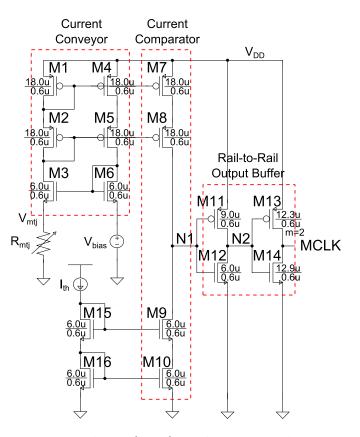

| Figure 3.11: | Resistance-to-voltage (R2V) read circuit in the 3M2P $0.5\mu\mathrm{m}$ process                                                                                                                                | 68  |

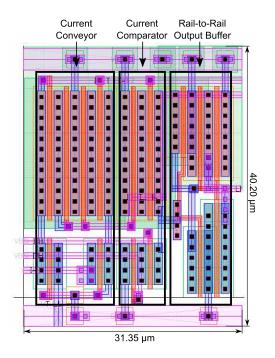

| Figure 3.12: | Layout of the R2V read circuit in the 3M2P $0.5\mu{\rm m}$ process $~.~.~.$                                                                                                                                    | 71  |

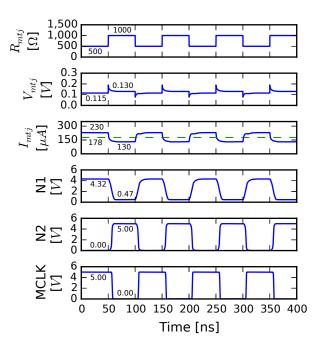

| Figure 3.13: | Transient response of the R2V read circuit at 10 MHz frequency                                                                                                                                                 | 72  |

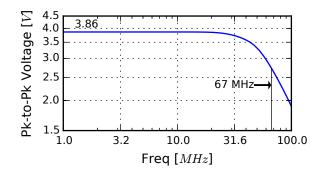

| Figure 3.14: | Node $N1$ peak-to-peak voltage of the R2V read circuit from 1 MHz to 100 MHz frequency in the 3M2P $0.5 \mu$ m process $\dots \dots \dots \dots \dots$                                                         | 74  |

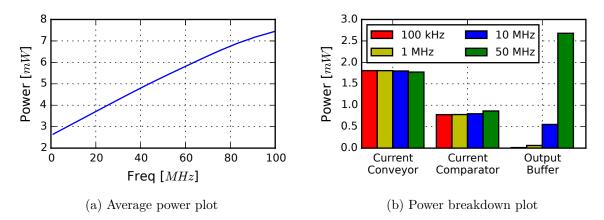

| Figure 3.15: | Average power and power breakdown plots of the R2V read circuit in the 3M2P $0.5 \mu$ m process $\dots \dots $ | 75  |

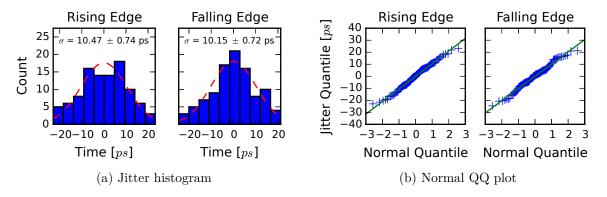

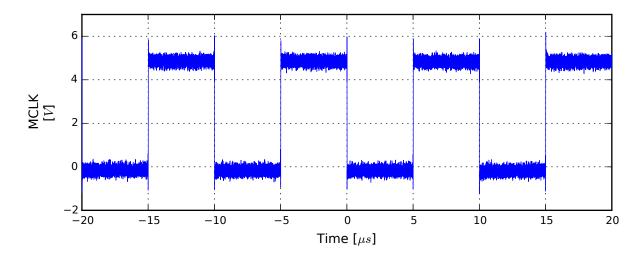

| Figure 3.16: | Jitter histogram and quantile-quantile (QQ) plot of the rising/falling edges of $MCLK$ of the R2V read circuit in the 3M2P 0.5 $\mu$ m process                                                                 | 77  |

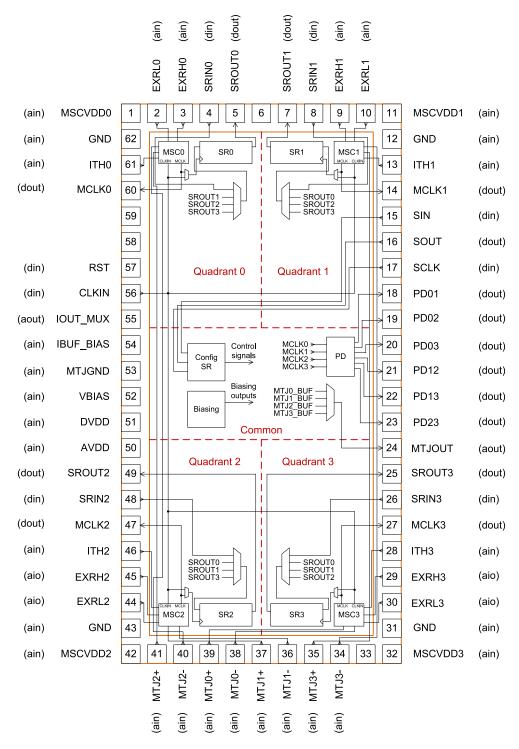

| Figure 4.1:  | Prototype test chip schematic (overview)                                                                                                                                                                       | 81  |

| Figure 4.2:  | Chip bonding diagram                                                                                                                                                                                           | 82  |

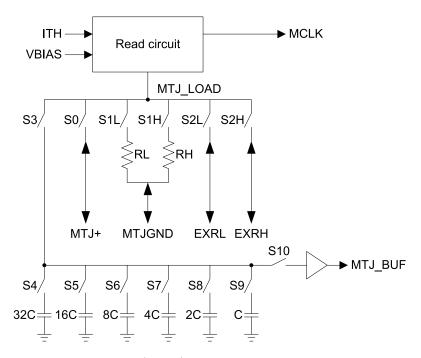

| Figure 4.3:  | Magnetic sense circuit (MSC)                                                                                                                                                                                   | 84  |

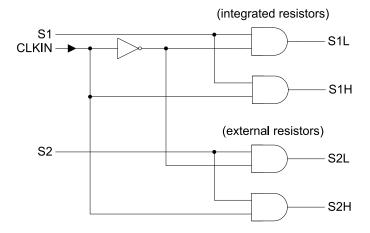

| Figure 4.4:  | MSC decode logic                                                                                                                                                                                               | 84  |

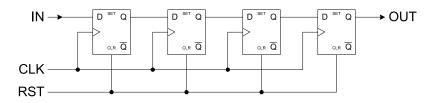

| Figure 4.5:  | Digital shift register                                                                                                                                                                                         | 87  |

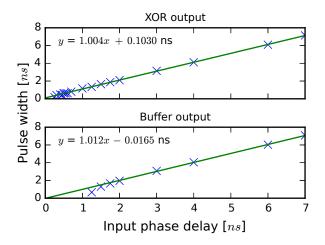

| Figure 4.6:  | Simulated phase detector response plot in the 3M2P $0.5\mu\mathrm{m}$ process .                                                                                                                                | 88  |

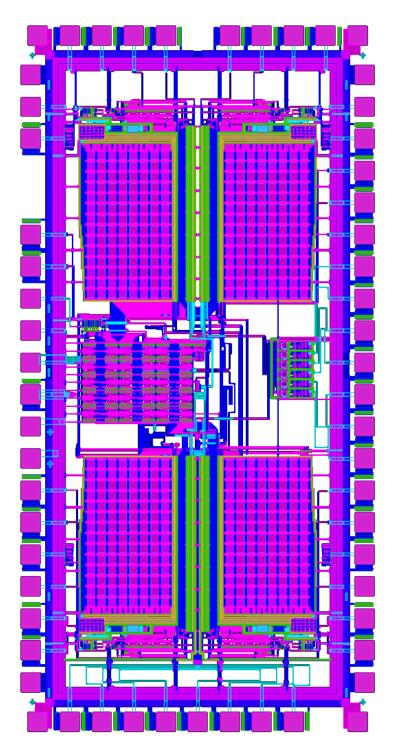

| Figure 4.7:  | Prototype test chip layout                                                                                                                                                                                     | 89  |

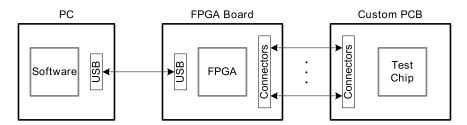

| Figure 4.8:  | System overview of test setup                                                                                                                                                                                  | 90  |

| Figure 4.9:  | Custom printed circuit board (PCB) for testing and interfacing to the prototype test chip                                                                                                                      | 93  |

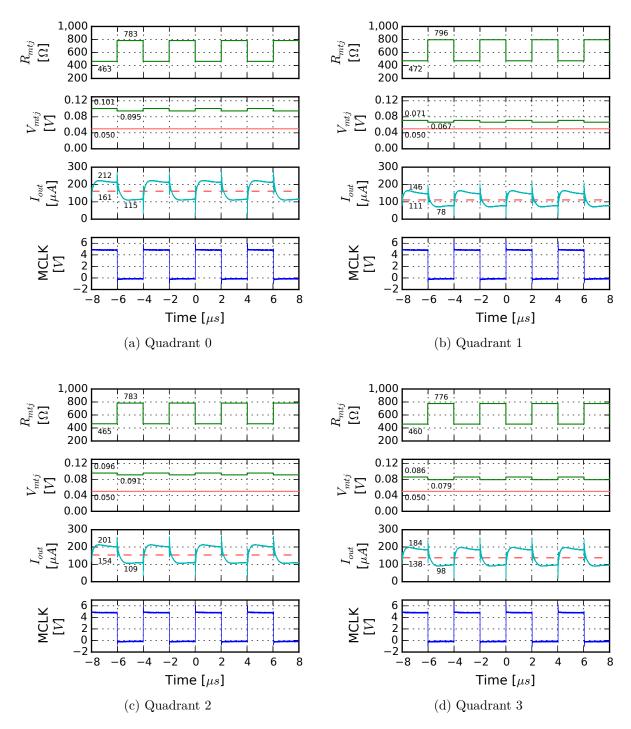

| Figure 4.10: | Functional test of the MTJ read circuit in each quadrant                                                                                                                                                       | 99  |

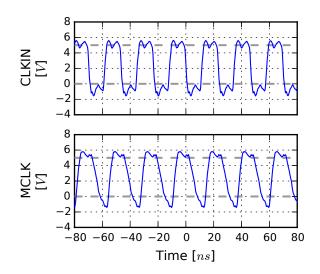

| Figure 4.11: | Performance test of the MTJ read circuit in quadrant 0 for external resistors at 43 MHz                                                                                                                        | 102 |

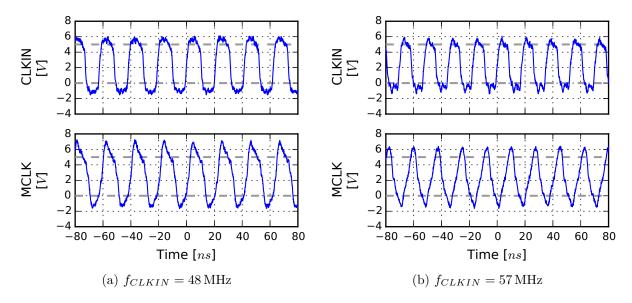

| Figure 4.12: | Performance test of the MTJ read circuit in quadrant 0 for internal resistors at two clock frequencies                                                                                                                         | 103 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

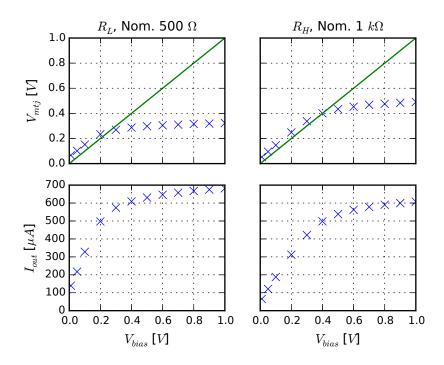

| Figure 4.13: | Linearity plots of the read circuit for internal resistors with nominal values $R_L = 500 \Omega$ and $R_H = 1 \mathrm{k}\Omega$                                                                                               | 110 |

| Figure 4.14: | Linearity plots of the read circuit for external resistors with nominal values $470 \Omega$ , $1 k\Omega$ , and $4.7 k\Omega$                                                                                                  | 111 |

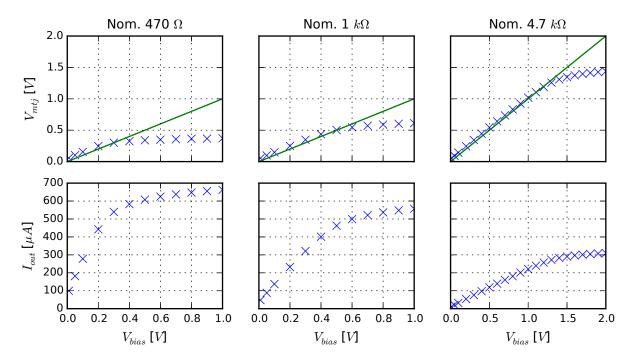

| Figure 4.15: | Ideal current limits for a theoretical current comparator                                                                                                                                                                      | 113 |

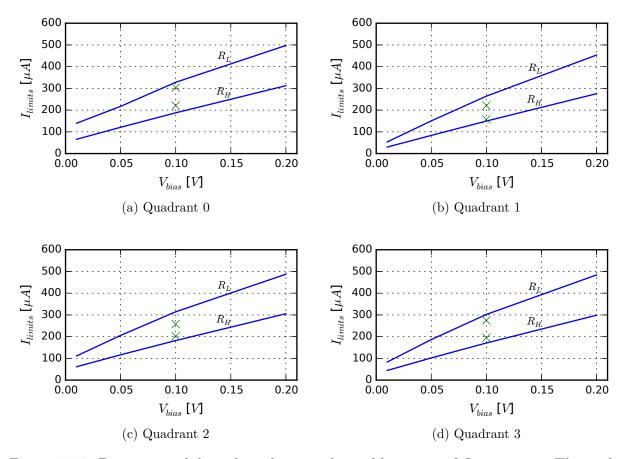

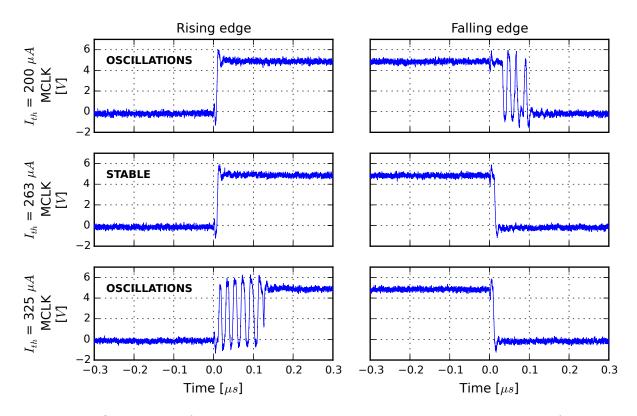

| Figure 4.16: | Dynamic stability plots showing the stable region of $I_{th}$ currents                                                                                                                                                         | 117 |

| Figure 4.17: | Output waveforms demonstrating oscillations and stable operation for multiple $I_{th}$ currents at the rising/falling edges $\ldots \ldots \ldots \ldots \ldots$                                                               | 118 |

| Figure 4.18: | Output waveform demonstrating stable operation at midway $I_{th} = 263 \mu\text{A} \dots \dots$                          | 118 |

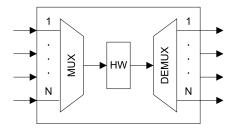

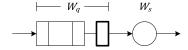

| Figure 5.1:  | Hardware virtualization for $N$ distinct data streams that perform the same computation $\ldots \ldots \ldots$ | 122 |

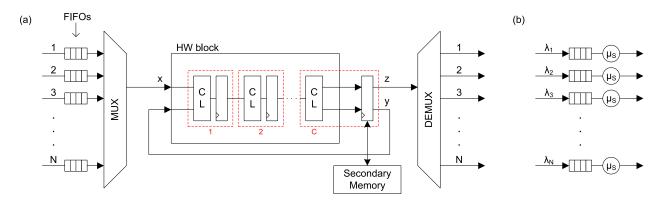

| Figure 5.2:  | General virtualized hardware configuration and queueing model $\ . \ .$                                                                                                                                                        | 124 |

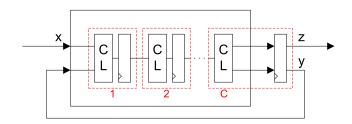

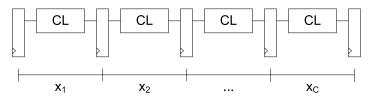

| Figure 5.3:  | $C$ -slowed circuit $\ldots \ldots \ldots$                                                                     | 126 |

| Figure 5.4:  | Stage-to-stage delay model                                                                                                                                                                                                     | 127 |

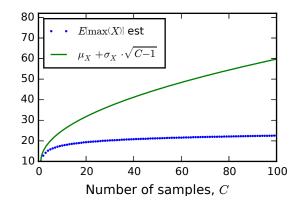

| Figure 5.5:  | Empirical simulation of $E[\max(X)]$ and its upper bound for $C$ random samples $\ldots \ldots \ldots$         | 128 |

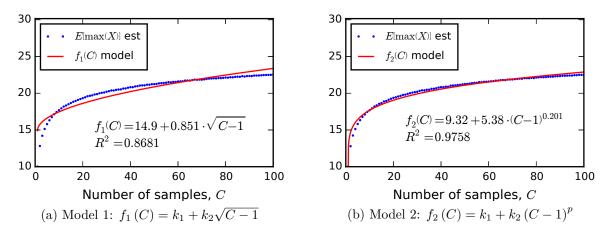

| Figure 5.6:  | Curve-fit of Model 1 and 2 with samples drawn from normal distribu-<br>tion $\mathcal{N}(10, 5^2)$                                                                                                                             | 129 |

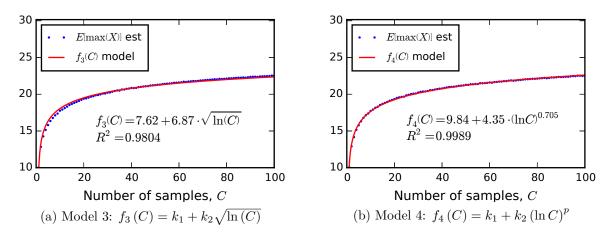

| Figure 5.7:  | Curve-fit of Model 3 and 4 with samples drawn from normal distribu-<br>tion $\mathcal{N}(10, 5^2)$                                                                                                                             | 131 |

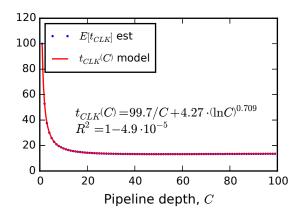

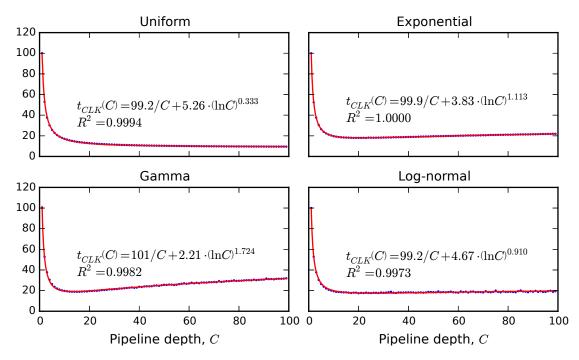

| Figure 5.8:  | Curve-fit of $t_{CLK}(C)$ model with samples drawn from a normal distribution ( $t_{CL} = 100, \sigma = 5$ )                                                                                                                   | 132 |

| Figure 5.9:  | Curve-fit of $t_{CLK}(C)$ model with samples drawn from various distributions $(t_{CL} = 100, \sigma = 5) \dots $        | 133 |

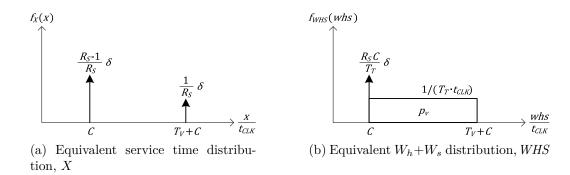

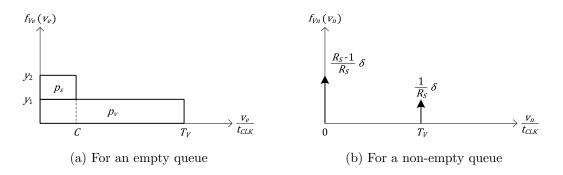

| Figure 5.10: | Equivalent distributions for $M/D/1$ model equations                                                                                                                                                                           | 139 |

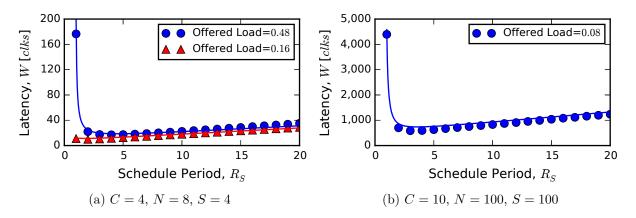

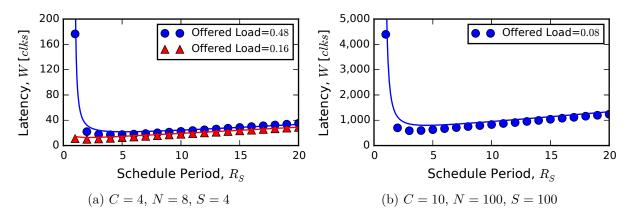

| Figure 5.11: | Discrete-event simulation of latency vs. schedule period for two sets of parameters for the $M/D/1$ queueing model                     | 140 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.12: | Single queueing station of system                                                                                                      | 141 |

| Figure 5.13: | Sub-model distributions used in the derivation of the vacation waiting time model                                                      | 142 |

| Figure 5.14: | Discrete-event simulation of latency vs. schedule period for two sets of parameters for the $M/G/1$ queueing model                     | 152 |

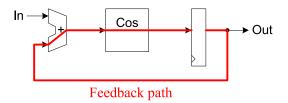

| Figure 5.15: | Block diagram of synthetic cosine application with added feedback $% \mathcal{A}$ .                                                    | 156 |

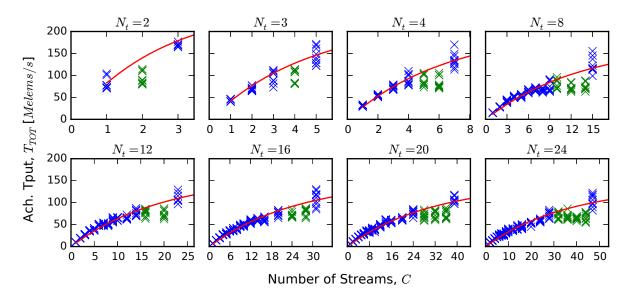

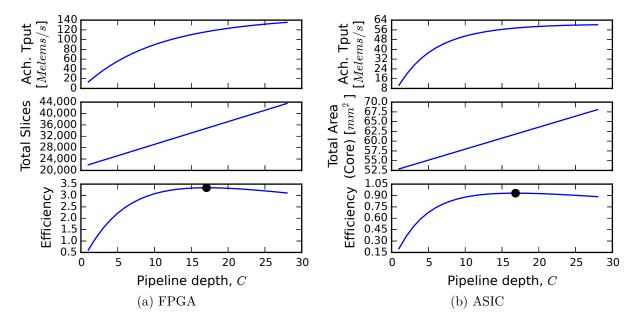

| Figure 5.16: | Calibrated total achievable throughput plot of the virtualized Cosine application with feedback on an FPGA                             | 157 |

| Figure 5.17: | Calibrated total achievable throughput plot of the virtualized Cosine application with feedback on an ASIC                             | 158 |

| Figure 5.18: | Calibrated total slices plot of the virtualized Cosine application with feedback on an FPGA                                            | 159 |

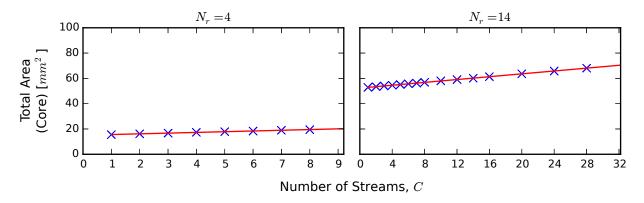

| Figure 5.19: | Calibrated total core area plot of the virtualized Cosine application with feedback on an ASIC                                         | 160 |

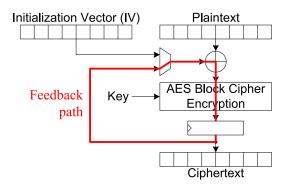

| Figure 5.20: | Block diagram of AES encryption cipher application in the CBC block mode                                                               | 161 |

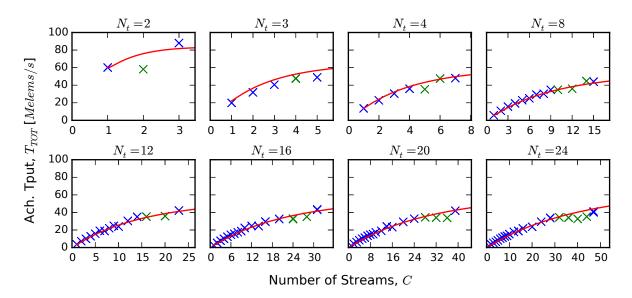

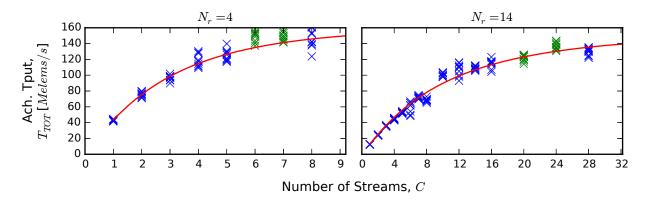

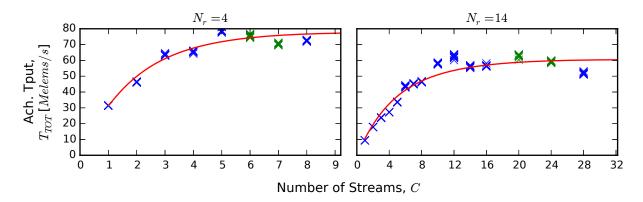

| Figure 5.21: | Calibrated total achievable throughput plot of the virtualized AES encryption cipher application on an FPGA                            | 162 |

| Figure 5.22: | Calibrated total achievable throughput plot of the virtualized AES encryption cipher application on an ASIC                            | 163 |

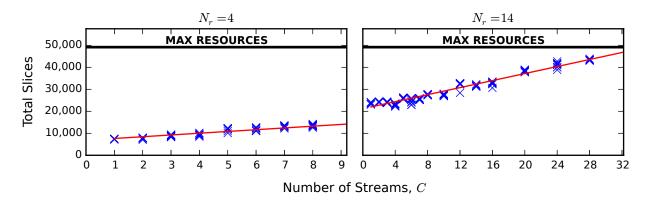

| Figure 5.23: | Calibrated total slices plot of the virtualized AES encryption cipher application on an FPGA                                           | 164 |

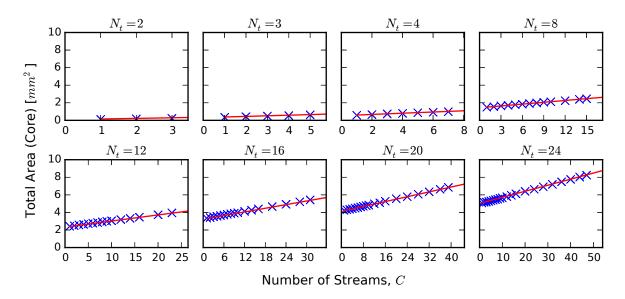

| Figure 5.24: | Calibrated total core area of the virtualized AES encryption cipher application on an ASIC                                             | 165 |

| Figure 5.25: | Block diagram of SHA-2 cryptographic hash application                                                                                  | 166 |

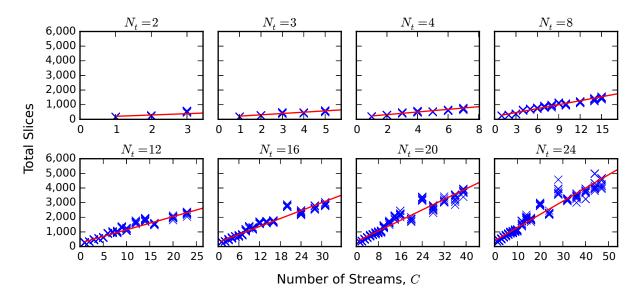

| Figure 5.26: | Calibrated total achievable throughput plot of the virtualized SHA-2 cryptographic hash application on an FPGA for SHA-256 and SHA-512 | 167 |

| Figure 5.27: | Calibrated total slices plot of the virtualized SHA-2 cryptographic hash application on an FPGA for SHA-256 and SHA-512                       | 168 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

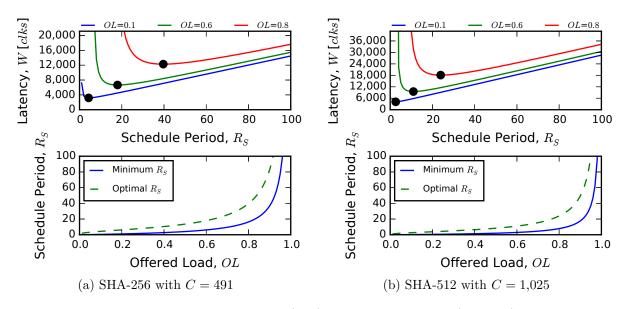

| Figure 5.28: | Analytic latency prediction and optimization plots for MTJ technol-<br>ogy with the SHA application for design scenario 1                     | 171 |

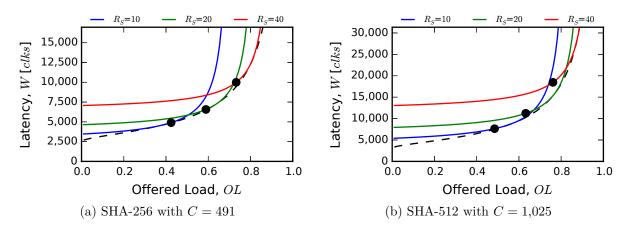

| Figure 5.29: | Analytic latency prediction plots vs. offered load for MTJ technology with the SHA application for design scenario 1                          | 172 |

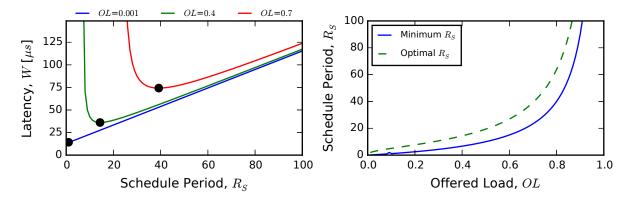

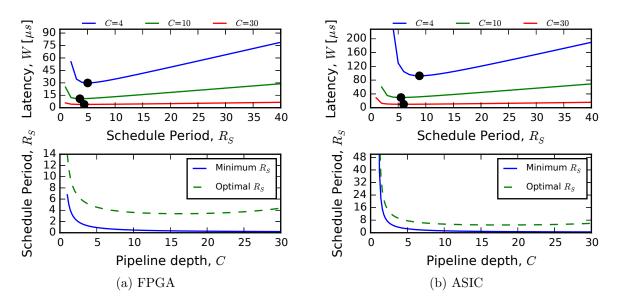

| Figure 5.30: | Analytic latency prediction and optimization plots for FPGA technol-<br>ogy with the COS application for design scenario 1                    | 173 |

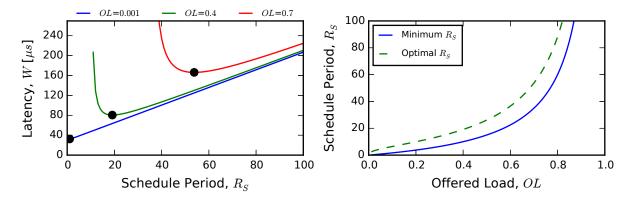

| Figure 5.31: | Analytic latency prediction and optimization plots for ASIC technol-<br>ogy with the AES application for design scenario 1                    | 174 |

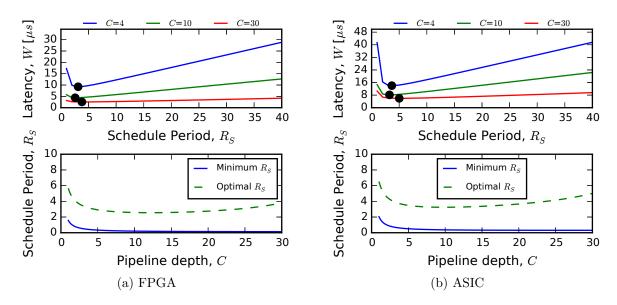

| Figure 5.32: | Analytic latency prediction and optimization plots for the COS appli-<br>cation for design scenario 2                                         | 175 |

| Figure 5.33: | Analytic latency prediction and optimization plots for the AES appli-<br>cation for design scenario 2                                         | 176 |

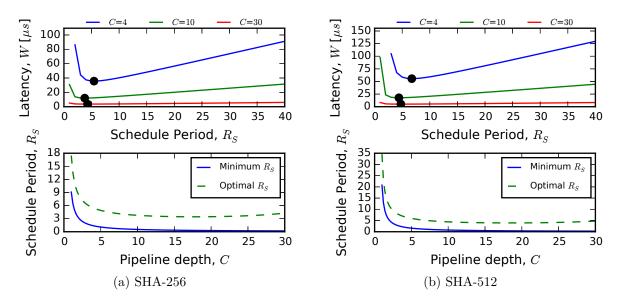

| Figure 5.34: | Analytic latency prediction and optimization plots for the SHA appli-<br>cation in FPGA technology for design scenario 2                      | 177 |

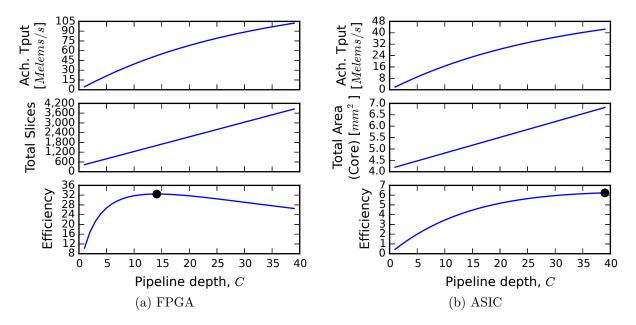

| Figure 5.35: | Analytic total achievable throughput, total slices/area, and efficiency plots for the COS application for design scenario 3                   | 179 |

| Figure 5.36: | Analytic total achievable throughput, total slices/area, and efficiency plots for the AES application for design scenario 3                   | 179 |

| Figure 5.37: | Analytic total achievable throughput, total slices, and efficiency plots for the SHA application in FPGA technology for design scenario $3$ . | 180 |

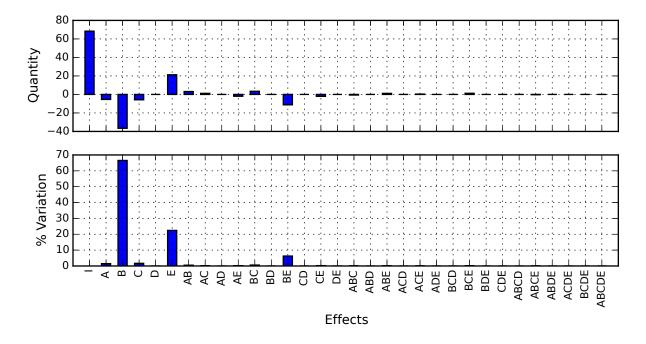

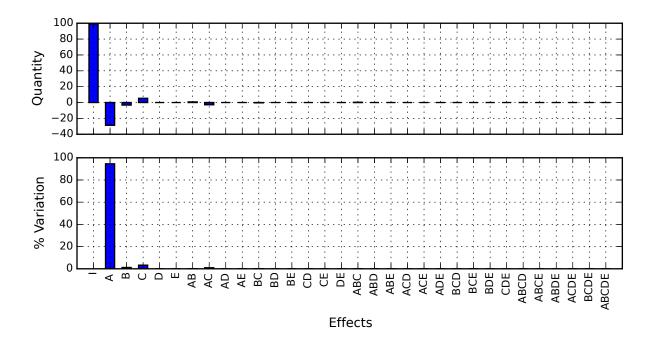

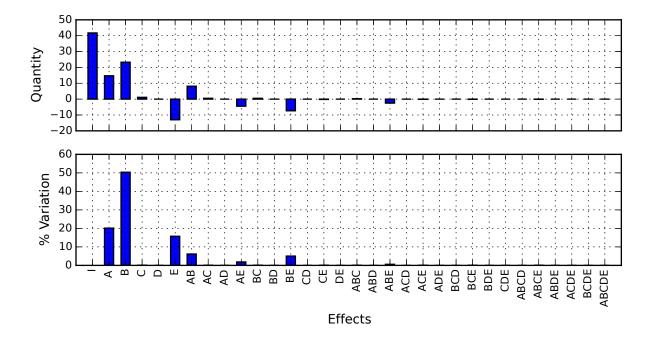

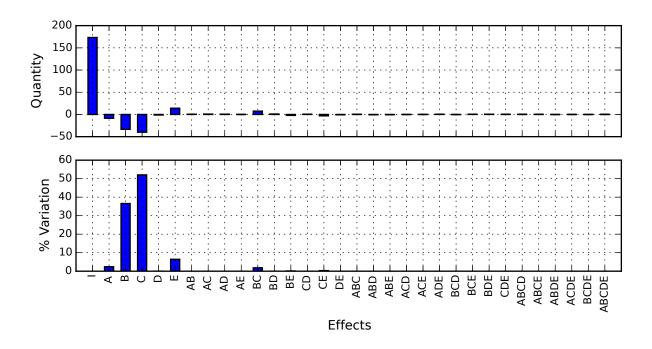

| Figure A.1:  | $2^k$ factorial experimental design for output characteristic $f_{p1}$                                                                        | 200 |

| Figure A.2:  | $2^k$ factorial experimental design for output characteristic $R_3$                                                                           | 200 |

| Figure A.3:  | $2^k$ factorial experimental design for output characteristic $C_{mtj,dp,min}$ .                                                              | 201 |

| Figure A.4:  | $2^k$ factorial experimental design for output characteristic $\sqrt{I_{out,tot,n}^2}$ .                                                      | 201 |

# List of Tables

| Table 3.1: | DC transfer functions from noise source to output                                                             | 31  |

|------------|---------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2: | Resistance at each node                                                                                       | 32  |

| Table 3.3: | Capacitance at each node                                                                                      | 32  |

| Table 3.4: | Validation of node resistances                                                                                | 36  |

| Table 3.5: | Analytical calculation of pole frequencies                                                                    | 36  |

| Table 3.6: | Design guidance for tuning circuit performance                                                                | 39  |

| Table 3.7: | Comparison of relevant process parameters for the R2V read circuit .                                          | 70  |

| Table 3.8: | Rise/fall times (10–90%) and propagation delay of the R2V read circuit                                        | 73  |

| Table 3.9: | Summary of results for the R2V read circuit                                                                   | 78  |

| Table 4.1: | Parameters that can be set                                                                                    | 91  |

| Table 4.2: | Measured propagation delay of the read circuit in the test chip using external and internal input resistances | 104 |

| Table 4.3: | Internal resistor value estimates in each quadrant of the test chip $\ . \ .$                                 | 108 |

| Table 4.4: | $V_{mtj}$ node and output buffer calibration $\ldots \ldots \ldots \ldots \ldots \ldots$                      | 109 |

| Table 4.5: | Summary of the linear range of $V_{bias}$ of the read circuit for each resistor                               | 112 |

| Table 4.6: | Measured operating ranges of the current comparator threshold current                                         | 114 |

| Table 4.7: | Dynamic stability ranges                                                                                      | 116 |

| Table 5.1: | Curve-fit $p$ values of the $t_{CLK}(C)$ model for various distributions and parameters                       | 134 |

| Table 5.2: | Applications implemented using $C$ -slow techniques $\ldots \ldots \ldots$    | 153 |

|------------|-------------------------------------------------------------------------------|-----|

| Table A.1: | Factors used in the $2^k$ factorial experimental design                       | 198 |

| Table A.2: | Metrics used in the $2^k$ factorial experimental design                       | 198 |

| Table A.3: | Summary of the relative dependence of output characteristics to input factors | 202 |

| Table B.1: | Queueing model definition of terms                                            | 203 |

| Table B.2: | Summary of M/D/1 queueing model equations $\ldots \ldots \ldots \ldots$       | 205 |

| Table B.3: | Summary of $M/G/1$ queueing model equations $\ldots \ldots \ldots \ldots$     | 206 |

# List of Abbreviations

| 3M2P   | 3 metal 2 poly                                                                     |

|--------|------------------------------------------------------------------------------------|

| 5M1P   | 5 metal 1 poly                                                                     |

| AES    | Advanced Encryption Standard                                                       |

| API    | Application programming interface                                                  |

| ASIC   | Application-specific integrated circuit                                            |

| BJT    | Bipolar junction transistor                                                        |

| CBC    | Cipher-block chaining                                                              |

| CIMS   | Current-induced magnetic switching                                                 |

| CMOS   | Complementary metal-oxide semiconductor                                            |

| DAC    | Digital-to-analog converter                                                        |

| DRAM   | Dynamic random-access memory                                                       |

| FIFO   | First In, First Out                                                                |

| FIMS   | Field-induced magnetic switching                                                   |

| FPGA   | Field-programmable gate array                                                      |

| FPLD   | Field-programmable logic device                                                    |

| GPU    | Graphics processing unit                                                           |

| IID    | Independent and identically distributed                                            |

| M/D/1  | Markovian, or memoryless, arrival process; Deterministic service process; 1 server |

| M/G/1  | Markovian, or memoryless, arrival process; General service process; 1 server       |

| MOSFET | Metal-oxide semiconductor field-effect transistor                                  |

| MRAM   | Magnetoresistive random-access memory                                              |

| MSC  | Magnetic sense circuit            |

|------|-----------------------------------|

| MTJ  | Magnetic tunnel junction          |

| NMOS | n-channel MOSFET                  |

| PC   | Personal computer                 |

| PCB  | Printed circuit board             |

| PLL  | Phase-locked loop                 |

| PMOS | p-channel MOSFET                  |

| QQ   | Quantile-quantile                 |

| R2V  | Resistance-to-voltage             |

| RA   | Resistance-area                   |

| SHA  | Secure Hash Algorithm             |

| SMT  | Simultaneous multithreading       |

| SPI  | Serial peripheral interface       |

| SRAM | Static random-access memory       |

| STT  | Spin-torque transfer              |

| TMR  | Tunneling magnetoresistance ratio |

| USB  | Universal serial bus              |

|      |                                   |

## Acknowledgments

I am pleased to thank those who made this thesis possible as well as those who have supported me along the way. I am especially grateful to my research advisor Dr. Roger Chamberlain who has provided me with guidance, advice, and help during my years as a graduate student. He has been very patient and encouraging. I am also grateful to my co-advisor Dr. Viktor Gruev for the guidance he has given in anything pertaining to circuit design.

This thesis would not be possible without the support of funding sources. The research was supported by the Air Force Office of Scientific Research (AFOSR) under the Discovery Thrust Program, contract no. FA9550-08-1-0473; the National Science Foundation (NSF) through grants CCF-0427794, CNS-0751212, and CNS-0931693; Exegy, Inc.; and VelociData, Inc.

Thanks to the members of my dissertation committee for agreeing to serve on the committee; our collaborators at Organ State University who introduced us to magnetic tunnel junctions (MTJs) and provided us with a Verilog-A simulation model of the MTJ; Dr. Roch Guérin, the department chair, who steered me towards a vacation model to improve our queueing model; and VelociData with Dr. Joe Lancaster, my peer and supervisor, for the opportunity to work in a summer internship to build the SHA-2 application that is included in this dissertation.

It has been a pleasure also to work with Dr. Raj Jain periodically throughout my studies as a teaching assistant for his class and editor for his book. The knowledge and techniques learned from the class and book have been invaluable in my research work. I have applied them to develop queueing models included in this dissertation and to analyze experimental results. These techniques, no doubt, will continue to be useful in my career, and I am especially grateful for the collaboration I have had with him.

Further, thanks to Washington University, the Computer Science & Engineering department, the staff and faculty, and those who have been supportive of me which include my parents, siblings, relatives, friends, and church community. Thanks also to my academic mentor Dr. George Engel from Southern Illinois University Edwardsville (SIUE) who encouraged me to pursue a Ph.D.

Finally, I would like to express my deepest thanks to God whom I love and who is an integral part of my life. God has been with me constantly throughout my Ph.D. studies and has always been one that I can turn to in prayer. Through prayer, I have daily offered up my work to God for sanctification.

Michael J. Hall

Washington University in Saint Louis May 2015

### Dedicated to the three people who have been tremendous influences in my life: my mother, father, and academic mentor Dr. George Engel.

The people who have been the most influential in my life in pursuing a computer engineering career are my parents Gerald and Janet Hall, whom I dearly love, and my academic mentor Dr. George Engel. I am especially grateful to my parents for all of their love, help, and encouragement. My mother raised me in my Catholic faith and taught me morals and values that guide me through life. My father worked with me and helped me in my projects, and inspired me in my interest in computers. When I came to my parents in 2<sup>nd</sup> grade and asked them to give me math problems to solve, my dad said, "You can write a program to do that." Well, we did just that, and I have been playing with computers ever since. Finally, I thank my academic mentor Dr. George Engel, at SIUE, for encouraging me to go on to pursue a Ph.D.

#### ABSTRACT OF THE DISSERTATION

Utilizing Magnetic Tunnel Junction Devices in Digital Systems by Michael J. Hall Doctor of Philosophy in Computer Engineering Washington University in St. Louis, 2015 Professor Roger D. Chamberlain, Chair

The research described in this dissertation is motivated by the desire to effectively utilize magnetic tunnel junctions (MTJs) in digital systems. We explore two aspects of this: (1) a read circuit useful for global clocking and magnetologic, and (2) hardware virtualization that utilizes the deeply-pipelined nature of magnetologic.

In the first aspect, a read circuit is used to sense the state of an MTJ (low or high resistance) and produce a logic output that represents this state. With global clocking, an external magnetic field combined with on-chip MTJs is used as an alternative mechanism for distributing the clock signal across the chip. With magnetologic, logic is evaluated with MTJs that must be sensed by a read circuit and used to drive downstream logic. For these two uses, we develop a resistance-to-voltage (R2V) read circuit to sense MTJ resistance and produce a logic voltage output. We design and fabricate a prototype test chip in the 3 metal 2 poly  $0.5 \,\mu$ m process for testing the R2V read circuit and experimentally validating its correctness. Using a clocked low/high resistor pair, we show that the read circuit can correctly detect the input resistance and produce the desired square wave output. The read circuit speed is measured to operate correctly up to 48 MHz. The input node is relatively insensitive to node capacitance and can handle up to 10s of pF of capacitance without changing the bandwidth of the circuit. In the second aspect, hardware virtualization is a technique by which deeply-pipelined circuits that have feedback can be utilized. MTJs have the potential to act as state in a magnetologic circuit which may result in a deep pipeline. Streams of computation are then context switched into the hardware logic, allowing them to share hardware resources and more fully utilize the pipeline stages of the logic. While applicable to magnetologic using MTJs, virtualization is also applicable to traditional logic technologies like CMOS. Our investigation targets MTJs, FPGAs, and ASICs. We develop M/D/1 and M/G/1 queueing models of the performance of virtualized hardware with secondary memory using a fixed, hierarchical, round-robin schedule that predict average throughput, latency, and queue occupancy in the system. We develop three *C*-slow applications and calibrate them to a clock and resource model for FPGA and ASIC technologies. Last, using the M/G/1 model, we predict throughput, latency, and resource usage for MTJ, FPGA, and ASIC technologies. We show three design scenarios illustrating ways in which to use the model.

## Chapter 1

## Introduction

Thin-film magnetic devices based on the magnetic tunnel junction (MTJ) are actively being researched for applications in memory [1], field-programmable gate arrays (FPGAs) [2], and logic computation [3], and have been developed as early as the 1980s [4]. These devices can store information non-volatilely in a magnetic field that retains its value across power cycles. Fabrication of these devices is compatible with the complementary metal-oxide semiconductor (CMOS) process allowing them to be integrated on a CMOS chip. Integration improves area efficiency, lowers wire resistance and capacitance, and reduces power. Further, these devices can scale down with the CMOS process and have been shown to be fabricated in a 45 nm process node with a size of 40 nm along the short axis and an aspect ratio, long vs. short, of  $\sim 2.5$  to 3 [5]. The write endurance, or the number of times a stored value can change without failure in the device, is practically infinite. They also have potentially short read and write times, allowing stored data to be accessed quickly [6].

A basic illustration of the MTJ device is shown in Figure 1.1 with a write-strap that programs the MTJ using an induced magnetic field. The MTJ device is constructed using two ferromagnetic layers separated by a thin insulator such as MgO that is the tunnel barrier. The top ferromagnetic layer, called the free layer, can have a magnetic orientation in one of

Figure 1.1: A magnetic tunnel junction (MTJ) device that encodes state information in the magnetic orientation of the free layer. The state is programmed with a current (+I) and accessed as a resistance  $(R_{mtj})$  between the two electrodes.

two directions as indicated in the figure. The bottom ferromagnetic layer, called the fixed layer, has its magnetic orientation in one direction that is pinned during the manufacturing process. The resistance,  $R_{mtj}$ , as seen across the electrodes of the device, is dependent on the magnetic orientation of the free layer relative to the fixed layer. When the orientations of both layers are parallel (in the same direction), the resistance seen through the MTJ is low ( $R_L$ ). In contrast, when the orientations of both layers are anti-parallel (in opposite directions), the resistance seen through the MTJ is high ( $R_H$ ). Thus, the state is accessed as a resistance. The orientation of the free layer can be set by applying a magnetic field of sufficient strength through the free layer. The magnetic field can be generated externally or induced by sourcing a current through the write-strap [4].

### 1.1 Uses of MTJs

The first use of MTJs is memory. Memory technology has developed rapidly to serve different needs: static random-access memory (SRAM) for high-speed data storage, dynamic randomaccess memory (DRAM) for low-cost data storage, and Flash memory for high-density, nonvolatile data storage. All three technologies have their advantages and disadvantages. Researchers are working to develop a universal memory technology that combines the best aspects of all three. That is, a memory that is non-volatile, has a high-write endurance, low read/write energy, and high read/write speed [7]. Magnetoresistive random-access memory (MRAM) using MTJs is one such promising universal memory technology [8, 9, 10]. MRAM is actively being researched and improved; Everspin Technologies, a spin-off company from Freescale Semiconductor formed in 2008, is actively commercializing MRAM memory and is today selling 64 Mb MRAM chips [11]. MRAM circuits typically use current conveyors for readout of the MRAM cells. While there is still research to be accomplished in the area of MRAM memory design, that is not the focus of this dissertation.

The second use of MTJs is configuration memory in FPGAs. FPGAs currently use SRAM cells to store the programmed configuration data used to configure the lookup tables in the reconfigurable logic. However, these memory cells are volatile and lose their data values across power cycles, requiring them be reprogrammed at power-up. If they are replaced with MRAM cells, then the configuration memory will be able to retain its data values across power cycles due to the non-volatile nature of MRAM. This consequently means that the configuration memory will only need to be programmed once [2]. The MRAM cells are based on the same structure as the SRAM cells. They use an SRAM-based sense amplifier, which is an unbalanced magnetic flip-flop in voltage-mode, to sense a stored data value from a

differential pair of MTJs [12]. As with MRAM, this dissertation will not investigate the use of MTJs as configuration memory in FPGAs.

The third use of MTJs is clocking which is a new use of MTJs not previously proposed in the literature. Synchronous logic circuits in digital systems need to receive a common clock signal at the same time across a chip. Clock distribution trees are the predominant way to distribute the clock from a single source. They use a tree-like structure and clock buffers to balance the signal propagation of the clock to every flip-flop in synchronous logic circuits. On modern processors, clock power is significant, consuming on the order of 25% of total chip power [13]. Clock skew with the clock distribution tree can be significant as the clock is driven at higher frequencies, contributing to 3.8% of the clock period in the Cell processor running at 3.2 GHz [13]. Replacing the clock distribution tree with an equivalent mechanism that can distribute the clock to all flip-flops has the potential to yield benefits in area, speed, and on-chip power dissipation.

A global external magnetic field combined with on-chip MTJs is an alternative mechanism for distributing the clock across a chip as illustrated in Figure 1.2. We proposed this in [14]. This is similar to optical clock distribution in free-space as proposed in the literature [15]. A resistance-to-voltage read circuit is necessary for sensing MTJ resistance state. The MTJs, when distributed across the chip, sense a global magnetic field, and, using a read circuit, produce local clock signals that drive nearby synchronous logic circuits. In this way, a global clock distribution tree is not needed, however, local clock distribution is still necessary. This should result in reduced on-chip power dissipation and area. If the global clock is relatively insensitive to process variations in the MTJ devices and corresponding read circuits such that the jitter between local clocks is small, then clock skew will decrease, resulting in increased circuit speed. The external magnetic field generated off-chip, however, will consume power. It is an open question as to whether or not there is a net power benefit in the system. This

Figure 1.2: Magnetic clocking across a chip using an external magnetic field. A chip is partitioned into regions that contain a Magnetic Clock Generator (MG) and a Digital Logic (DL) region. The MG contains an MTJ and a read circuit that senses the external field and generates a local clock. The local clock drives nearby digital logic. Because the local clocks are synchronous, interconnections can be made from any DL region to any other DL region (only regular connections are illustrated).

dissertation will investigate the design of the resistance-to-voltage read circuit and present experimental results from a prototype test chip. The read circuit can be used to produce local clock signals generated from an external oscillating magnetic field. This dissertation will also describe the design of the prototype chip to be used for testing global clocking. However, due to the inaccessibility of obtaining MTJs, this dissertation will not present experimental results demonstrating a functional globally clocked chip.

The fourth use of MTJs is logic. Logic circuits designed using MTJs depend on the type of MTJ device used. These types include field-induced, toggle, thermally-assisted, and spin-torque transfer [4]. Several approaches have been proposed in the literature for constructing fundamental magnetologic circuits (e.g. gates) including device threshold logic [16], serially-connected devices for complex logic [3, 12, 17, 18], cascading device logic [19], and resistive-based lookup tables with MTJ storage elements [20]. This dissertation will not investigate how to build fundamental magnetologic circuits.

Figure 1.3: Pipelined magnetologic circuit with feedback. Four MTJ logic gates are shown, each acting as a pipeline stage with state. It takes 4 clock cycles to compute a single result with the feedback path.

There are commonalities in the way fundamental magnetologic circuits are built. First, each MTJ device acts as a latch to whatever data is written to it. This gives it the potential to act as state in the pipeline stage of a logic circuit as shown in Figure 1.3. We want to exploit the latching property of fundamental magnetologic circuits for constructing deeply-pipelined logic. Second, data is accessed as a resistance between the terminals of the MTJs. A read circuit, therefore, is commonly needed to sense this resistance.

To exploit the deeply-pipelined nature of magnetologic circuits when feedback is present, context switching can be used to fully utilize the pipeline stages of the deeply-pipelined logic, allowing them to compute multiple data streams. This allows the hardware (a.k.a. the logic) to be virtualized, meaning that each data stream shares the hardware resource. The circuits are sequential logic circuits with pipelined combinational logic. The pipelined combinational logic adds latency and decreases single stream throughput since it takes multiple clock cycles (corresponding to the number of pipeline stages) to compute a single result and feed it back to the input. If the number of pipeline stages is C, then this circuit is said to be Cslowed [21] since a single computation runs C times slower. C-slow is a technique described by Leiserson by which every register is replaced by C registers and then retimed to balance the registers throughout the combinational logic. Application of the C-slow technique is shown in Figure 1.4. Exploiting this characteristic allows processing multiple different contexts or data streams in a fine-grain way using the same hardware logic. The number of fine-grain

Figure 1.4: Application of the C-slow technique to a non-pipelined circuit. The non-pipelined sequential circuit is shown on the left. C-slow is applied to this circuit by replacing the register with C registers and distributing it amongst the combinational logic (CL) shown on the right. x is the input, y is the feedback, and z is the output.

contexts supported equals the pipeline depth. Context switching the hardware can utilize all the pipeline stages, and if they are evenly spaced, improve the clock frequency as well.

Virtualization of the hardware is akin to simultaneous multithreading (SMT) in a processor where fast context switches allow executing multiple threads simultaneously on the hardware, also sharing the hardware resource [22]. Graphics processing units (GPUs) regularly use this technique, frequently supporting large numbers of threads per core. Asymptotic models that employ this technique have been introduced by Ma et al. [23, 24]. This dissertation will investigate hardware virtualization using context switching as a way to exploit the deeplypipelined nature of magnetologic circuits.

### 1.2 Virtualized hardware

Virtualized hardware using context switching is more widely applicable than its use in magnetologic. It can also be used in existing FPGA and ASIC technologies. Context switching is a technique by which hardware resources are reused to support processing multiple computations. It can be fine- or coarse-grain. Context switching using deeply-pipelined or C-slowed logic circuits is fine-grain. Context switching using a secondary memory and explicitly swapping contexts in and out at an infrequent rate is coarse-grain.

There are three main benefits of context switching hardware: (1) the ability to reuse hardware resources for doing computation on multiple data streams, (2) an increase in the clock frequency when the combinational logic is evenly pipelined, and (3) an increase in the total throughput of all computations when total hardware resources are limited. For the first benefit, reusing hardware for computation is beneficial when available resources for a design are limited such as on an FPGA or when the cost to build hardware is high such as on an ASIC. For the second benefit, the clock frequency increases because the combinational logic is broken up more finely, allowing signals to propagate faster between pipeline stages. For the third benefit, total throughput increases because more computation can be done on a fixed amount of resources than could otherwise be done and as the clock frequency increases the throughput also increases.

This dissertation will investigate the design of virtualized hardware, model its performance, and optimize a schedule for context switching. The model will predict circuit performance and resource usage, and provide guidance in selecting design parameters.

### **1.3** List of contributions

In this dissertation, the following contributions are made:

- Noise analysis of a basic current-mode read circuit [25] and design guidance of performance tradeoffs

- Transistor sizing equations of several different current conveyor structures

- Design, layout, and simulation of a resistance-to-voltage (R2V) read circuit [26]

- Design, layout, and fabrication of a prototype test chip for testing the R2V read circuit and aspects of global clocking

- Design, layout, and fabrication of a printed circuit board (PCB) for testing the prototype chip

- Construction of the PCB and test setup for testing the prototype chip

- Experimental results and characterizations of the R2V read circuit in the prototype chip

- Automated tool scripts and infrastructure for synthesizing virtualized hardware logic circuits and exploring the design space

- Development of a clock period model based on a randomized model of logic delay

- Development of M/D/1 [27, 28] and M/G/1 queueing models for predicting performance in virtualized hardware logic circuits

- Design of 3 C-slow applications for virtualization

- Synthetic cosine application implemented via a Taylor series expansion with added feedback

- Advanced Encryption Standard (AES) cipher in cipher-block chaining (CBC) mode for encryption [27]

- Secure Hash Algorithm (SHA-2) with 256 and 512 bit digests (SHA-256 and SHA-512)

- Calibration of the 3 C-slow applications to the clock period model and a resource model

Demonstration of ways to use the performance model (queueing model + clock period model + resource model) to predict performance in virtualized hardware logic circuits

[27]

#### 1.4 Outline of the dissertation

The outline of the dissertation is as follows. Chapter 2 provides relevant background information about MTJ devices, MTJ read circuits, current conveyor operation, magnetologic circuits, *C*-slow transformation, hardware virtualization, queueing notation, and vacation models. Chapter 3 describes MTJ read circuit theory including a noise analysis of a currentmode read circuit, transistor sizing equations for several different current conveyor structures, and the design and simulation of a resistance-to-voltage (R2V) read circuit. Chapter 4 describes MTJ read circuit experimentation including the design of a prototype system and experimental results of the R2V read circuit in the prototype system. Chapter 5 investigates hardware virtualization which includes the design, modeling, and optimization of virtualized hardware logic circuits, and presents results with three example applications. Last, Chapter 6 presents conclusions and future work.

## Chapter 2

### **Background and Related Work**

### 2.1 MTJ devices

The magnetic tunnel junction (MTJ) device, illustrated in Figure 2.1, is a small thin-film magnetic device that is constructed using two ferromagnetic layers such as CoFeB (top layer) and CoFe (bottom layer) separated by a thin insulator such as MgO that is the tunnel barrier [4]. The figure is similar to the one illustrated in Figure 1.1, but without the write strap. The ferromagnetic layers can take on one of two magnetic orientations. Usually one of the layers is pinned during fabrication so that its magnetic orientation is fixed while the other layer is free to rotate. These layers are called the fixed layer and free layer, respectively. Pinning is done by placing an antiferromagnetic layer below the fixed layer (not shown) constructed using a material such as IrMn that prevents the fixed layer from switching at ambient temperature [4]. The free layer effectively stores one bit of state information determined by its magnetic orientation. Since it requires no power to sustain a particular magnetic orientation, the state information is non-volatile.

Reading the MTJ device state can be accomplished by sensing a resistance output. The output is sensed via the two electrodes of the device whose resistance is determined by the

Figure 2.1: Magnetic tunnel junction (MTJ) device. Basic construction consists of two ferromagnetic layers (free and fixed layer) and an insulator. The fixed layer magnetic orientation is pinned whereas the free layer magnetic orientation is free to switch. For field-induced magnetic switching (FIMS), an additional write strap may be added above or below the MTJ. Current passing through the write strap induces a magnetic field to switch the free layer. For current-induced magnetic switching (CIMS), current instead passes through the MTJ device itself to switch the free layer. The state of the device is accessed as a resistance seen looking between the two electrodes.

relative magnetic orientations of the free and fixed layers. A device is characterized by its resistance-area (RA) product, which can range from  $10 \Omega \cdot \mu m^2$  [29] to  $7.6 k\Omega \cdot \mu m^2$  [1]. When the magnetic orientations are parallel, that is, oriented in the same direction, the resistance is low ( $R_L$ ). Likewise, when they are anti-parallel, that is, oriented in opposite directions, the resistance is high ( $R_H$ ). Sensing this low/high resistance provides a means for reading the device state. A tunneling magnetoresistance ratio (TMR) is defined as  $TMR = \frac{R_H - R_L}{R_L}$ that characterizes the separation between resistance states. The TMR is dependent on the bias voltage,  $V_{bias}$ , across the electrodes of the device. Large bias voltages result in small TMR and a high rate of device failure [4].

Writing to the MTJ device can be done via one of two basic write mechanisms: field-induced magnetic switching (FIMS), and current-induced magnetic switching (CIMS). With FIMS, a write strap is added over the MTJ device and bidirectional current is applied through the write strap. This induces a magnetic field that permeates through the free layer and sets its magnetic orientation. The fixed layer, however, does not switch because the pinning layer below it prevents it from doing so. The applied current has to exceed the switching threshold of the free layer. Alternatively, this field might be induced by an externally generated global

field. With CIMS, a bidirectional current is applied directly through the electrodes of the MTJ device which becomes spin-polarized and sets the magnetic orientation of the free layer. A critical current has to be exceeded for switching to occur [4]. The field strength needed to switch an MTJ is at least 4 times the Earth's geomagnetic field [14].

Field-induced magnetic switching (FIMS) devices: There are three different types of MTJ devices that use the FIMS write mechanism: conventional, toggle, and thermallyassisted [4]. Conventional devices frequently have two write straps (easy and hard axis) that cross each other at a 90° angle. The hard axis lowers the threshold for magnetic switching, and the easy axis magnetically switches the free layer. Toggle devices are similar to conventional devices, but are constructed to prevent a device from being only half-selected (where a field is applied along one axis but not the other). This is done by performing a 4-phase rotation to toggle the device. Thermally-assisted devices, on the other hand, are constructed to lower the write energy required by preheating the device with a heat current prior to inducing a field to switch the free layer.

**Current-induced magnetic switching (CIMS) devices:** Spin-torque transfer (STT) devices utilize the CIMS write mechanism [4, 10]. They have a few benefits that do not exist in FIMS devices. One, STT devices do not suffer from cross-talk between fields, and therefore, they can be placed closer together for greater density. Two, STT devices scale well with power. As the process dimensions decrease, the power required to write to the device decreases as well. Many STT devices have two terminals which are used for both reading and writing. For reading, a large MTJ resistance is desirable for determining its state. For writing, a small MTJ resistance is desirable so that the voltage drop across the device due to the write current is small. A three-terminal STT device was constructed by Braganca et al. [30] that achieves this by providing a low-resistance write terminal and a

Figure 2.2: Read circuit block diagram for an MTJ. The read circuit senses an MTJ resistance and compares this to a reference to produce an output.

high-resistance read terminal. According to their simulations, the 3-terminal STT device requires approximately the same write current as a 2-terminal STT device, but with a lower voltage drop.

### 2.2 MTJ read circuits

An MTJ device is accessed as a resistance as seen through its tunnel junction. This resistance represents the logic state of the device, whether low or high. In order to read the state, a read circuit is necessary to convert the resistance into a corresponding logic voltage output. A read circuit can be designed in many ways. It can be voltage- or current-clamped, use a voltage- or current-mode comparator, use a single MTJ with a reference or a pair of differential MTJs, and be sampled or continuous in time. Several read circuits have been designed in the literature to accomplish this task. We describe several below. A block diagram for a basic read circuit is shown in Figure 2.2.

Current conveyor with voltage comparator [31]: This read circuit uses a differential current conveyor with a voltage comparator for sensing data in an MRAM cell. There are two inputs to the differential current conveyor: an MTJ device with a low/high resistance, and a reference with a midpoint resistance. The current conveyor clamps both inputs to a fixed voltage and produces currents according to Ohm's law  $(I = \frac{V}{R})$ . These currents are then converted to voltages and compared by a voltage comparator.

Current conveyor with current comparator [32]: This read circuit is similar to the one in [31]. It uses a differential current conveyor with a current comparator for sensing data in an MRAM cell and is designed to be low power. There are two inputs to the differential current conveyor: an MTJ device with a low/high resistance and a reference with a midpoint resistance. The current conveyor clamps both inputs to a fixed voltage and produces currents according to Ohm's law. These currents are then compared by a current comparator to produce the final voltage output. This is the type of MTJ read circuit that is investigated in this dissertation.

Voltage-mode sense amplifier [12]: This read circuit is used to compare networks of MTJ devices in a structure called the basic field-programmable logic device (FPLD). It works by first applying a constant sense current,  $I_{sens}$ , to both the positive and negative terminals of the sense amplifier in the FPLD. This then produces corresponding terminal voltages across the MTJ networks according to Ohm's law. Comparing these terminal voltages, the sense amplifier then produces a final voltage output. The FPLD structure is used to construct complex Boolean logic expressions.

**Differential unbalanced flip-flop circuit** [12]: This read circuit is a reconfigurable static latch cell that consists of a differential pair of inverters connected with feedback to form a flip-flop. This is based on the static random-access memory (SRAM) cell circuit [33]. A complementary pair of MTJs are connected in series with the inverters to ground. This causes the flip-flop to be unbalanced due to the difference in MTJ resistance of the

complementary pair. A sense transistor, connected between the inverter outputs, shorts them together when closed and senses the MTJs when opened. When the sense transistor is opened, the inverters swing low and high based on the relative MTJ resistances. This samples the MTJ state discretely in time.

# 2.3 Current conveyor operation

The current conveyor, shown in a black box representation in Figure 2.3a, is a 3-terminal circuit introduced by Smith and Sedra [34] that provides current amplification with unity gain. A voltage V applied at Y appears at X, causing current I to flow out at X. In a dual manner, the same current I also flows out at Y. The current at X is also conveyed out at Z with high impedance. This circuit thus allows current to be conveyed from one source (X) to another (Z) while holding the voltage potential constant (at X).

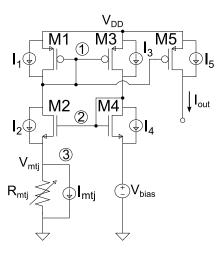

An implementation of the basic current conveyor circuit using complementary metal-oxide semiconductor (CMOS) transistors [35, 36] is shown in Figure 2.3b which is used in our design of the MTJ read circuit for sensing MTJ resistance and producing an output current. The current conveyor is a feedback circuit consisting of two current mirror circuits between the left and middle branches connected together in a feedback loop and a high impedance output current out from the right branch. Transistors  $M_{1,3,5}$  form the PMOS current mirror circuits and transistors  $M_{2,4}$  form the NMOS current mirror circuit. The supplied  $V_{ref}$  voltage then clamps the  $V_{in}$  voltage to  $V_{ref}$  potential over the input resistance  $R_{in}$ . This in turn produces a current  $I_{in}$  through the left branch according to Ohm's Law that is inversely-proportional to the input resistance by the equation  $I_{in} = V_{ref}/R_{in}$ . The currents are mirrored between each branch (left, middle, and right) with a 1:1 gain which is achieved by matching the width

Figure 2.3: Basic current conveyor.

and length of the transistors in the current mirrors [37], thus making  $\left(\frac{W}{L}\right)_1 = \left(\frac{W}{L}\right)_3 = \left(\frac{W}{L}\right)_5$ ,  $\left(\frac{W}{L}\right)_2 = \left(\frac{W}{L}\right)_4$ , and  $I_{in} = I_{sd,1} = I_{sd,3} = I_{sd,5} = I_{ds,2} = I_{ds,4}$ .

# 2.4 Magnetologic circuits

There are several different ways to construct fundamental magnetologic circuits (e.g. basic gates), some of which may require CMOS support circuitry. These include device threshold logic, serially-connected devices for complex logic, cascading device logic, and lookup tables. Each approach is discussed separately; however, they are not all mutually exclusive. Some can be combined and used together.

**Device threshold logic** [12, 16]: This is a way to build simple magnetologic gates using threshold logic. Inputs combine as either currents or fields to switch the free layer of the device when the device threshold is exceeded. Since the free layer is only conditionally switched, threshold logic is implemented using a preset and evaluate phase. In the preset

phase, the MTJ device is preset to a value that selects the logic function to be evaluated (such as AND or OR). Then, in the evaluate phase, the logic is evaluated using threshold logic. The state of the free layer then represents the logic output which is accessed as a resistance. Device threshold logic needs read/write circuits to connect between gates.

Serially-connected devices for complex logic [12, 18, 38]: This is a way to build complex magnetologic gates using CMOS support circuitry. It is constructed using two strings of MTJ devices whose output resistances are serially connected to the V+ and Vnodes of a voltage sense amplifier. Logic inputs to this complex gate drive the MTJ devices' write lines to set their state. Based on their state, logic is evaluated when the strings of devices are sensed. A Boolean expression representing the logic function can be derived from the equation of the voltage sense amplifier. Simple logic functions can be implemented in multiple ways from this complex Boolean expression. Further, serially-connected devices can be combined with device threshold logic to construct even more complex logic gates [18].

**Cascaded device logic** [19]: This is a way to build simple magnetologic gates without CMOS support circuitry. It relies on device threshold logic with 3-terminal spin-torque transfer (STT) devices. With cascaded device logic, the read current of one device acts as the write current to the next device. Since device threshold logic conditionally switches the free-layer, cascaded device logic requires preset and evaluate phases to operate. Simple logic gates such as AND, OR, NAND, and NOR can be implemented.

Lookup tables [20]: This is a way to build reconfigurable magnetologic gates using CMOS support circuitry to implement arbitrary logic functions from a truth table. The truth table is specified by the values stored in MTJ devices and looked up via a multiplexor tree. The

multiplexer tree selects one of the devices based on a given input and accesses the device's resistance which is then sensed by a sense amplifier. The sense amplifier then produces the final output value. These lookup tables can be used in reconfigurable logic arrays such as field-programmable gate arrays (FPGAs) and in resistive computing [39].

# 2.5 C-slow transformation

C-slow is a transformation described by Leiserson [21] whereby every register in a digital logic circuit is replaced by C registers as illustrated in Figure 1.4. This allows sequential logic circuits, which have feedback paths, to be pipelined and retimed. Retiming is a technique for improving the clock frequency of a circuit by moving pipeline registers forward and backwards through the combinational logic to shorten the critical path of the circuit. Retiming a C-slowed circuit can theoretically give up to C times improvement in the clock frequency.

C-slow circuits, by their very nature, are multi-processing. They have C pipeline registers in the feedback path allowing them to process multiple data streams interleaved into a single stream. It takes C clock cycles to compute an output for a single data stream and to feed it back to the input to be processed with the next data value. Multiple data streams can be processed at different stages in the pipeline, allowing the pipeline to be more fully utilized. For a single stream, the throughput, measured as data values per clock cycle, will be C times slower (in terms of clock cycles) than before the C-slow transformation. For all streams combined, the total throughput will be the same.

The design of C-slow circuits has several constraints relative to traditional synchronous circuit designs [40]. They cannot use asynchronous sets or resets. They cannot use a global synchronous reset as it creates too many constraints in the retiming process. And, they

cannot use the enable input of a flip-flop. Rather, reset and enable can be expressed as logic, allowing contexts to still be reset and enabled.