#### Washington University in St. Louis

### Washington University Open Scholarship

McKelvey School of Engineering Theses & Dissertations

McKelvey School of Engineering

Winter 12-15-2013

### Dynamic Thermal and Power Management: From Computers to **Buildings**

Yong Fu Washington University in St. Louis

Follow this and additional works at: https://openscholarship.wustl.edu/eng\_etds

Part of the Engineering Commons

#### **Recommended Citation**

Fu, Yong, "Dynamic Thermal and Power Management: From Computers to Buildings" (2013). McKelvey School of Engineering Theses & Dissertations. 24.

https://openscholarship.wustl.edu/eng\_etds/24

This Dissertation is brought to you for free and open access by the McKelvey School of Engineering at Washington University Open Scholarship. It has been accepted for inclusion in McKelvey School of Engineering Theses & Dissertations by an authorized administrator of Washington University Open Scholarship. For more information, please contact digital@wumail.wustl.edu.

#### WASHINGTON UNIVERSITY IN ST. LOUIS

School of Engineering and Applied Science

Department of Computer Science and Engineering

Dissertation Examination Committee:

Chenyang Lu, Chair

Ron K. Cytron

Christopher D. Gill

Humberto Gonzalez

Anne Holler

Raj Jain

Dynamic Thermal and Power Control for Computing Systems

by

Yong Fu

A dissertation presented to the Graduate School of Arts and Sciences of Washington University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

December 2013 Saint Louis, Missouri

### Contents

| Li           | st of | Figures                                                            |

|--------------|-------|--------------------------------------------------------------------|

| Li           | st of | Tables ix                                                          |

| $\mathbf{A}$ | ckno  | wledgments                                                         |

| D            | edica | ${f x}$ ion                                                        |

| $\mathbf{A}$ | bstra | $\mathbf{x}$                                                       |

| 1            | Intr  | $\operatorname{roduction}$                                         |

|              | 1.1   | Feedback Thermal Management for Real-time systems                  |

|              | 1.2   | CloudPowerCap                                                      |

|              | 1.3   | Contributions                                                      |

| <b>2</b>     | Fee   | dback Thermal Management for Real-time Systems on Single Core Pro- |

|              | cess  | sors                                                               |

|              | 2.1   | Introduction                                                       |

|              | 2.2   | Related Work                                                       |

|              | 2.3   | Problem Formulation                                                |

|              |       | 2.3.1 System Models                                                |

|              |       | 2.3.2 Design Goals                                                 |

|              | 2.4   | Overview of TCUB                                                   |

|              | 2.5   | Thermal Control Design and Analysis                                |

|              |       | 2.5.1 Dynamic Model for Thermal Control                            |

|              |       | 2.5.2 Thermal Controller Design                                    |

|              |       | 2.5.3 Stability Analysis                                           |

|              |       | 2.5.4 Sensitivity Analysis                                         |

|              | 26    | Evaluation 25                                                      |

|   |     | 2.6.1 Power Deviation                                               | 27 |

|---|-----|---------------------------------------------------------------------|----|

|   |     | 2.6.2 Execution Time Variation                                      | 28 |

|   |     | 2.6.3 Robustness of TCUB                                            | 32 |

|   |     | 2.6.4 Thermal Fault                                                 | 33 |

|   |     | 2.6.5 Ambient Temperature Variation                                 | 34 |

|   | 2.7 | Summary                                                             | 36 |

| 3 | Fee | dback Thermal Control for Real-time Systems on Mulitcore Processors | 37 |

|   | 3.1 | Introduction                                                        | 37 |

|   | 3.2 | Problem Formulation                                                 | 39 |

|   | 3.3 | Overview of RT-MTC                                                  | 41 |

|   | 3.4 | Thermal Dynamic Model                                               | 42 |

|   |     | 3.4.1 Power Model                                                   | 42 |

|   |     | 3.4.2 Pulse Width Modulation (PWM)                                  | 43 |

|   |     | 3.4.3 Thermal Dynamic Model                                         | 44 |

|   | 3.5 | Control Design                                                      | 46 |

|   |     | 3.5.1 Stability Analysis and Control Design                         | 46 |

|   | 3.6 | Implementation of RT-MTC                                            | 48 |

|   | 3.7 | Evaluation                                                          | 49 |

|   |     | 3.7.1 Experiments                                                   | 49 |

|   |     | 3.7.2 Simulation                                                    | 53 |

|   | 3.8 | Related Work                                                        | 61 |

|   | 3.9 | Summary                                                             | 62 |

| 4 | Rob | oust Control-theoretic Thermal Balancing for Server Clusters        | 63 |

|   | 4.1 | Introduction                                                        | 63 |

|   | 4.2 | Problem Formulation                                                 | 65 |

|   |     | 4.2.1 System model                                                  | 65 |

|   |     | 4.2.2 Dynamic Model for Thermal Balancing                           | 66 |

|   |     | 4.2.3 Thermal Balancing Objective                                   | 68 |

|   | 4.3 | CTB Design and Analysis                                             | 68 |

|   |     |                                                                     | 69 |

|   |     | 4.3.2 Control Design of CTB-T                                       | 71 |

|   |     | 4.3.3 Control Design of CTB-UT                                      | 72 |

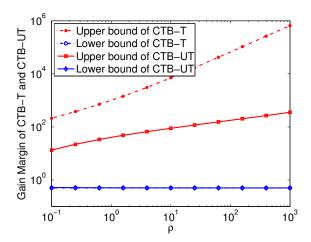

|   |     | 4.3.4 Stability and Robustness                                                                |

|---|-----|-----------------------------------------------------------------------------------------------|

|   | 4.4 | Evaluation                                                                                    |

|   |     | 4.4.1 Simulation Setup                                                                        |

|   |     | 4.4.2 Baseline Algorithms                                                                     |

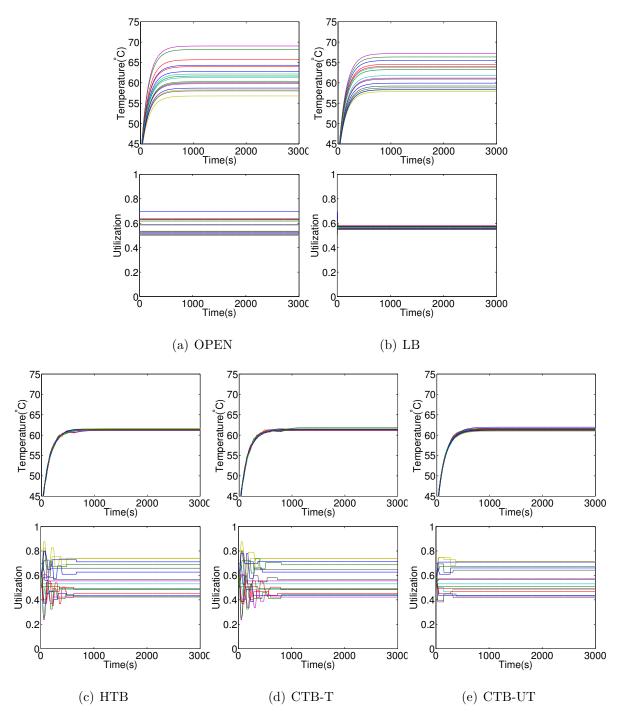

|   |     | 4.4.3 Effect of Thermal Balancing                                                             |

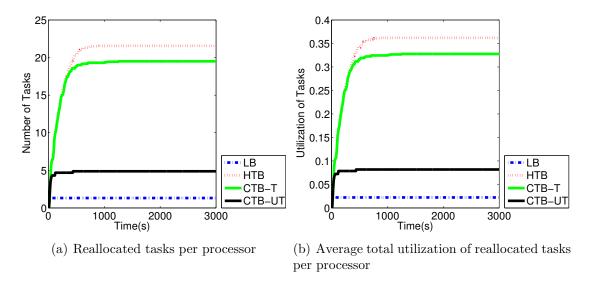

|   |     | 4.4.4 Comparison of Thermal Balancing Algorithms                                              |

|   |     | 4.4.5 Thermal Fault                                                                           |

|   |     | 4.4.6 Robustness against Different Ambient Temperatures                                       |

|   | 4.5 | Related Work                                                                                  |

|   | 4.6 | Summary                                                                                       |

| 5 | Cla | udDowerCon. Integrating Dower Pudget and Descripe Management                                  |

| J |     | udPowerCap: Integrating Power Budget and Resource Management oss a Virtualized Server Cluster |

|   | 5.1 | Introduction                                                                                  |

|   | 5.2 | Motivation                                                                                    |

|   | 0.2 | 5.2.1 Managing a Rack Power Budget                                                            |

|   |     | 5.2.2 Powercap Distribution Examples                                                          |

|   | 5.3 | CloudPowerCap Design                                                                          |

|   |     | 5.3.1 CloudPowerCap Power Model                                                               |

|   |     | 5.3.2 CloudPowerCap Design Priciples                                                          |

|   |     | 5.3.3 CloudPowerCap Overview                                                                  |

|   | 5.4 | CloudPowerCap Implementation                                                                  |

|   |     | 5.4.1 DRS Overview                                                                            |

|   |     | 5.4.2 Powercap Check                                                                          |

|   |     | 5.4.3 Powercap Allocation                                                                     |

|   |     | 5.4.4 Powercap Balancing                                                                      |

|   |     | 5.4.5 Powercap Redistribution                                                                 |

|   |     | 5.4.6 Implementation Details                                                                  |

|   | 5.5 | Evaluation                                                                                    |

|   |     | 5.5.1 DRS Simulator                                                                           |

|   |     | 5.5.2 Headroom Rebalancing                                                                    |

|   |     | 5.5.3 Standby Host Power Reallocation                                                         |

|   |     | 5.5.4 Flexible Resource Capacity                                                              |

|   | 5.6 | Related Work                                                                                  |

|                           | 5.7   | Summary    | • | • | • | • | <br>• | ٠ | ٠ | ٠ | • | • | • | • | • | <br>• | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |  | 117 |

|---------------------------|-------|------------|---|---|---|---|-------|---|---|---|---|---|---|---|---|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|-----|

| 6                         | Cor   | nclusion . |   | • |   | • |       |   |   |   |   |   |   |   |   | <br>  |   |   |   | • |   |   |   |   |   |   |   |   |   |   |   |   |  | 118 |

| $\mathbf{R}_{\mathbf{c}}$ | efere | nces       |   |   |   |   |       |   |   |   |   |   |   |   |   |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  | 119 |

# List of Figures

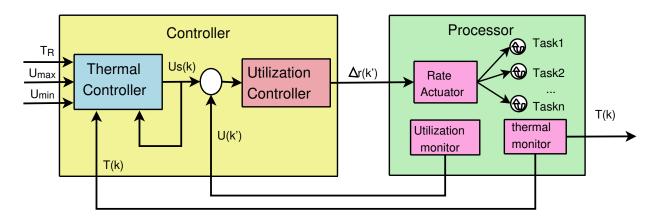

| 2.1  | TCUB structure                                                                  | 13 |

|------|---------------------------------------------------------------------------------|----|

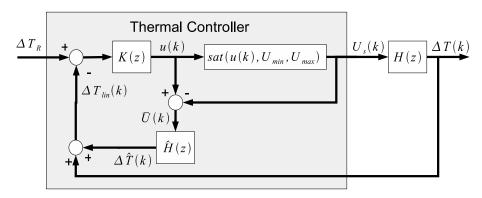

| 2.2  | Proposed thermal control structure                                              | 16 |

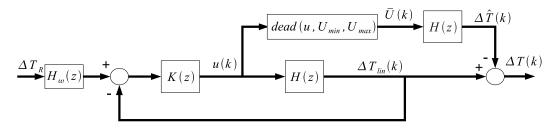

| 2.3  | Resulting feedback control structure when $H(z) = \hat{H}(z)$                   | 20 |

| 2.4  | Equivalent control structure given that $\hat{H}(z) = (1 + \Delta(z))H(z)$      | 21 |

| 2.5  | Closed-Loop structure when studying sensitivity                                 | 24 |

| 2.6  | Magnitude of sensitivity transfer function of the example system                | 25 |

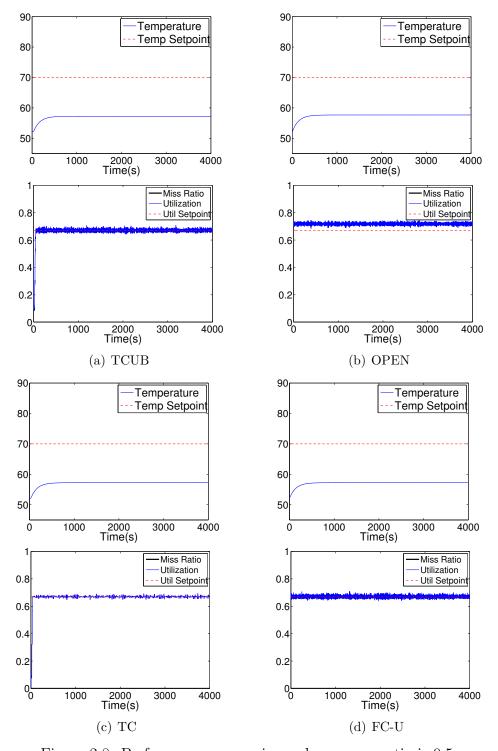

| 2.7  | Performance comparison when power ratio is 2                                    | 29 |

| 2.8  | Performance comparison when power ratio is 0.5                                  | 30 |

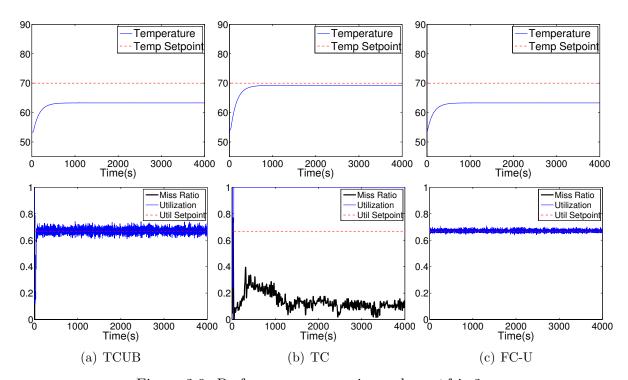

| 2.9  | Performance comparison when $etf$ is $2. \dots \dots \dots \dots \dots \dots$ . | 31 |

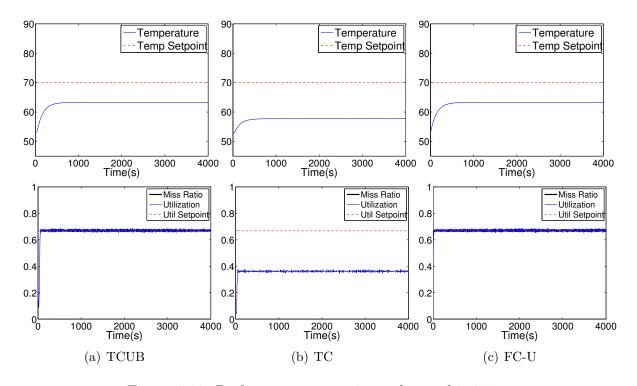

| 2.10 | Performance comparison when $etf$ is 0.5                                        | 32 |

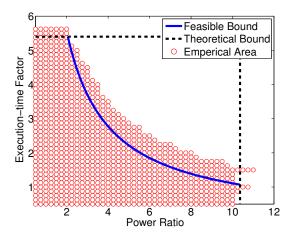

| 2.11 | TCUB performance with varying power ratio and etf                               | 33 |

| 2.12 | Performance comparison with thermal fault                                       | 34 |

| 2.13 | Performance comparison with different ambient temperature                       | 35 |

| 2.14 | TCUB performance with varied ambient temperature                                | 36 |

| 3.1  | Feedback control loop of RT-MTC                                                 | 40 |

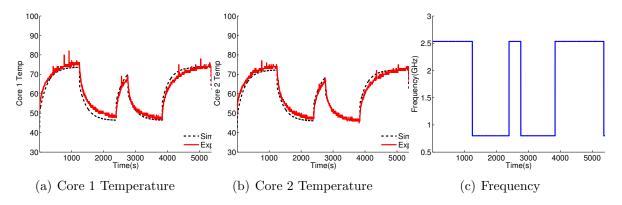

| 3.2  | Model identification data (mixed workload)                                      | 51 |

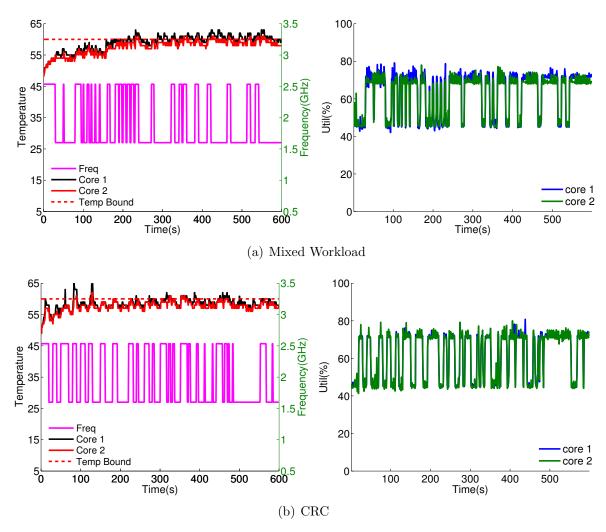

| 3.3  | Experimental results of RT-MTC                                                  | 52 |

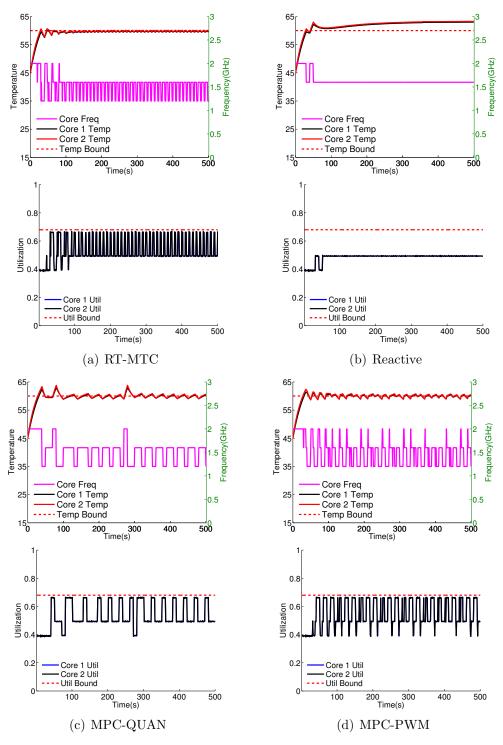

| 3.4  | Constant power variation when power ratio is 4                                  | 57 |

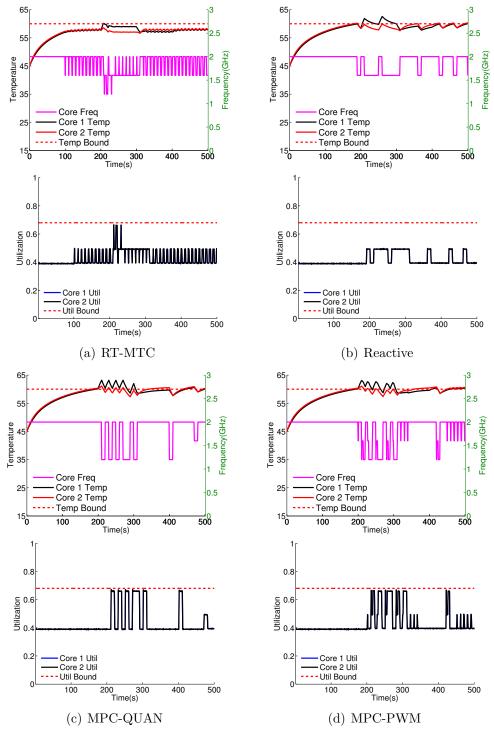

| 3.5  | Dynamic power variation                                                         | 60 |

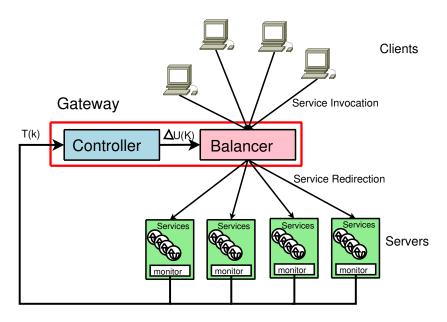

| 4.1  | The feedback control loop of CTB-T                                              | 70 |

| 4.2  | Analytical Power Gain Stable Region of CTB-T and CTB-UT                         | 74 |

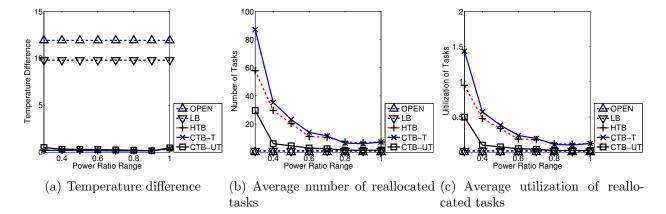

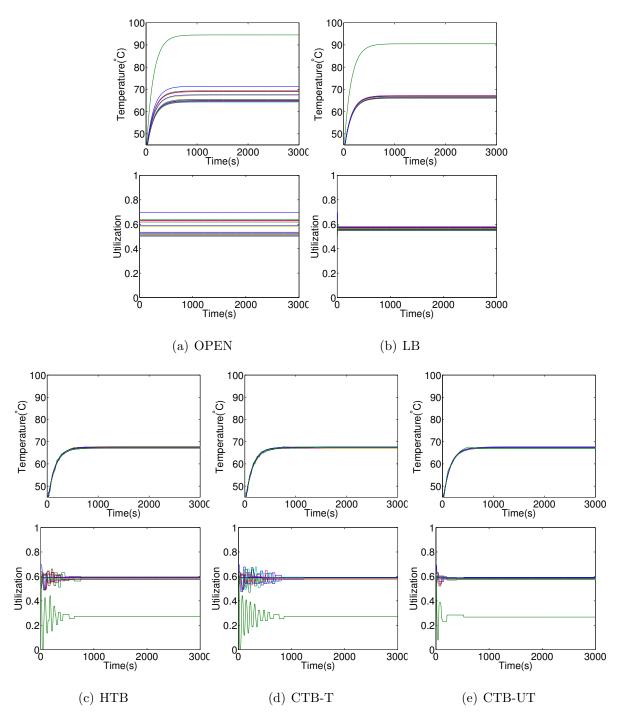

| 4.3  | Temperatures and CPU utilization of all processors under CTB and baseline       |    |

|      | algorithms                                                                      | 77 |

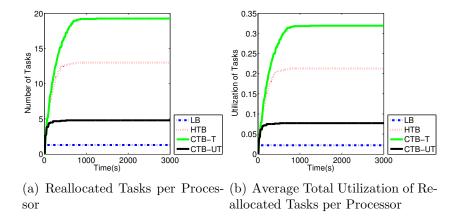

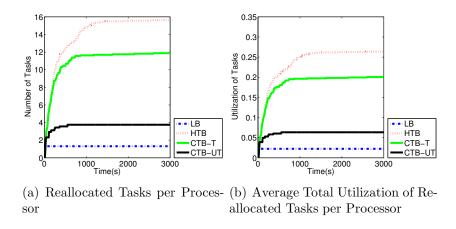

| 4.4  | Comparison of overhead due to tasks reallocation                                | 79 |

| 4.5  | Comparison of algorithms with different range of power ratio. The x axis represents the lower bound of the power ratio. For each data point shown in |     |  |  |  |  |  |  |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|--|

|      | this figure, the power ratio of tasks are randomly chosen in the range $[x, 1]$ .                                                                    | 80  |  |  |  |  |  |  |  |  |

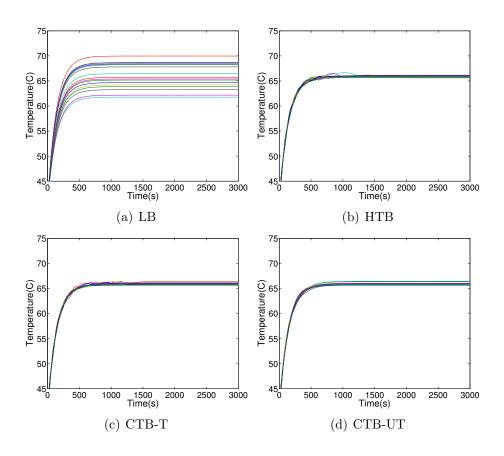

| 4.6  | Temperatures and CPU utilization of all processors under CTB and baseline                                                                            |     |  |  |  |  |  |  |  |  |

|      | algorithms                                                                                                                                           | 81  |  |  |  |  |  |  |  |  |

| 4.7  | Comparison of overhead due to tasks reallocation                                                                                                     | 82  |  |  |  |  |  |  |  |  |

| 4.8  | Temperatures and CPU utilization of all processors under CTB and baseline                                                                            |     |  |  |  |  |  |  |  |  |

|      | algorithms                                                                                                                                           | 83  |  |  |  |  |  |  |  |  |

| 4.9  | Comparison of Overhead due to Tasks Reallocation                                                                                                     | 83  |  |  |  |  |  |  |  |  |

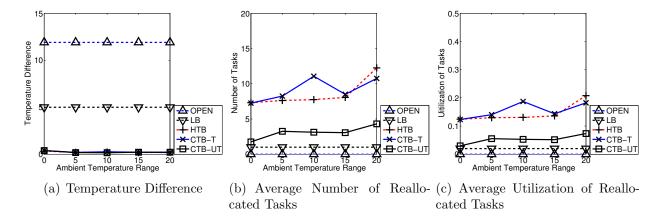

| 4.10 | Comparison of Algorithms with Different Ambient Temperature. The x axis                                                                              |     |  |  |  |  |  |  |  |  |

|      | represents the range of ambient temperatures of processors. For each data                                                                            |     |  |  |  |  |  |  |  |  |

|      | point shown in this figure, the ambient temperatures of processors are in the                                                                        |     |  |  |  |  |  |  |  |  |

|      | range $[(45 - x/2)^{\circ}C, (45 + x/2)^{\circ}C]$                                                                                                   | 84  |  |  |  |  |  |  |  |  |

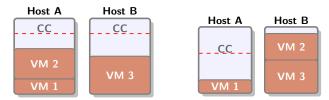

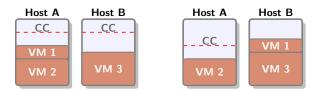

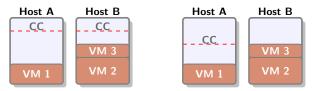

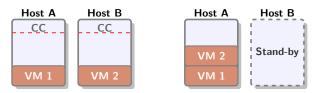

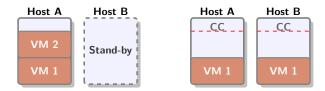

| 5.1  | Power cap distribution scenarios. Left-hand figures correspond to hosts status                                                                       |     |  |  |  |  |  |  |  |  |

|      | before distribution; right-hand figures show hosts status after. Power-capped                                                                        |     |  |  |  |  |  |  |  |  |

|      | capacity is not shown when the power cap of the host equals its peak power.                                                                          |     |  |  |  |  |  |  |  |  |

|      | (CC: Power-capped capacity)                                                                                                                          | 91  |  |  |  |  |  |  |  |  |

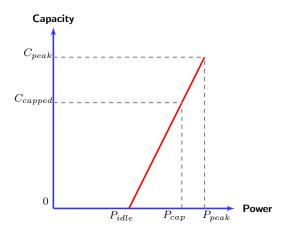

| 5.2  | Mapping a power cap $(P_{cap})$ to capped capacity $(C_{capped})$ . $P_{idle}$ and $P_{peak}$                                                        |     |  |  |  |  |  |  |  |  |

|      | are the idle and peak power of a host respectively. $C_{peak}$ and $C_{capped}$ are the                                                              |     |  |  |  |  |  |  |  |  |

|      | uncapped and capped raw capacity respectively                                                                                                        | 95  |  |  |  |  |  |  |  |  |

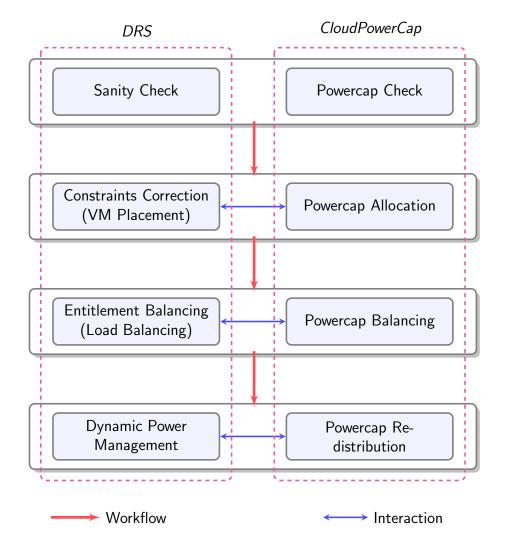

| 5.3  | Structure of CloudPowerCap working with DRS. <i>Italic</i> texts indicate corre-                                                                     |     |  |  |  |  |  |  |  |  |

|      | sponding components in general resource management systems                                                                                           | 100 |  |  |  |  |  |  |  |  |

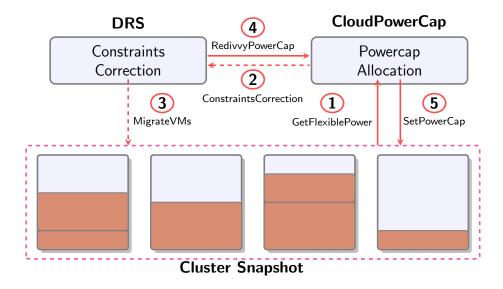

| 5.4  | Coordination between CloudPowerCap and DRS to correct constraints. Solid                                                                             |     |  |  |  |  |  |  |  |  |

|      | arrow indicates invocations of CloudPowerCap functions while dashed arrow                                                                            |     |  |  |  |  |  |  |  |  |

|      | indicates invocations of DRS functions                                                                                                               | 103 |  |  |  |  |  |  |  |  |

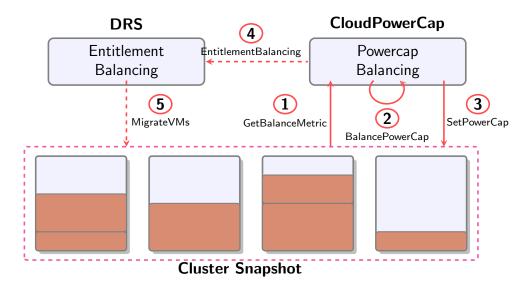

| 5.5  | Work flow of Powercap Balancing and its interaction with DRS load balancing.                                                                         |     |  |  |  |  |  |  |  |  |

|      | Solid arrow indicates to invocations of CloudPowerCap functions while dashed                                                                         |     |  |  |  |  |  |  |  |  |

|      | arrow indicates to invoke DRS functions                                                                                                              | 105 |  |  |  |  |  |  |  |  |

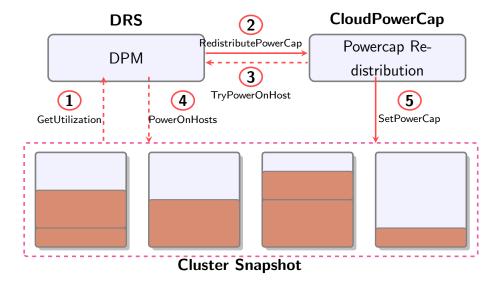

| 5.6  | Coordination between CloudPowerCap and DRS and DPM in response to                                                                                    |     |  |  |  |  |  |  |  |  |

|      | power on/off hosts. Solid arrow indicates to invoke CloudPowerCap functions                                                                          |     |  |  |  |  |  |  |  |  |

|      | while dashed arrow indicates to invoke DRS functions                                                                                                 | 108 |  |  |  |  |  |  |  |  |

| 5.7  | Headroom balancing on a group of 3 hosts. Hosts are gouped at each event                                                                             |     |  |  |  |  |  |  |  |  |

|      | time                                                                                                                                                 | 113 |  |  |  |  |  |  |  |  |

|      |                                                                                                                                                      |     |  |  |  |  |  |  |  |  |

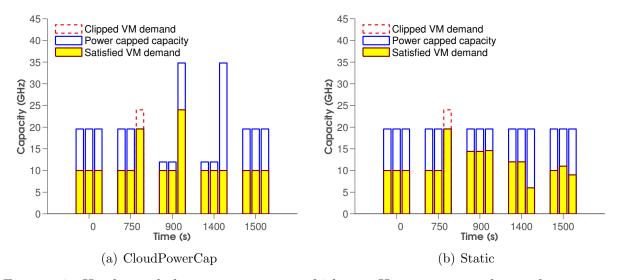

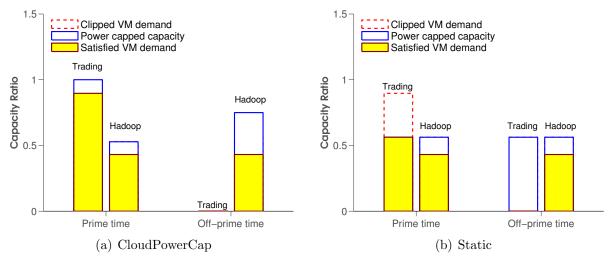

| 5.8 | Trade-offs between dynamical resource capacities. <i>Trading</i> indicates a group |     |

|-----|------------------------------------------------------------------------------------|-----|

|     | of servers running production trading while $Hadoop$ represents servers run        |     |

|     | production Hapdoop.                                                                | 115 |

## List of Tables

| 2.1 | Power and thermal parameters of simulated processor                         | 26  |

|-----|-----------------------------------------------------------------------------|-----|

| 2.2 | TCUB controller parameters                                                  | 27  |

| 3.1 | Symbols in thermal dynamic model                                            | 44  |

| 3.2 | Frequencies and thermal properties of the T9400 processor                   | 50  |

| 3.3 | Workload tasks period and execution time when frequency is 2.53GHz (ms).    | 50  |

| 3.4 | Results of model identification                                             | 50  |

| 3.5 | Simulation parameters                                                       | 54  |

| 4.1 | Power and thermal parameters                                                | 75  |

| 4.2 | Comparison of different algorithms                                          | 78  |

| 5.1 | The configuration of the server in the rack                                 | 89  |

| 5.2 | Server deployments in a rack with 8 KWatt power budget with different power |     |

|     | caps                                                                        | 90  |

| 5.3 | CloudPowerCap (CPC) rebalancing without migration overhead                  | 113 |

| 5.4 | CloudPowerCap (CPC) reallocating standby host power                         | 114 |

| 5.5 | CloudPowerCap (CPC) enabling flexible resource capacity                     | 116 |

### Acknowledgments

I would like to sincerely thank my advisers, Professor Chenyang Lu, whose guidance helped me through my Ph.D career. Chenyang has always been a source of not only inspiration but also support. The ideas presented in this paper, totally or partially, arise from discussions with Chenyang.

I would also want to thank Professor Xenofon D. Koutsoukos and Dr. Nicholas Kottenstette, who not only provided valuable knowledge of control theory but also partially shaped my research.

My internship at VMware offered me a wonderful opportunity to experience work and research under industry environment. I greatly thank my mentor, Dr. Anne Holler for making my internship a very enjoyable and rewarding experience.

Finally, I am grateful to have opportunity to collaborate with many colleagues who support my research: Mo Sha, Chengjie Wu, Abu Sayeed Saifullah, Sisu Xi, Dr. Yixin Chen, Dr. Humberto Gonzalez, Dr. Anna Leavey, Dr. Weining Wang, Bill Drake, Andrew Kutta, Dr. Pratim Biswas and Craig England.

Yong Fu

Washington University in St. Louis December 2013 To Yan and Claire

#### ABSTRACT OF THE DISSERTATION

Dynamic Thermal and Power Control for Computing Systems

by

Yong Fu

Doctor of Philosophy in Computer Science Washington University in St. Louis, 2013 Professor Chenyang Lu, Chair

Thermal and power management have become increasingly important for computers. Computing systems from real-time embedded systems to data centers require effective thermal and power management to prevent overheating and save energy. In this dissertation we investigate dynamic thermal and power management for computer systems and buildings. (1) We present thermal control under utilization bound (TCUB), a novel control-theoretic thermal management algorithm designed for single core real-time embedded systems. A salient feature of TCUB is to maintain both desired processor temperature and real-time performance. (2) To address unique challenges posed by multicore processors, we develop the real-time multicore thermal control (RT-MTC) algorithm. RT-MTC employs a feedback control loop to enforce the desired temperature and CPU utilization of the multicore platform via dynamic frequency and voltage scaling. (3) We research dynamic thermal management for real-time services running on server clusters. We develop the control-theoretic thermal balancing (CTB) to dynamically balance temperature of servers via distributing clients' service requests to servers. (4) We propose CloudPowerCap, a power cap management system

for virtualized cloud computing infrastructure. The novelty of CloudPowerCap lies in an integrated approach to coordinate power budget management and resource management in a cloud computing environment.

### Chapter 1

### Introduction

Thermal and power management have become increasingly important for both computing and physical systems. Fast growing power density and on-chip temperature are key challenges in computer system design. Increased temperatures reduces life span of processors, degrades performance, adversely affects reliability and increases cooling cost and energy. Hence there is widespread interest in thermal management at different levels of computing systems from real-time embedded systems to data centers.

Power management is another critical concern of modern computing systems since it directly affects both operational and deployment cost. For example, a datacenter of 30,000 square feet, which host tens of thousands of servers, consumes 10MW of electricity and requires an accompanying cooling system that costs from 2 to 5 million dollars. Overall, data centers in US consume 100 billion kWh in 2011 according to estimate by the Environmental Protection Agency (EPA) [21]. Moreover, power delivery and cooling limitations in datacenters are bottlenecks of high density configurations to meet the ever increasing performance and scalability demand.

This dissertation focus on studying of thermal and power management of computer systems. The research can be divided into two parts. The first part, from Chapter 2 to Chapter 4, focuses on thermal and power management of real-time systems on different types of computing platforms. Chapter 2 and Chapter 3 investigates thermal management for real-time systems working on single core and multicore processors, respectively. Due to uncertainties in power consumption and workload, we proposed a suite of control-theoretic thermal management approaches to meet both the temperature and real-time performance requirements. Chapter 4 studies thermal management of real-time clusters. In contrast to existing

approach, the proposed approach reduces *hot spots* in the cluster by balancing thermal workload rather than regulating individual servers, improving system throughput without compromising thermal performance.

In the second part, Chapter 5, we focus on power management of distributed systems, specifically, power cap management for cloud computing infrastructure. Our dynamic power cap management, CloudPowerCap, coordinates with existing resource management framework to provide integrated power budget and resource management for virtualized server clusters.

# 1.1 Feedback Thermal Management for Real-time systems

Real-time embedded systems face significant challenges in thermal management as they adopt modern processors with increasing power density and compact architecture. Such systems must avoid processor overheating while still maintaining desired real-time performance. While modern processors usually rely on hardware throttling mechanisms to prevent overheating, such mechanisms cause performance degradation which is unacceptable for real-time applications. Moreover, real-time systems must deal with a broad range of uncertainties in system characteristics and environmental conditions, such as power consumption variation, ambient temperature fluctuation and thermal fault. Finally, multicore processors induce unique challenges on thermal management due to inter-core thermal coupling and practical constraints of power management mechanism such as Dynamic Voltage and Frequency Scaling (DVFS).

In recent years, control-theoretic thermal management approaches have shown promise in [20, 27, 54, 99, 105, 106] handling uncertainties in thermal characteristics. In contrast to heuristic-based design relying on trial-and-error, control-theoretic approaches provide a scientific framework for systematic design and analysis of thermal control algorithms. The major advantage of adopting feedback control theory in thermal management is to systematically handle uncertainties of thermal dynamics of computing systems.

In this dissertation, we first present *Thermal Control under Utilization Bound (TCUB)*, a novel dynamic thermal management algorithm specifically designed for real-time systems running on single-core processors. TCUB employs feedback control loops to control *both* the processor temperature and CPU utilization by adjusting task rates. In contrast to earlier research on feedback control real-time scheduling that ignores thermal issues [60], TCUB can maintain *both* desired processor temperature and CPU utilization bound, thereby avoiding processor overheating and maintaining desired real-time performance.

Secondly, to address the unique challenges posed by mulitcore processors, we present *Real-Time Multicore Thermal Control (RT-MTC)*, a feedback thermal control algorithm for real-time systems running on multicore processors. RT-MTC employs a feedback control loop that enforces the desired temperature and CPU utilization bounds of embedded real-time systems through DVFS. RT-MTC combines a control-theoretic approach and a practical design to provide a simple, efficient and easily implemented solution to handle challenges and requirements unique to multicore processors.

Finally, we designed Control-theoretic Thermal Balancing (CTB), an feedback thermal management approach for server clusters running real-time services. CTB performs dynamic thermal balancing to reduce the differences among the temperatures of different processors through workload distribution. Thermal balancing is an attractive approach for thermal management on distributed systems since it can mitigate hot spots without significantly compromising system performance. CTB employs a feedback control loop that periodically monitors the temperature and CPU utilization of different servers in a cluster, and redistributes clients' service requests among different processors to dynamically balance their temperature.

### 1.2 CloudPowerCap

In many datacenters, server racks are as much as 40 percent underutilized [30]. Rack slots are intentionally left empty to keep the sum of the servers' nameplate power below the power provisioned to the rack. To address rack underutilization, server vendors have introduced support for per-host power caps, which provide a hardware or firmware-enforced limit on the amount of power that the server can draw [19, 39, 43]. However while this approach

improves rack utilization, it burdens the operator with managing the rack power budget across the hosts and, even worse, lacks flexibility to handle workload spikes or to respond to the addition or removal of a rack's powered-on server capacity.

In this dissertation we developed CloudPowerCap, a holistic and adaptive solution for power budget management in a virtualized environment. CloudPowerCap manages the power budget for a cluster of virtualized servers, dynamically resetting the per-host power caps for hosts in the cluster. The key of CloudPowerCap is to treat and manage the power cap in close coordination with resource management system. CloudPowerCap maps each host's power cap into resources capacity, by which CloudPowerCap can interoperate with a sophisticated resource management system of cloud datacenters, allowing it to manage power caps through the VM resource controls supported by resource management systems. CloudPowerCap provides global fairness on dynamical power caps distribution with robustness for unpredictable workload variation, preventing hosts from gaining unfair entitlement of power caps and enhancing the system's capability to enforce VM placement constraints. To the best of our knowledge, CloudPowerCap is the first holistic framework to provide dynamic power budget management in coordination with a cloud resource management system.

### 1.3 Contributions

Specifically, this dissertation made the following contributions:

Feedback thermal management for real-time systems on single core processor: We designed TCUB, a novel dynamic thermal management algorithm specifically for real-time embedded systems on single processors. TCUB employs feedback control loops to enforce *both* desired processor temperature and CPU utilization by adjusting task rates, thereby avoiding processor overheating and maintaining desired real-time performance.

Feedback thermal management for real-time systems on mulit-core processor: We designed *RT-MTC*, a feedback thermal control algorithm to tackle the challenges posed by multicore processors, which enforces the desired temperature and CPU utilization bounds of real-time embedded systems through realistic DVFS mechanisms.

Feedback thermal balancing for real-time clusters: We designed *CTB*, a control-theoretic thermal balancing approach employing feedback control loop that redistributes clients' service requests among different servers to dynamically balance their temperature.

Dynamic power cap management for cloud computing infrastructure: We designed CloudPowerCap, a holistic and adaptive solution for power budget management in a virtualized environment. CloudPowerCap manages the power budget for a cluster of virtualized servers, dynamically resetting the per-host power caps for hosts in the cluster to respect the power budget of the cluster. The key of CloudPowerCap is to treat and manage the power cap in close coordination with resource management system.

### Chapter 2

# Feedback Thermal Management for Real-time Systems on Single Core Processors

### 2.1 Introduction

Real-time embedded systems face significant challenges in thermal management as they adopt modern processors with increasing power density and compact architecture. Such systems must avoid processor overheating while still maintaining desired real-time performance. While modern processors usually rely on hardware throttling mechanisms to prevent overheating, such mechanisms cause performance degradation unacceptable for real-time applications.

Moreover, real-time embedded systems must deal with a broad range of uncertainties in system characteristics and environmental conditions:

- Power consumption: The power consumption of a processor may vary significantly when running different tasks with different instructions [46].

- Ambient temperature: In contrast to servers operating in air-conditioned environments, real-time embedded systems may operate in diverse environments under a wide range of ambient temperature.

- Thermal faults: Due to their harsh operating conditions embedded systems can be particularly susceptible to failures of cooling subsystems [23].

- Tasks execution times: The execution times of many real-time tasks may vary significantly because their executions are strongly influenced by the operating environment and sensor inputs.

To meet these challenges, we present *Thermal Control under Utilization Bound (TCUB)*, a novel dynamic thermal management algorithm specifically designed for real-time embedded systems. TCUB employs feedback control loops to control *both* the processor temperature and CPU utilization by adjusting task rates. In contrast to earlier research on feedback control real-time scheduling that ignores thermal issues [60], TCUB can maintain *both* desired processor temperature and CPU utilization bound, thereby avoiding processor overheating and maintaining desired real-time performance. TCUB has the following salient features.

- TCUB features a nested feedback control structure consisting of (1) a low-rate thermal controller dealing with the slower thermal dynamics, and (2) a high-rate utilization controller handling the faster CPU utilization dynamics caused by uncertainties in task execution times. The thermal controller outputs a set point for the CPU utilization below the schedulable utilization bound of the real-time system. This set point is, in turn, used by the utilization controller to adjust the task rates. The modular control structure allows separate control designs optimized for thermal-protection and utilization-regulation.

- In contrast to earlier research on thermal-ware real-time scheduling that relies in accurate system and task models [14, 42, 92, 93, 102], TCUB is a highly robust algorithm that can handle a broad range of uncertainties in terms of processor power consumption, task execution times, thermal faults, and ambient temperature. The robustness of TCUB makes it particularly suitable for real-time embedded systems that operate in highly unpredictable environments.

- TCUB features a simple and efficient thermal controller that integrates a discretetime-proportional-integral-controller and a traditional anti-windup controller designed to enforce the schedulable utilization bound. The anti-windup controller is necessary

to enforce the schedulable utilization bound that impose hard saturation constraints on the output of the thermal controller (utilization set point). Moreover, the control approach allows rigorous analysis of stability and robustness under uncertainties.

• Extensive simulation results demonstrate the stability and robustness of TCUB under a wide range of uncertainties and operating conditions including varying tasks execution times, power consumption and ambient temperature, as well as thermal faults.

The rest of the chapter is organized as follows. Section 2.3 presents a difference equation model that characterizes the thermal dynamics of real-time systems and the goal of thermal control for real-time systems. Section 2.5 details the design and stability analysis of TCUB. Section 2.6 provides simulation results. Section 2.2 introduces related work. Section 2.7 summarizes this chapter.

### 2.2 Related Work

Thermal management of real-time systems received significant attention recently. Some researchers explore thermal-aware real-time scheduling [14, 42, 92, 93, 102] to enforce temperature bounds while meeting real-time performance constraints. Existing thermal-aware real-time scheduling algorithms rely on accurate knowledge of the system characteristics such as task execution times and power consumption, which may vary dynamically at run time for real-time systems. In contrast, thanks to its robust feedback control approach, TCUB is especially designed to handle a broad range of uncertainties.

A multitude of feedback real-time scheduling and utilization control algorithms have been proposed in recent years, [4,9,47,80,83,94,108], but they are not cognizant of processor temperature. In contrast, TCUB is designed to control both the real-time performance and the processor temperature. While TCUB incorporates a utilization controller, the key contribution of this work is the nested control architecture and the novel thermal controller that can handle the utilization bound constraint needed to enforce desired soft real-time performance.

Several papers [17,69–71,99,104–106] have adopted model predictive control or online convex optimization for dynamic thermal management. None of these works are concerned with maintaining real-time performance or enforce CPU utilization bound. In addition, control approaches based on model predictive control and convex optimization has higher computation complexity than our efficient proportional control approach.

Fu. et al. [27] proposed a model predictive control approach for thermal and utilization control in distributed real-time systems. While it shares similar goals as TCUB, there are several differences between them. First, the algorithm proposed in [27] uses different actuators to control temperature (DVFS) and utilization (task rate adaptation). Instead, TCUB uses a single actuator (task rate adaptation) to control both temperature and utilization. This makes TCUB a more general solution applicable to a broader range of real-time systems including those running on embedded hardware that does not support DVFS. At the same time, relying on a single actuator also poses unique challenges since temperature and utilization control are closely coupled due to the shared actuator. Second, our control design is fundamentally different from the model predictive control approach adopted in [27]. Our novel control design result in a simple and efficient nested control algorithm with  $\mathcal{O}(1)$ run-time overhead. In contrast, the model predictive controller [27] relies on a least-square estimator with polynomial complexity to solve the control output over the control and prediction horizon. The simplicity and efficiency of TCUB make it a practical solution even for resource-limited embedded processors. Finally, our control approach allows rigorous robustness analysis. Since our robustness analysis is based on the necessary and sufficient conditions required of the Nyquist stability criteria, we prove and demonstrate how our controller can respond quickly while operating under system uncertainties. In contrast, the small-gain conditions [103] required to satisfy robustness criteria of the proposed model predictive controller presented in [27] tend to be conservative and computationally intensive to verify [107]. Loosening these model uncertainty constraints for model-predictive controllers is a daunting task as noted in [63] and currently being addressed in [32, 50, 59].

### 2.3 Problem Formulation

In this section we first present the system model adopted in this work, and then discuss the goals of thermal control for real-time systems.

### 2.3.1 System Models

A key feature of our system model is that it characterizes the *uncertainties* in real-time systems in terms of tasks execution times, power consumption, ambient temperature, and thermal faults. We assume a single CPU real-time system running n independent, periodic real-time tasks,  $\{T_i|1 \leq i \leq n\}$ . Each task  $T_i$  has a period  $p_i$ . The rate  $r_i$  of the task  $T_i$  is defined as  $r_i = \frac{1}{p_i}$ . Each task has a soft deadline related to its period and an estimated execution time  $c_i$  known at design time. However, the actual execution time  $a_i$  at run time is unknown and may deviate from  $c_i$ .

The rate  $r_i$  of the task  $T_i$  can be dynamically adjusted within a range  $[R_{\min,i}, R_{\max,i}]$ . Earlier works have shown that task rates in many real-time applications (e.g., digital feedback control [12] and multimedia [10]) can be adjusted in certain ranges without causing system failure. A task running at a higher rate contributes a higher value to the application at the cost of higher CPU utilization.

When tasks are running on the processor, the active power consumed by the processor fluctuates significantly. Earlier work refers to such significant power variation during run time as power phase behavior [46]. At the instruction level, different instruction types, inter-instruction overhead, memory system states and pipeline related effects cause power fluctuation [85]. Consequently, while the processor's *estimated* active power,  $P_a$ , is known, the actual active power of the processor may deviate from the estimate at run time. When the processor is idle, the processor consumes idle power  $P_{\text{idle}}$ .

We adopt the well known thermal RC model to characterize the thermal dynamics of the processor [5,23]:

$$\frac{dT(t)}{dt} = -b_2(T(t) - T_o) + b_1 P(t) \tag{2.1}$$

where T(t) is the temperature of the processor,  $T_o$  is ambient temperature, P(t) is the actual power consumed by the processor,  $b_1 = \frac{1}{C_{th}}$  and  $b_2 = \frac{1}{R_{th}C_{th}}$ , where  $C_{th}$  is heat capacity and  $R_{th}$  is heat resistance. As a high level model thermal RC model is efficient for thermal control design and computation comparing to the architecture level thermal model like Hotspot [41] because of its simple structure. However thermal RC model may introduce model error As embedded systems may operate in diverse environments, the ambient temperature  $T_0$  may change. Moreover, thermal faults (e.g., fan failure) may cause significant change to the thermal resistance [23]. A thermal control algorithm designed for real-time systems must handle these uncertainties at run time.

### 2.3.2 Design Goals

Our thermal control algorithm is designed to meet two primary requirements: (1) to prevent processor overheating, and (2) to maintain desired soft real-time performance. Due to the uncertainties faced by real-time systems, TCUB adopts a feedback control approach that dynamically controls the processor temperature and real-time performance. It allows users to specify a temperature set point  $T_R$ , maximum and minimum CPU utilization bound  $U_{\text{max}}$ ,  $U_{\text{min}}$ . For processors support hardware throttling, the temperature set point is below the temperature threshold for hardware throttling so as to avoid unpredictable performance degradation caused by throttling. For processors that do not support throttling, the temperature set point should be below the maximum temperature tolerable to the processor. The maximum CPU utilization bound  $U_{\text{max}}$  should be below the schedulable CPU utilization bound of the real-time scheduling policy. For example, the schedulable CPU utilization bound of Rate Monotonic Scheduling (RMS) is  $U_{\text{max}} = n(2^{\frac{1}{n}} - 1)$ , where n is the number of the periodic real-time tasks [56]. The minimum CPU utilization bound  $U_{\text{min}}$  can be determined by minimum allowable tasks rate  $R_{\text{min},i}$  for a given system.

TCUB is designed to prevent processor overheating by keeping the temperature close to the temperature set point  $T_R$  and to maintain desired software real-time performance by enforcing the CPU utilization bound  $U_{\text{max}}$ . Moreover, TCUB must handle uncertainties in terms of power consumption, task execution times, ambient temperature, and thermal faults.

<sup>&</sup>lt;sup>1</sup>As TCUB only controls the average CPU utilization dynamically, it is not suitable for hard real-time systems.

Finally, the control algorithm should be simple and efficient to provide a practical solution for resource-limited embedded systems.

### 2.4 Overview of TCUB

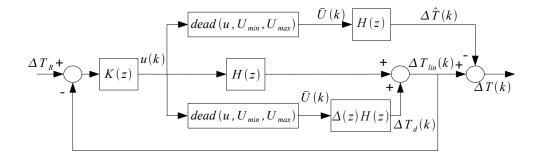

We propose a nested feedback control approach to manage both temperature and CPU utilization. As shown in Fig. 2.1, there are two control loops in TCUB that operate at different time scales. The outer loop is responsible for thermal control and runs at a lower rate than the inner loop responsible for utilization control. In the outer loop, the thermal controller aims to enforce the specified temperature set point  $T_R$ . At the end of the  $k^{th}$  sampling period of the outer loop, the thermal controller computes the utilization set point  $U_s(k)$  for the utilization controller of the inner loop based on the measured temperature T(k) provided by the thermal monitor. The inner-loop utilization controller ensures that the utilization converges to the set point  $U_s(k)$  computed by the thermal controller by adjusting the task rates. At the  $k'^{th}$  sampling period of the inner loop, the utilization controller outputs the task rate change  $\Delta r(k')$  based on the measured utilization U(k'). The rate actuator adjusts tasks rate based on the output of the utilization controller. Our multi-rate nested control approach has several important advantages.

- 1. The thermal dynamics are typically significantly slower than the utilization dynamics, which motivates a multi-rate control approach. The processor thermal-control problem usually involves a *large* thermal time-constant whereas existing utilization controllers (which we incorporate into our design) typically have dynamic responses within a few seconds [60].

- 2. Unlike the computationally intensive model predictive control adopted by earlier work on thermal control [27], our proposed nested control architecture greatly simplifies the control algorithms. It requires neither complicated gain-scheduling tables nor complicated on-line optimization algorithms. The lower rate of the thermal-control loop further reduces computational overhead.

3. We provide a stability and robustness analysis for the thermal-controller, based on the necessary and sufficient Nyquist Stability criterion which allows us to *directly* relate uncertain physical properties of our thermal-dynamic control problem, whereas the model predictive control approach [27] has to rely on a *conservative* small gain assumption and offers little insight into the physical parameter uncertainties which directly affect stability and performance.

Figure 2.1: TCUB structure

Specifically, the nested control loops work as follows. The thermal and utilization controller employ two sampling periods:  $T_s$ , which denotes the sampling period of the processor's temperature; and  $T_u$ , which is the sampling period of the utilization ( $T_u < T_s$ ). At the end of the  $k^{\text{th}}$  temperature sampling period, the feedback loop is invoked and executes the following steps:

- 1. The temperature monitor sends the processor's temperature T(k) to the thermal controller over the last sampling period.

- 2. The thermal controller calculates the utilization set point of the processor,  $U_s(k)$ , based on T(k) and temperature reference. It then sends  $U_s(k)$  to the utilization controller. Note  $U_s(k)$  is effectively held for m samples in which m is a positive integer which relates the outer-loop sample time  $T_s$  to the inner-loop sample time  $T_u$  such that  $T_s = mT_u$ .

3. The utilization controller adjusts the task rates through a rate actuator in each  $T_u$  sampling period so as to track the utilization set point  $U_s(k)$ . TCUB employs FC-U [60] as the utilization controller, which uses a Proportional controller to track the utilization set point.

A benefit of our nested control structure is modular design, that is, we can design the two control loops separately. For utilization control loop we reuse the well studied feedback control utilization controller FC-U [60]. FC-U periodically monitors the utilization of the CPU, computes the control output based on difference between current utilization and the utilization setpoint and then calls rate adaptor to change utilization according to control output. FC-U is implemented in FCS/nORB, a real-time middleware on a Linux platform [97]. Since the effectiveness of FC-U is justified by experiments and implementation, in the following sections, we focus on the thermal controller design and stability analysis.

### 2.5 Thermal Control Design and Analysis

In this section we describe the control design and analysis of TCUB. In the following sections we present the design of thermal controller and the stability analysis.

### 2.5.1 Dynamic Model for Thermal Control

As a foundation for the design of the thermal controller, we derive a discrete-time, difference equation model that characterizes the dynamic relationship between the CPU utilization U(k) (the control input) and the processor temperature T(k) (the controlled variable). We first characterize the relationship between the power consumption and the CPU utilization and then derive a discrete-time model based on the thermal RC model.

First, we characterize the relationship between the power consumption of the processor and its CPU utilization. Let U(k) denote the CPU utilization in the  $k^{th}$  sampling period. The average power of the processor in  $k^{th}$  sampling period,  $\bar{P}(k)$ , has the following relationship

with U(k):

$$\bar{P}(k) = G_p P_a U(k) + P_{\text{idle}}(1 - U(k)) = (G_p P_a - P_{\text{idle}}) U(k) + P_{\text{idle}}$$

(2.2)

where  $G_p$  represents the ratio between the actual active power at run time and the estimated active power  $P_a$ . In (2.2),  $G_pP_a$  is the actual active power, and U(k) is the fraction of time when the CPU is active.  $P_{\text{idle}}$  is the power when the CPU is idle, and 1-U(k) is the fraction time when the CPU is idle. The same power model is also used in temperature simulation of server systems [37].

Next, we transform the thermal RC model (2.1) to a discrete-time model. Denote the Laplace transform of the difference between processor's temperature and ambient temperature, T(t) –  $T_o$ , as T(s) as well as P(t) as P(s) from (2.1), we have the following model

$$T(s) = \frac{R_{\text{th}}}{R_{\text{th}}C_{\text{th}}s + 1}P(s) + \frac{1}{R_{\text{th}}C_{\text{th}}s + 1}T_{o}.$$

(2.3)

For control analysis we need to derive a discrete-time model to approximate this system. The thermal controller issues a fixed-periodic utilization set point which the inner-loop utilization controller closely and quickly regulates to. This utilization set point is proportional to the average power consumed by the processor. As previously mentioned, the thermal-time constant is large, therefore the effects of transients are negligible. Thus a ZOH-equivalent model is appropriate to approximate a discrete-time model of the thermal dynamics of the system. It is straightforward to derive the linear ZOH-equivalent discrete time model from (2.3) as follows [25]:

$$T(k+1) = \Phi T(k) + (1-\Phi)T_o + R_{\mathsf{th}}(1-\Phi)P(k)$$

(2.4)

where k represents  $k^{th}$  sampling period,  $\Phi = \exp(-\frac{T_s}{R_{th}C_{th}})$  and  $T_s$  is the sampling period.

Then we combine the thermal RC model (2.4) and the relationship between power and utilization (2.2), specifically, by substituting P(k) for  $\bar{P}(k)$ , we could derive the model employed in thermal control:

$$T(k+1) = \Phi T(k) + R_{\mathsf{th}}(1-\Phi)(G_a P_a - P_{\mathsf{idle}})U(k) + R_{\mathsf{th}}(1-\Phi)P_{\mathsf{idle}} + (1-\Phi)T_o. \tag{2.5}$$

### 2.5.2 Thermal Controller Design

The principal challenge for the thermal controller design is to ensure that a maximum allowable temperature  $T_R$  is not exceeded while the thermal-control output  $U_s(k)$  is subject to actuator saturation which is governed by utilization bound  $U_{\text{max}}(0 \leq U_{\text{max}} \leq 1)$ . The thermal controller is required to regulate the temperature of the processor to subject to the utilization constraint given its output  $U_s(k)$ . A proportional-integrator (PI) controller with an integrator-anti-windup controller is proposed to determine  $U_s(k)$  while addressing actuator limitations in order to guarantee stability. This simple yet elegant outer-thermal control loop can be run at a significantly lower-rate without any noticeable performance loss due to the systems large thermal time constant.

The structure of thermal controller we proposed is illustrated in Fig. 2.2. It consists of a PI controller (denoted as K(z)), an anti-windup controller (denoted as  $\hat{H}(z)$ ) which is determined from a processor's thermal model  $\hat{H}(z)$  and a saturation block. The PI controller's output is limited by the saturated block and then the utilization set point output by the thermal controller cannot surpass the utilization bound assigned by the users. Essentially anti-windup controller transforms nonlinear behavior of the real-time systems induced by the utilization bounds to linear behavior so that normal linear control design could be exploited. The input of the PI controller is the error between the reference trajectory and linearized

Figure 2.2: Proposed thermal control structure.

temperature  $\Delta T_{\rm lin}(k)$ . The control output of the PI controller, u(k), is limited to enforce

utilization bounds by the saturated block,  $U_s(k) = \text{sat}(u(k), U_{\min}, U_{\max})$ , in which

$$sat(x, x_{\min}, x_{\max}) = \begin{cases} x_{\min}, & \text{if } x < x_{\min} \\ x_{\max}, & \text{if } x > x_{\max} \\ x, & \text{otherwise.} \end{cases}$$

The error between  $U_s(k)$  and u(k), denoted as  $\bar{U}(k)$ , is passed through a thermal model of the processor (denoted  $\hat{H}(z)$ ) which generates a compensation term  $\Delta \hat{T}(k)$ , when combined with the actual processor temperature difference  $\Delta T(k)$ , a linearized temperature difference  $(\Delta T_{\text{lin}}(k) = \Delta \hat{T}(k) + \Delta T(k))$  is fed-back to the controller K(z) in order to guarantee stability. This compensation is also known as anti-windup control. It is noted that the thermal model of the processor is used here without considering dynamic of the utilization controller. This is one of the benefits of nested control structure, that is, we can design the thermal and utilization controller separately. In order to describe our implementation of the thermal controller, as presented in Algorithm 1, we denote  $\hat{T}_{idle}$  as an estimate of the idle temperature  $T_{idle}(t)$  and  $\hat{T}_o$  as either an estimate or measurement of ambient temperature  $T_o$ .

For thermal controller design, we rewrite the model (2.5) in a more compact form. Note that the temperature T(k) depends ultimately on the ambient temperature  $T_o$ , the idle temperature component  $T_{\text{idle}}$  which depends on the idle power component  $P_{\text{idle}}$  such that  $T_{\text{idle}} = R_{\text{th}}P_{\text{idle}}$ , and the active power component  $\Delta T(k)$ , that is,  $T(t) = \Delta T(t) + T_o + T_{\text{idle}}$ . Then the model (2.5) could be rewritten as

$$\Delta T(k+1) = \Phi \Delta T(k) + \Gamma U(k) \tag{2.6}$$

where  $\Gamma = k_p R_{\mathsf{th}} (1 - \Phi)$  and  $k_p = (G_a P_a - P_{\mathsf{idle}})$ . In model (2.6) uncertainty in  $G_p$  can be expressed in terms of the following bounds on the *actual power gain*  $k_p$  such that  $k_{p \min} \leq k_p \leq k_{p \max}$ .

In z-domain the model (2.6) can be written as follows

$$H(z) = \frac{\Delta T(z)}{U(z)} = \frac{\Gamma}{z - \Phi}.$$

(2.7)

To design the thermal controller with the proposed structure we follow two steps. First a nominal linear controller K(z) ignoring the saturating limit is designed. In this work the nominal linear controller is a PI-controller,  $K(s) = K_{\rm P} + K_{\rm I} \frac{s+\omega_{\rm I}}{s}$ . The discrete time controller K(z) is synthesized using the IPESH-transform from the continuous time controller model K(s). The IPESH-transform, like the bilinear-transform, is both a passivity and stability preserving transform which can be applied to any linear-time invariant model K(s) except that it will not suffer from warping effects and therefore closely matches the magnitude response up to the Nyquist frequency  $\frac{\pi}{T_s}$  [48,49]. The result discrete time controller is:

$$K(z) = K_{\rm P} + K_{\rm I} \left( 1 + \frac{\omega_{\rm I} T_s}{2} \right) \frac{z - \frac{2 - \omega_{\rm I} T_s}{2 + \omega_{\rm I} T_s}}{z - 1}.$$

Secondly, an anti-windup controller  $\hat{H}(z)$  is designed to limit performance deterioration in the event of a control constraints being encountered. The details of anti-windup controller are presented in Section 2.5.3.

Algorithm 1 describes workflow of the thermal controller and the derivation of thermal controller related parameters used in the algorithm are explained in Section 2.5.3.

### 2.5.3 Stability Analysis

The section analyzes the stability of the proposed control framework. For a real-time system under thermal control, stability ensures that the processor temperature converges to the temperature set-point. In order to discuss stability, we recall the following definition and the Nyquist stability theorem.

**Definition 1.** A stable discrete-time linear time invariant (LTI) system is one in which all poles are inside the unit circle.

For our control structure, it should be intuitive from viewing Fig. 2.2 that there are only two cases to maintain stability. The first case, when the control input  $U_{\min} \leq u(k) \leq U_{\max}$  (which implies that  $\bar{U}(k) = 0$ ) we want to enforce stability of the *active* closed-loop system consisting of K(z) and H(z), and stability of  $\hat{H}(z)$ . For the second case, when the control

#### Algorithm 1 Thermal Controller

```

T(k): temperature

U_s(k): thermal-control Output

T_R: temperature set point

T_0, T_{\text{idle}}: estimated environment and idle temperature

U_{\text{max}}, U_{\text{min}}: utilization bounds

K_p, K_I, \omega, T_s, \hat{\Phi}, \hat{\Gamma}: controller parameters

1: Compute temperature difference set point \Delta T_R(k) = T_R - \left(\hat{T}_0 + \hat{T}_{idle}\right) \triangleright At the end of

the k^{th} sampling period

2: The linearized temperature is computed by \Delta T_{\rm lin}(k) = T(k) - (\hat{T}_0 + \hat{T}_{\rm idle}) + \Delta \hat{T}(k)

3: e(k) = (\Delta T_R(k) - \Delta T_{lin}(k))

4: u(k) = u(k-1) + K_P(e(k) - e(k-1)) + K_I\left(1 + \frac{\omega_1 T_s}{2}\right) \left(e(k) - \frac{2 - \omega_1 T_s}{2 + \omega_1 T_s}e(k-1)\right)

5: if U_{\min} \leq u(k) \leq U_{\max} then

U_s(k) = u(k)

6:

7: else

if u(k) < U_{\min} then

8:

U_s(k) = U_{\min}

9:

10:

else

U_s(k) = U_{\text{max}}

11:

end if

12:

13: end if

14: \bar{U}(k) = u(k) - U_s(k)

15: \Delta \hat{T}(k+1) = \hat{\Phi} \Delta \hat{T}(k) + \hat{\Gamma} \bar{U}(k)

```

input saturates  $u(k) < U_{\min}$  or  $u(k) > U_{\max}$ , we want to enforce stability of the *active* closed-loop system consisting of K(z) and  $\hat{H}(z)$ , and stability of H(z).

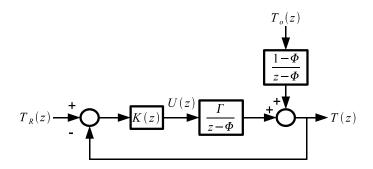

Figure 2.3: Resulting feedback control structure when  $H(z) = \hat{H}(z)$ .

For the first case, as is assumed in [33,38], stability of this system will first be considered for the special case in which  $\hat{H}(z) = H(z)$ . In such case it is straightforward to show that Fig. 2.2 can be drawn in the equivalent form as depicted in Fig. 2.3. The function dead $(u, U_{\min}, U_{\max})$  is implemented as follows:

$$\operatorname{dead}(u, U_{\min}, U_{\max}) = \begin{cases} (u - U_{\min}), & \text{if } u \leq U_{\min} \\ 0, & \text{if } U_{\min} < u < U_{\max} \\ (u - U_{\max}), & \text{otherwise.} \end{cases}$$

The verification of stability of the closed-loop system in Fig. 2.3 is based on the well-know Nyquist stability criteria in frequency domain [75], from which and Fig. 2.3 we obtain Theorem 1 to verify stability of the our proposed control structure (Fig. 2.2) directly.

**Theorem 1.** The closed-loop system depicted in Fig. 2.2 is stable if 1) K(z)H(z) satisfies Nyquist stability criteria; 2)  $\hat{H}(z) = H(z)$ . In addition, if the output  $\Delta T(k)$  is to reach a steady-state output for a given input  $\Delta T_R$ , then  $\hat{H}(z)$  should be stable.

For the second case, to avoid introducing additional terms and complexity, we simply note that when  $\hat{H}(z) = H(z)(1+\Delta(z))$ , Fig. 2.2 can be shown to be in the equivalent form depicted in Fig. 2.4. Therefore, when checking for stability, one should verify whether  $K(z)\hat{H}(z)$  also satisfy the Nyquist stability criteria.

Nyquist stability criteria and Lemma 1 lead us to the following theorem:

Figure 2.4: Equivalent control structure given that  $\hat{H}(z) = (1 + \Delta(z))H(z)$ .

**Theorem 2.** The closed-loop system with controller

$$K(z) = K_P + K_I \left( 1 + \frac{\omega_I T_s}{2} \right) \frac{z - \frac{2 - \omega_I T_s}{2 + \omega_I T_s}}{z - 1}$$

depicted in Fig. 2.2 in which  $\Delta T_R$  is the input, and  $\Delta T_{lin}$  is the output is stable if:

1.

$$\hat{H}(z) = \frac{\hat{\Gamma}}{z - \hat{\Phi}}, \ \hat{\Gamma} \leq \Gamma_{\text{max}}, \ \hat{\Phi} \leq \Phi_{\text{max}}$$

2.

$$K_P = K_I = k_{GM} \frac{1 + \Phi_{\text{max}}}{2\Gamma_{\text{max}}}$$

in which  $k_{GM}=10^{-\frac{GM}{20}},~\Phi_{\max}=\exp(-\frac{T_s}{R_{\text{th}\max}C_{\text{th}}}),~\Gamma_{\max}=k_{p\max}R_{\text{th}\max}(1-\Phi_{\max})~and~\omega_I=\frac{2(1-\Phi_{\max})}{T_s(1+\Phi_{\max})}.$  where GM is the desired worst-case gain margin and ,  $0\leq GM<\infty$ .

*Proof.* We show a brief proof of Theorem 2. Let us first consider the case of the closed loop only with K(z) and H(z). The plant-controller loop-product can now be written in the following form:

$$K(z)H(z) = \frac{K_{\rm P}\Gamma}{z - \Phi} + K_{\rm I}\left(1 + \frac{\omega_{\rm I}T_s}{2}\right) \frac{z - \Phi_{\rm max}}{z - \Phi} \frac{\Gamma}{z - 1}.$$

(2.8)

The models of (2.8) and (2.5) indicate that no poles exist outside the unit circle for all  $T_s < \infty$ ; therefore, Lemma 1 will always be satisfied if

$$|K(e^{j\pi})H(e^{j\pi})| \leq 1, \text{ and } \Phi_{\max} = \exp(-\frac{T_s}{R_{\mathsf{th}\max}C_{\mathsf{th}}}) \geq \Phi.$$

These two conditions are sufficient that the phase margin will be greater than zero when  $\omega = \pi$ . In particular we note that if we assume that  $\omega_{\rm I} = \frac{2(1-\Phi_{\rm max})}{T_s(1+\Phi_{\rm max})}$  then by cross multiplication  $\Phi_{\rm max} = \frac{2-\omega_{\rm I}T_s}{2+\omega_{\rm I}T_s}$ . Therefore, our proposed controller has the following form

$$K(z) = K_{\rm P} + K_{\rm I} \frac{2}{1 + \Phi_{\rm max}} \left( \frac{z - \Phi_{\rm max}}{z - 1} \right)$$

so that

$$K(z)H(z) = \frac{K_{\rm P}\Gamma}{z - \Phi} + \frac{2K_{\rm I}}{1 + \Phi_{\rm max}} \frac{(z - \Phi_{\rm max})\Gamma}{(z - \Phi)(z - 1)} = \left(\frac{\Gamma}{1 + \Phi_{\rm max}}\right) \frac{z - \frac{K_{\rm P}(1 + \Phi_{\rm max}) + \Phi_{\rm max}2K_{\rm I}}{K_{\rm P}(1 + \Phi_{\rm max}) + 2K_{\rm I}}}{(z - 1)(z - \Phi)}$$

(2.9)

from the corresponding pole-zero plot, it is evident that the magnitude  $|K(e^{j\omega})H(e^{j\omega})|$  is a smoothly decreasing function in which the phase  $\angle K(e^{j\omega})H(e^{j\omega}) > -\pi$  for  $\omega \in [0,\pi)$  if

$$\Phi < \frac{K_{\rm P}(1 + \Phi_{\rm max}) + \Phi_{\rm max}2K_{\rm I}}{K_{\rm P}(1 + \Phi_{\rm max}) + 2K_{\rm I}} < 1 \text{ holds.}$$

Indeed, the above inequality will be shown to hold if  $\Phi_{\text{max}} > \Phi$ . It is therefore sufficient to let the magnitude of  $|K(e^{j\pi})H(e^{j\pi})| < 1$  or the magnitude of the respective proportional term (involving  $K_{\text{P}}$ ) and integral term (involving  $K_{\text{I}}$ ) to each be less than one-half when  $\omega = \pi$  and can indeed be readily verified from our first expression given for K(z)H(z), and carefully noting the relationship between the ratio involving  $\Phi$  and  $\Gamma$  in which

$$\frac{K_{\rm P}}{k_{\rm GM}} < \frac{|e^{j\pi} - \Phi|}{2\Gamma} \le \frac{1 + \Phi_{\rm max}}{2\Gamma_{\rm max}}, \frac{K_{\rm I}}{k_{\rm GM}} < \frac{1 + \Phi_{\rm max}}{4\Gamma} \frac{|(e^{j\pi} - \Phi)(e^{j\pi} - 1)|}{|e^{j\pi} - \Phi_{\rm max}|} \le \frac{1 + \Phi_{\rm max}}{2\Gamma_{\rm max}}.$$

We will always know what  $U_{\text{max}}$  will be as it is dictated by the scheduler chosen, however, some uncertainty may remain on choosing the lower-limit  $U_{\text{min}}$  due to task execution time. Therefore even choosing the ultimate lower-bound  $U_{\text{min}} = 0$  can always be a safe choice even if  $U_{\text{min}} > 0$  in that it will result in a slight sub-optimal lag in allowing the controller to increase the utilization levels due to a decrease in environmental temperature for example. Considering that environmental temperature changes are fairly slow, this slight lag is typically unnoticeable. For a more detailed discussion on anti-windup control, we refer the reader to [33,38].

The Theorem 2 reveals the appealing feature of our thermal controller, that is, its robustness under power change and thermal fault can be guaranteed analytically. Since  $k_p$  involves uncertainty of power change represented by  $G_p$  according its definition,  $k_p = (G_p P_a - P_{\text{idle}})$ ,  $k_{p \,\text{max}}$  corresponds to the maximum actual power changes that TCUB can cancel. For example, if  $k_{p \,\text{max}} = 510$ ,  $P_a = 51.9W$  and  $P_{\text{idle}} = 13.3W$ , we can calculate that the upper limit of  $G_p$  is 10.11, that is, even if the actual power is 10.11 times by the estimated power, the thermal controller still can stabilize the system. Similarly, the capability of TCUB to handle thermal fault (modeled by increased thermal resistance) is represented by  $R_{\text{th max}}$ . Note that the Theorem 2 not only provides robustness guarantee but also design of the anti-windup controller.

Moreover, another appealing property is isolation of varied ambient temperature in our thermal controller. This property is provided by Lemma 1.

**Lemma 1.** If the processor's temperature converges, it converges to the temperature set point even the estimated ambient temperature,  $\hat{T}_o$ , and idle temperature  $\hat{T}_{idle}$  are employed.

Proof. The proof is straightforward. it is obvious that for the steady-state case when the  $u(k) = U_s(k)$  that  $\Delta T_R(k) = \Delta T_{\text{lin}}(k) = \Delta T_{\text{fb}}(k)$  due to the integrator term in K(z). Therefore, from the following equation,  $\Delta T_R = T_R - (\hat{T}_o + \hat{T}_{\text{idle}}) = T(k) - (\hat{T}_o + \hat{T}_{\text{idle}}) = \Delta T_{\text{fb}}(k)$ , we have  $T_R = T(k)$ , that is, the processor's temperature converges to the temperature set point.

It is noted that due to the minimum task rate constraints, there exists a lower bound for the feasible utilization, which in turn results in a lower bound for the feasible temperature. The lower bounds for the utilization and temperature are related to the rate constraints, the actual execution times, and the actual power consumption. TCUB can achieve satisfactory thermal and real-time performance only if both the given temperature set-point and the utilization bound are feasible under the task rate constraints.

## 2.5.4 Sensitivity Analysis

In the preceding analysis we provided necessary and sufficient conditions for stability assuming that environmental temperature  $T_o$  and idle power  $P_{\text{idle}}$  (corresponding idle temperature  $T_{\text{idle}}$ ) remained constant. For simplicity of discussion, we will: i) further assume that idle power is constant and equal to zero<sup>2</sup>; ii) we will treat environmental temperature  $T_o(k) \neq T_o(k+1)$  as a disturbance with the respective z-transform  $T_o(z)$ ; iii) assume that saturation does not occur; iv)  $\hat{T}_o = 0$ , therefore  $\Delta T_R(k) = T_R(k)$ . Since  $T_{\text{idle}} = 0$  then  $\Delta T(k) = T(k) - T_o(k)$  as a result it is a straight forward exercise to show from (2.5) and (2.7) that:

$$\Delta T(z) = \frac{\Gamma}{z - \Phi} U(z) - \frac{z - 1}{z - \Phi} T_o(z), T(z) = \frac{\Gamma}{z - \Phi} U(z) + \frac{1 - \Phi}{z - \Phi} T_o(z). \tag{2.10}$$

Using (2.5.4) we state Lemma 2.

**Lemma 2.** For the control system depicted in Fig. 2.1 in which  $u(k) = U_s(k)$ ,  $T_R(z) = 0$  the sensitivity transfer function S(z) is  $S(z) = \frac{T(z)}{T_o(z)} = \frac{1-\Phi}{z-\Phi+\Gamma K(z)}$ . Furthermore stability is unaffected when  $T_o(k+1) \neq T_o(k)$  and  $P_{\text{idle}}(k+1) \neq P_{\text{idle}}(k)$ .

Figure 2.5: Closed-Loop structure when studying sensitivity.

*Proof.* Fig. 2.5 depicts (2.5.4) and our proposed control structure when saturation is not present. Therefore, using standard closed loop realizations we can show that

$$T(z) = \frac{\Gamma K(z)}{z - \Phi + \Gamma K(z)} T_R(z) + \frac{1 - \Phi}{z - \Phi + \Gamma K(z)} T_o(z)$$

<sup>&</sup>lt;sup>2</sup>Constant idle power has no effect on the sensitive function shown in Lemma 2.

then setting  $T_R(z) = 0$  results in the standard sensitivity transfer function  $S(z) = \frac{1-\Phi}{z-\Phi+\Gamma K(z)}$ . Note also that the sensitivity function has the same characteristic equation as the closed-loop system  $(\frac{\Gamma K(z)}{z-\Phi+\Gamma K(z)})$  studied for closed-loop stability. Therefore it is obvious that dynamic effects related to environmental temperature  $T_o$  have no effect on stability. An analogous observation can be made if idle power is considered to be time-varying.

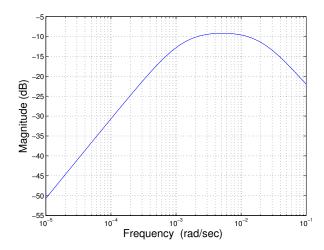

For an example system with parameters from Tab. 2.1 and Tab. 2.2, Fig. 2.6 plots the magnitude of the sensitivity transfer function of the system with respect to frequency. Note that in the whole range of frequency the magnitude is less than 0, which means the effect of  $T_o$  converges to 0 in steady state and can not affect the temperature of closed loop system.

Figure 2.6: Magnitude of sensitivity transfer function of the example system.

# 2.6 Evaluation

The simulation environment consists of two components: an event driven simulator implemented in C++ and a Simulink<sup>©</sup> model implemented in MATLAB (R2008a). The simulator simulates a single processor real-time system controlled by TCUB and implements a utilization monitor, a rate actuator and a utilization controller. The Simulink<sup>©</sup> component implements the thermal controller and models thermal dynamics of the processor. The simulator and the Simulink<sup>©</sup> component communicate with each other through a TCP connection.

In our simulation, the tasks set running on the processor consists of 10 periodic soft real-time tasks. The Rate Monotonic (RM) scheduling algorithm [56] is employed to schedule all tasks. Initially, the period of each task  $T_i$  is randomly generated in the range [100ms, 200ms]. Based on the initial tasks rate, the execution times of tasks are deliberately chosen in such a way that the CPU utilization of each task are almost equal and the CPU utilization of all tasks is lower than schedulable CPU utilization bound. The minimum rate of one task equals its execution time while the maximum rate equals 10 times of initial tasks rate. The deadline of each task equals its period.

The processor simulated in our work is a 2.6GHz Pentium 4 (P4) processor with 130nm Northwood core. All thermal related parameters except thermal capacitance shown in Table 2.1 are based on Intel technical specification [44]. The thermal capacitance is acquired based on the parameters used for simulating P4 on Hotspot [41], a widely used architecture level simulator,.

| Parameter                | Notation      | Value         |

|--------------------------|---------------|---------------|

| Ambient temperature      | $T_o$         | $45^{\circ}C$ |

| Max case temperature     | $T_c$         | $75^{\circ}C$ |

| Estimated Active power   | $P_a$         | 51.9W         |

| $Idle power^*$           | $P_{i}$       | 13.3W         |

| Thermal Capacitance      | $C_{\sf th}$  | 295.7J/K      |

| Thermal Resistance       | $R_{\sf th}$  | 0.467K/W      |

| Thermal Fault Resistance | $R_{\sf th}'$ | $2R_{th}$     |

<sup>\*</sup> Enhanced Halt Mode is available [86]

Table 2.1: Power and thermal parameters of simulated processor.

In the following simulations, we choose  $70^{\circ}C$  as the set point of the processor's temperature. The set point is lower than the maximum case temperature  $75^{\circ}C$  to avoid activation of interal hardware regulation which ends up unpredictable performance degradation. The thermal fault resistance,  $R'_{th}$ , is based on the data reported in [23].

Table 2.2 shows the controller parameters of TCUB which are calculated using the methods discussed in Section 2.5.

| $K_p$  | $K_i$  | $\omega_i$ | $k_{p \max}$ | $R_{th\mathrm{max}}$ | $U_{\rm max}$ | $U_{\min}$ | $T_R$          | $T_s$ | $K_p$ | $T_u$ |

|--------|--------|------------|--------------|----------------------|---------------|------------|----------------|-------|-------|-------|

| 0.0523 | 0.0523 | 0.0036     | 510          | 0.934                | 0.67          | 0.07       | $70~^{\circ}C$ | 10s   | 0.37  | 1s    |

Table 2.2: TCUB controller parameters

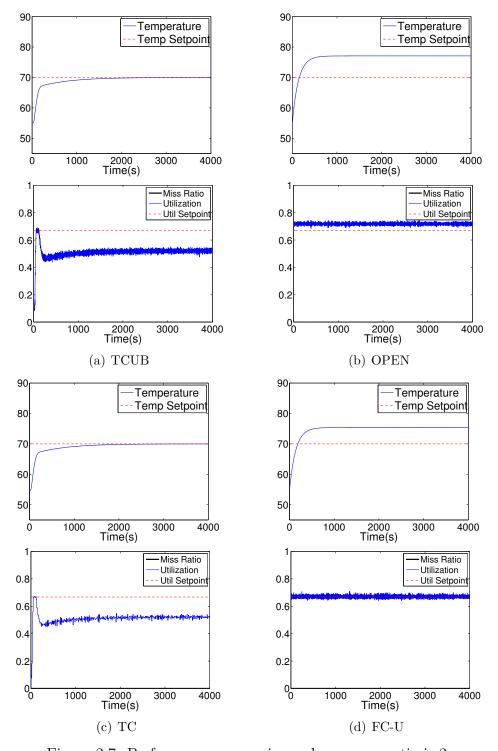

We compare TCUB against three baseline algorithms<sup>3</sup>, OPEN, TC and FC-U. OPEN has no feedback thermal and utilization control loop and statically set task rates based on the *estimated* execution times to achieve the schedulable utilization bound. OPEN represents a static approach commonly used in practice. TC has the same thermal controller as TCUB, but does not include the utilization controller. After the thermal controller outputs the utilization set point, it sets the task rates based on the *estimated* execution times. FC-U [60] is the same utilization control algorithm used in TCUB, but does not has the thermal controller to manage temperature. As subsets of TCUB, TC and FC-U allow us to evaluate the effectiveness of the *integrated* control approach of TCUB for both temperature and utilization.

#### 2.6.1 Power Deviation

This set of simulations is designed to evaluate TCUB when the processor's active power deviates from the estimate, which represents power phase change observed in previous empirical studies [46]. We use different power ratios, i.e., the ratio between the actual active power to the estimate, in different runs. In the first run the power ratio is 2, i.e., the actual active power is twice the estimate; in the second run, the power ratio is 0.5, i.e., the actual power is half of the estimate. The task execution times are the same as their estimate in this set of experiments.

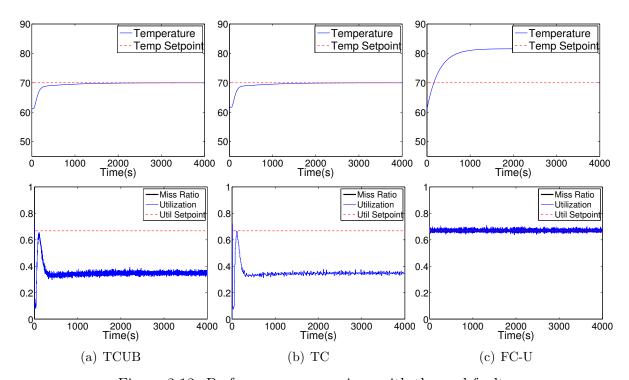

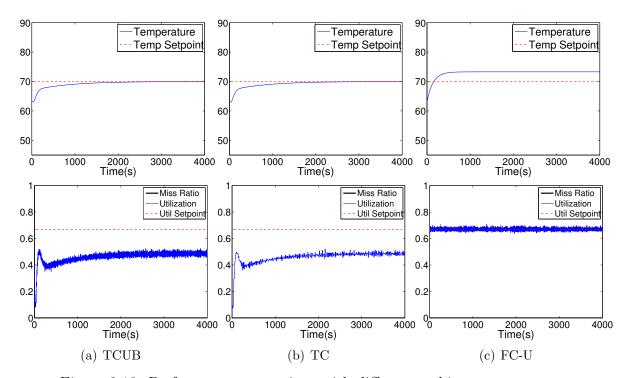

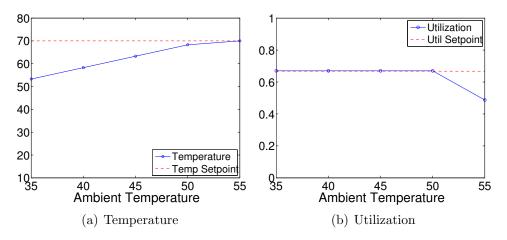

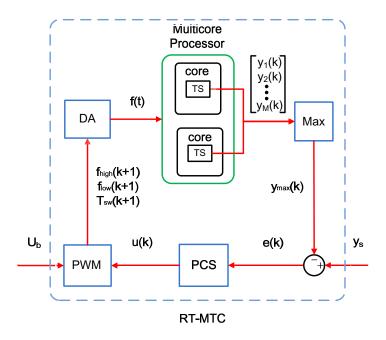

Fig. 2.7 shows the results when power ratio is 2. As shown in Fig. 2.7(a), the temperature of the processor under TCUB converges to the temperature set point  $70^{\circ}C$  while its utilization remains below the utilization bound. Note that TCUB forces the CPU utilization to remain lower than its utilization bound, which is needed in order to maintain the temperature set